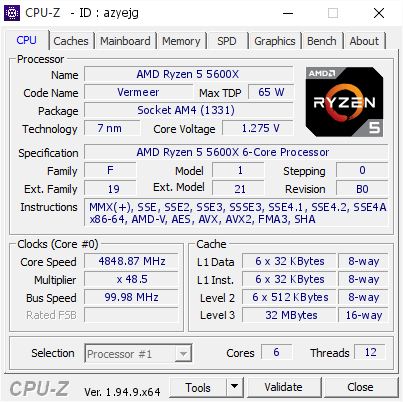

OK, to be more precise: usually it´s IO-Die = IOD that can´t handle it. If WHEA up to IOD 1,050V @ IF 1900, no WHEA beyond 1,055V @ IF 1900, while always WHEA at IF 1933+: I think you can very well simplify that to "IOD can´t handle it".

IOD mostly relates to GMI (and xGMI)

That mostly relates towards the chipset and the board peripheral.

// may or may not relate to CCD to CCD communication, but i'm not confident enough on that.

// VDDG CCD should branch on that part rather and take over part of L$. CPU1P8 likely does too, but not sure here;

But IOD issues for VDDG, mostly relate to (here especially different on AM5), to SOC and procODT issues.

VDDG itself is dynamic and loadbalanced. Supply between CCD & IOD herby is dynamic based on the input you give.

The input you give has a delta it requires based on if single-CCD or dual CCD. How much SOC that substrate requires.

// this is familiar to Matisse, Vermeer is the same just the substrate is more tolerable and can work with weaker procODT + lower voltages, X3D especially.

Pushing VDDG higher while might increase "relation of need", like the priority of voltage taking vs CCD section

But its only a VID.

Supply comes from SOC and supply strength to sample leakage (unique per sample, same SKU) is the outcome of thermal, socket vendor (should be standardized now) and SOC voltage itself

Those influence "requirement of voltage to reach X"

Stronger procODT (which they can take) , stronger effect of voltage and 1.8v CPU1P8 supply rail.

Soo herby lower VDDG and lower SOC.

Dynamic variables, nothing goes alone

IOD includes IMC, and because of 1:1:1 for FCLK / UCLK / MCLK the IO-Die is clocked to it´s limits.

For the IMC, you neither need SOC nor VDDG.

Sorry, i dont think this is correct.

IMC supply and upkeep voltage on AM4 is solely cLDO_VDDP

There is a VDDP_CPU supply that crosssections APUs too - soo it might! unclear, have an effect for GMIs

But no, UCLK itself which is main IMC clock (multi stage) ~ has no connection to SOC or to VDDG.

// GMI, LCLK & FCLK usually are dynamic on our samples ~ even if sillyheads AMD engineer stopped using dynamic FCLK+dynamic SOC (V) on frontend and hate to talk about this

// Its a difficult topic i get it, but wasting 25A vs 5A on idle ~ times SOC voltage soo about 35W vs 8-12W , i dont know. Such a silly waste of resources and efficiency

procODT and CPU1P8 does influence it

But those are side product influences. A "side-issue".

Once you set FCLK, only your sample strain towards general impedance (procODT) and your IMC tollerances to cLDO_VDDP

Are what define your maximum MCLK

VDDG & SOC need zero touch.

ProcODT for MemOC generally needs no touch, but its an old community habbit;

EDIT:

Soo based on this mess, you later define your ODTs that send the signal to mem

And your RTTs that amplify and do gate for their target need (chipselect, rankselect and so on)

EDIT2:

Technically speaking, LDO's are not an"input supply" either but an upkeep gated dropout regulator

Ah its fine, should be understandable nevertheless. 🤭

But all VIDs are priority loadbalanced. They are very far away from constant supply.

tho I hope you stop trying to stop us from still giving pragmatic, step-by-step advice and sharing experiences

I dont have anything negative , bad or forceive in my mind or actions. Zero

All emotes are neither passive nor active aggressive. Absolutely zero.

If i write them i mean it ~ very happy right now to be honest

I just wish that , how do i phrase it

I just wish that LUXX delivers better.

You guys have much more accurate research and germans generally are known for perfectionism

I want to hold you to that ~ but will never force this onto somebody

Selective (random) people i try to help, i want them "to not give up" even if its difficult and confusing due to lack of documentations;

Thats about all. It doesnt need to be first place or anything. If person learns and shares that knowledge further, pulling other people up ~ im happy

I hope thats understandable

, soo that means you have to work even harder~~

, soo that means you have to work even harder~~

Ja eh nur 1-2 am Tag. Aber die eben schon. Kommt nicht in Frage für mich.

Ja eh nur 1-2 am Tag. Aber die eben schon. Kommt nicht in Frage für mich.