Werbung

Kurz nachdem man sich bei AMD dazu entschlossen hatte, mit der Polaris-Architektur auf den Mittelklasse- und Mobile-Markt abzuzielen, folgte die Entscheidung mit einer parallelen Architektur-Entwicklung andere Märkte in den Fokus zu nehmen. Auch wenn AMD in den vergangenen Monaten immer wieder neue FirePro-Grafikkarten auf den Markt brachte, so schien man den Trend zum Machine Learning, Deep Learning, Artificial Intelligence etwas verschlafen zu haben – auch weil die verfügbaren GPUs aufgrund ihrer Architektur in diesem Bereich nicht ihre Stärken hatte. Mit der Vega-Architektur soll diese Lücke nun geschlossen werden. Heute gibt AMD einen ersten Einblick auf das, was uns 2017 erwartet.

Zum jetzigen Zeitpunkt dürfen wir etwas genauer über das sprechen, was wir schon Mitte Dezember im Rahmen der Vorstellung von Radeon Instinct zumindest an der Oberfläche ankratzen konnten. Schon damals wurden einige Details zu Vega bekannt, wenngleich AMD offiziell noch nichts sagen wollte.

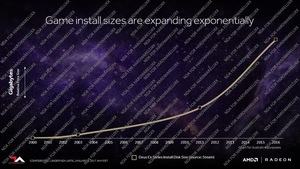

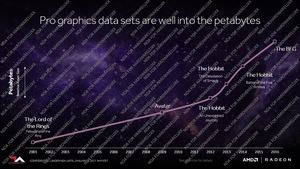

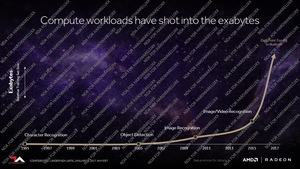

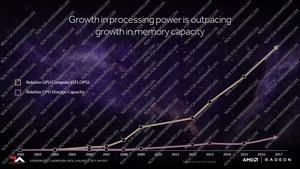

Bei der Entwicklung der Vega-Architektur wollte AMD diese auf die aktuellen Anforderungen auslegen und das nicht nur hinsichtlich der Rohleistung der Shadereinheiten, sondern auch die dazugehörige (Speicher)-Infrastruktur. Dass der Speicher ein immer wichtigerer Faktor wird, zeigt die Entwicklung von High Bandwidth Memory, GDDR5X und weiteren Stapelspeichertechnologien wie 3D XPoint bei Intel und HMC bei Micron. In Spielen werden inzwischen einige Gigabyte an Daten in den Speicher geschrieben und wieder von dort gelesen. Bei der Verarbeitung von Video-Inhalten sind wir inzwischen bei mehreren Petabyte angekommen. Schaut man aber in den Compute-Bereich und diesen will AMD mit der Vega-Architektur ansprechen, sind mehrere Exabyte keine Seltenheit mehr. Das auseinanderlaufende Verhältnis zwischen Rechenleistung und der zur Verfügung stehenden Speichermenge sowie dessen Anbindung will AMD wieder in ein sinnvolles Verhältnis rücken.

[h3]Neue Speicherarchitektur[/h3]

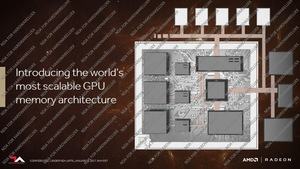

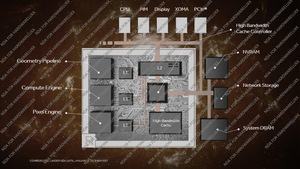

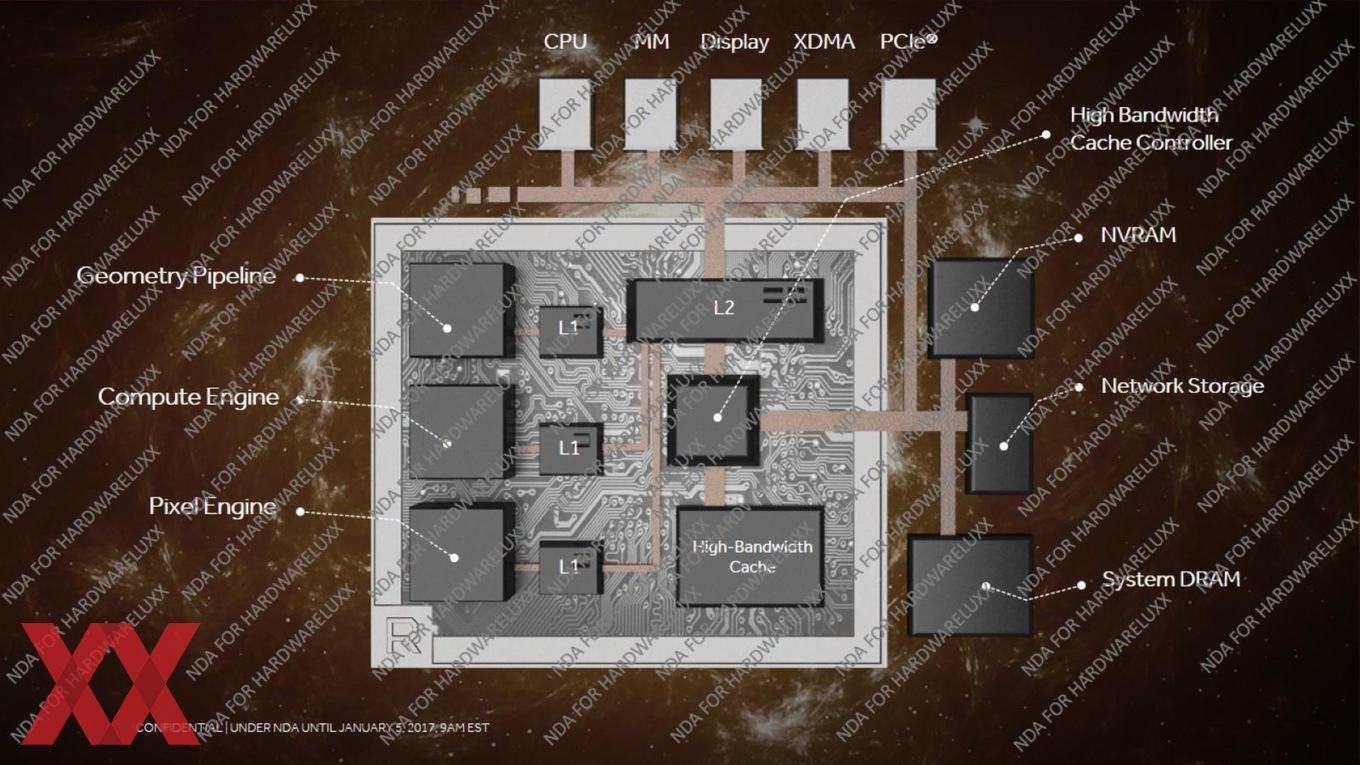

Im Rahmen der ersten Vorstellung der Vega-Architektur wollen wir auch mit der Betrachtung der neuen Speicherarchitektur beginnen. Ein wichtiger Bestandteil ist dabei der High-Bandwidth Cache. So bezeichnet AMD den für die GPU verfügbaren Speicher. Dabei handelt es sich nicht nur um den Grafikspeicher, sondern um allen der GPU zur Verfügung stehenden Speicher, einschließlich Caches. Dabei spielt es auch keine Rolle, ob es sich beim Speicher um GDDR5, GDDR5X oder HBM der 1. oder 2. Generation handelt.

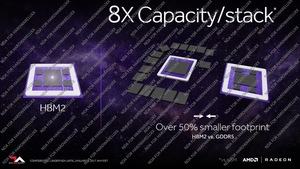

Der Vorteil der neuen Speichertechnologien wie HBM2 liegt auf der Hand. Die Speicherbandbreit kann auf bis zu 1.024 GB/s und damit verdoppelt werden. Die zur Verfügung stehende Kapazität kann bis zu 32 GB in vier Stacks zu jeweils 8 GB betragen.

[h2]HBM2 ermöglicht flexible Speicherausstattung[/h2]

Bisher kennen wir den High Bandwidth Memory im Desktop-Bereich nur von der Radeon R9 Fury X. Dort kommt dieser Speicher jedoch in seiner ersten Generation zum Einsatz. AMD verwendet im GPU-Package vier HBM-Speicherstacks mit einer Kapazität von jeweils 1 GB und einer Speicherbandbreite von jeweils 128 GB/s. Der Takt des Speichers liegt bei 500 MHz und somit ergeben sich daraus die insgesamt 4 GB Grafikspeicher und 512 GB/s.

NVIDIA präsentierte im letzten Frühjahr den GPU-Beschleuniger Tesla P100 und dieser ist nach wie vor der einzige seiner Art, der HBM der zweiten Generation verwendet. Auch hier werden vier Speicherstacks verwendet, die allerdings auf jeweils 4 GB Speicherkapazität und auf 180 GB/s kommen. Insgesamt ergeben sich daraus die 16 GB Gesamtspeicher auf der Tesla P100, der mit 720 GB/s angebunden ist. bei HBM2 kann der Takt theoretisch verdoppelt werden, sodass 256 GB/s pro Speicherstack erreicht werden, allerdings verwendet NVIDIA für die Tesla P100 vermutlich noch Speicher aus der Risikoproduktion von Samsung, der diese Taktraten noch nicht erreichen konnte.

Doch HBM2 soll im Unterschied zu HBM1 deutlich flexibler sein, was den Speicherausbau betrifft. Spezifiziert ist HBM2 in Speicherstacks zu 2 (2Hi HBM2), 4 (4Hi HBM2), 8 GB (8Hi HBM2) sowie 16 GB (16Hi HBM2). Bisher haben SK Hynix und Samsung als Hersteller von HBM2 aber nur bis zu 8Hi HBM2 in der Produktion vorgesehen. 16Hi HBM2 sind allerdings bereits spezifiziert und damit theoretisch umsetzbar. Je nachdem, wie viele Speicherstacks nun zum Einsatz kommen, kann der Speicherausbau und dessen Anbindung unterschiedlich ausgeführt werden.

Einige Vorteile des High Bandwidth Memory kennen wir bereits von der 1. Generation, die auf der Radeon R9 Fury X zum Einsatz kommt. Hier liegt die Speicherbandbreite mit 512 GB/s zwar auch schon auf einem recht hohen Niveau, schon damals war es aber wichtig festzuhalten, dass der HBM1 um den Faktor zwei effizienter weil sparsamer bei der Leistungsaufnahme ist. Hinzu kommt, dass der High Bandwidth Memory auf einem Interposer direkt neben der GPU und damit im GPU-Package platziert wird. Damit nimmt der Speicher auch deutlich weniger Platz auf dem PCB sein.

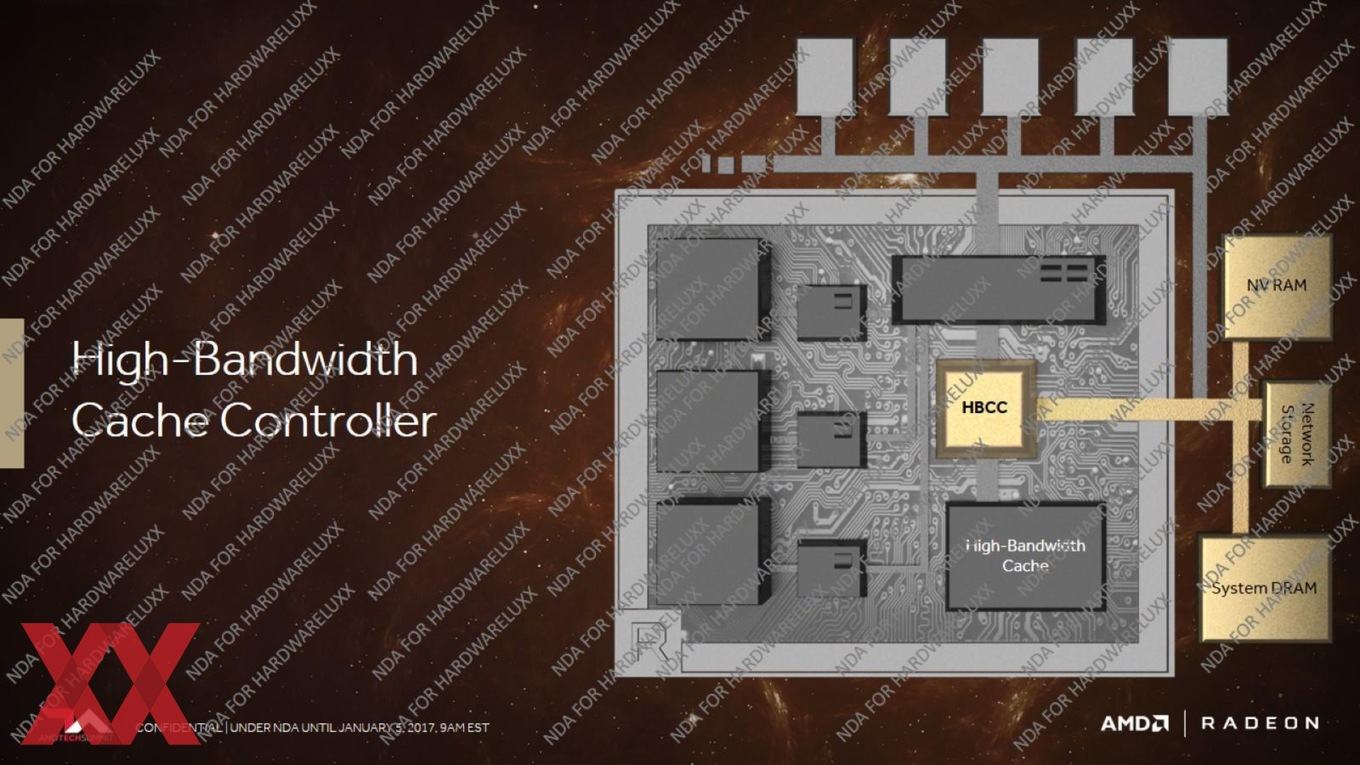

Immer mehr DRAM zu verwenden konnte die aktuellen Limitierungen also nicht mehr aufheben. Außerdem steigen der PCB Footprint und die Leistungsaufnahme. Ein heterogenes Speichermanagement soll die notwendige Flexibilität bieten. Dazu hat AMD den HBCC (High-Bandwidth Cache Controller) entwickelt. Dieser kümmert sich um die Ansteuerung und Verwaltung der verschiedenen Speichertechnologien.

Neben der reinen Größe und Geschwindigkeit des Speichers gibt es noch viele andere Punkte, an denen die Effizienz des Gesamtsystems verbessert werden kann. So ist es nicht notwendig alle Daten im schnellsten Speicher vorzuhalten, denn die GPU kann nur einen bestimmten Datensatz gleichzeitig verarbeiten. Das Datamanagement verschiebt sich von den Spieleentwicklern hin zu AMD bzw. der Architektur selbst. Bisher verwenden die Entwickler allen Speicher, den sie zur Verfügung gestellt bekommen. Die Kontrolle darüber haben sie selbst. Allerdings kostet eine gute und effiziente Anpassung viel Zeit und damit auch Geld.

Die Radeon Pro SSC mit einer SSD war in diesem Segment ein erster Schritt in die Richtung, der mit der Vega-Architektur nun vollständig vollzogen wird. Verschiedene Speicher werden kombiniert, die Hardware übernimmt weitestgehend die Zuteilung und sorgt für eine effiziente Nutzung.

Im Rahmen dieser Umstellung werden wir uns aber auch an neue Begriffe und Funktionsprinzipien gewöhnen müssen. Der Grafikspeicher oder richtiger Frame Buffer wird von AMD nur noch als High-Bandwidth Cache bezeichnet. Angesprochen wird dieser vom neuen High Bandwidth Cache Controller (HBCC), der neben dem HB Cache auch angebundenen Network Storage und System DRAM verwalten kann. Insgesamt kann der HBCC 512 TB an virtuellem Adressraum verwalten. 49 Bit können als Shared Memory auf alle GPUs in einem System verteilt werden. Dazu werden Speicherpools angelegt. 256 TB kann ein einzelner physikalischer Speicher theoretisch groß werden. Der HBCC entscheidet, welche Daten im schnellen Speicher und welche Daten im langsamen Speicher landen. Gesteuert wird dies über den Treiber (siehe Speichermanagement bei Fiji). Zugriffe auf die Daten im Speicher sollen optimiert werden, denn nur etwa die Hälfte der Daten, die sich im Frame Buffer befinden, werden überhaupt verwendet.

Wie ineffizient ein Speicher trotz vieler Optimierungen verwendet wird, zeigt folgendes Beispiel: In einer beispielhaft ausgesuchten Spielszene in Deus Ex: Mankind Devided sind 210 Millionen Polygonevorhanden, davon aber nur 2 Millionen davon sind sichtbar.

Unklar ist noch, wie das neue Speichermanagement genauer aussieht. Ab wann der Treiber die Kontroller übernimmt und wie viel Einfluss die Programmierer darauf haben. Mit DirectX 12 sollte die Kontrolle des Speichers eigentlich weiter in die Hände der Entwickler überführt werden. AMD und NVIDIA übernehmen über die Treiber aber weiterhin eigene Optimierungen, die auf die Hardware angepasst sind.

[h3]Neue Geometry Pipeline[/h3]

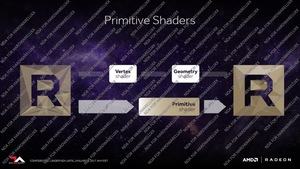

Neben dem Speicher hat AMD in der Vega-Architektur aber noch weitere Änderungen vorgenommen und diese betreffen die Geometry Pipeline. Diese soll einen doppelt so hohen Pixeldurchsatz pro Takt im Vergleich zu den bisherigen Architektur aus dem Hause AMD ermöglichen.

An dieser Stelle ein kleiner Exkurs durch die GPU-Architekturen bei AMD. AMD bezeichnet seine Architekturen und Instruction Sets in den vergangenen Jahren mit dem Namen Graphics Core Next (GCN). Den Anfang machte AMD mit der 1. Generation in der Radeon-HD-7700-Serie. Intern wurde diese Architektur auch als GFX7 bezeichnet. Allerdings gibt es Überschneidungen zwischen den GCN-Generationen und den Architekturbezeichnungen bei AMD. Mit GCN 2.0 und GCN 3.0 bzw. GFX8 wurden die darauffolgenden Generationen bezeichnet – bis hin zu den im letzten Sommer vorgestellten Polaris-Karten, die mit GCN 4.0 bezeichnet werden.

Die weitgehenden Änderungen bei der Vega-Architektur rechtfertigen wohl auch eine neue interne Bezeichnung bei den Architekturen. Die Vega-Architektur wird daher auch mit GFX9 benannt. Vega 10 und Vega 11 bleiben dem grundsätzlichen Design der GCN-Architekturen treu.

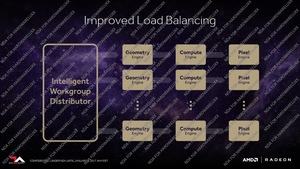

Neu innerhalb der Geometry Pipeline ist, dass Vertex Shader und Geometry Shader nicht mehr getrennt voneinander behandelt werden. Stattdessen können sogenannte Primitive Shader eingesetzt werden. Diese beinhalten Vertex- und Geometry-Berechnungen, lassen sich über einen verbesserten Load Balancer aber besser auf die zur Verfügung stehenden Hardware-Ressourcen verteilen. Damit sollen die Shadereinheiten auch besser ausgelastet werden. Die GPU überwacht sich bzw. die Auslastung ständig selbst und versucht die ideale Verteilung zu erreichen.

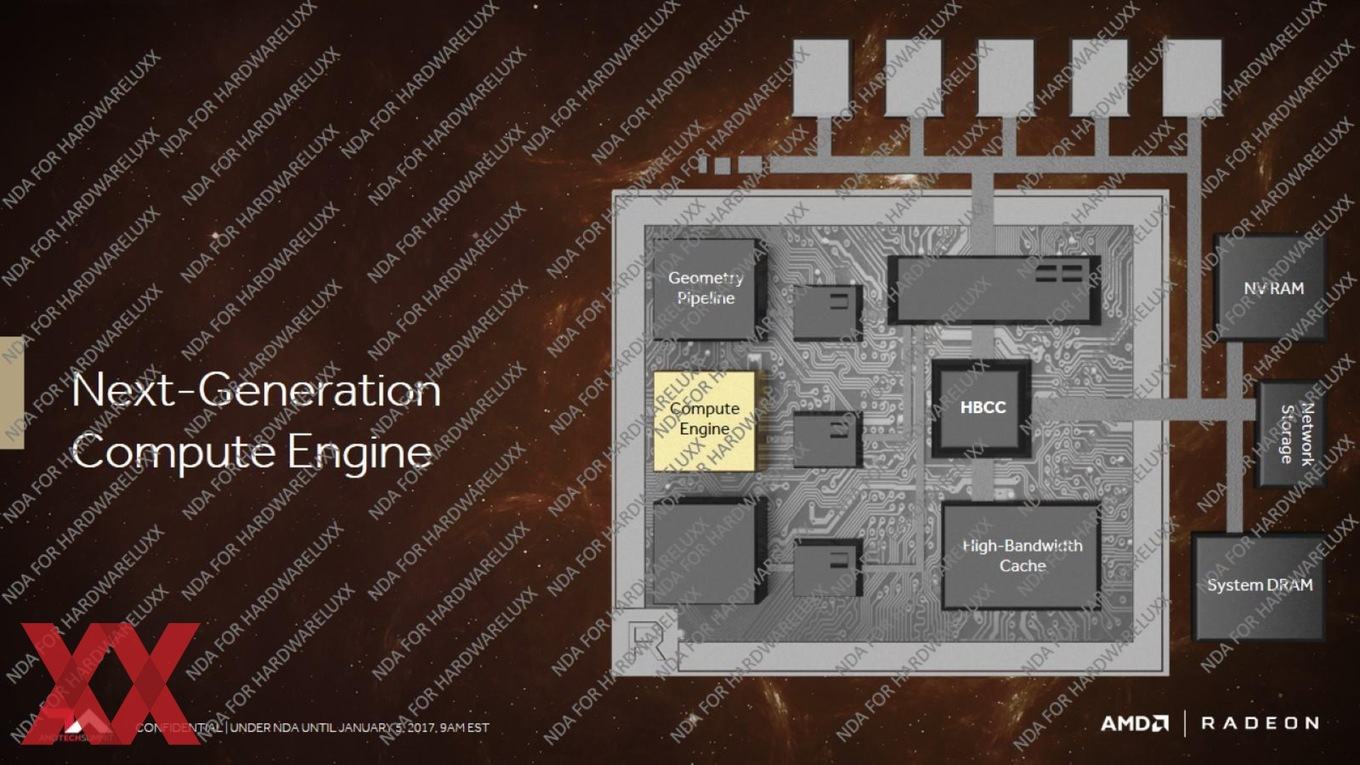

[h3]Neue Compute Engine[/h3]

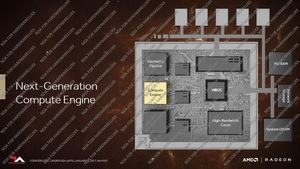

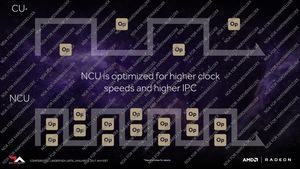

Dritter wichtiger Bestandteil der neuen Architektur ist die neue Compute Engine und auch hier gibt es weitgehende Änderungen im Vergleich zur bisherigen Architektur. Im Rahmen der neuen Compute Engine wird auch der bereits im Dezember gefallene Begriff NCU genauer erläutert. NCU steht wie von uns vermutet für Next-Generation Compute Engine.

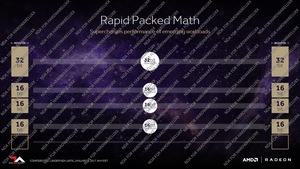

Diese neue Compute Engine kann 512 8-Bit Operationen pro Takt, 256 16-Bit Operationen pro Takt und 128 32-Bit Operationen pro Takt ausführen. Damit kommt die Vega-Architktur auf ein 4:2:1-Verhältnis für diese Datentypen und liegt wieder auf Niveau der Hawaii-GPUs. Das Double-Precision-Verhältnis ist anpassbar. AMD setzt dabei auch auf eine Technologie, die wir von NVIDIA als Mixed Precision kennen. Dabei können 32 Bit Register mit den dazugehörigen 32 Bit Operationen in 2x 16 Bit Register mit 2x 16 Bit Operationen aufgeteilt werden. Dies ist der wesentliche Schritt, um hinsichtlich der Leistung für Machine-Learning-Anwendungen wieder mithalten zu können. Durch andere Optimierunge sollen die NCU auch eine höhere Single-Threaded-Leistung vorzuweisen haben.

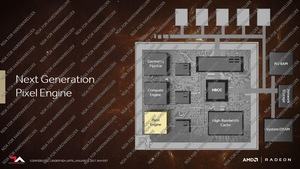

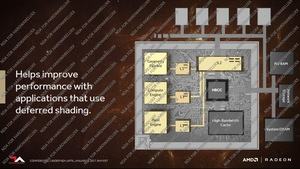

[h3]Neue Pixel Engine[/h3]

Änderungen hat es auch bei der Pixel Engine gegeben. Diese kann nun neue sogenannte Draw Stream Binning Rasterizer ausführen, die für eine bessere Kompression der vorhandenen Daten sorgen. Damit soll der Speicherbedarf reduziert werden, was bei der Übertragung dieser Daten aus und in den Speicher auch Vorteile bei der Geschwindigkeit birgt. In einer Szene wird jedes Objekt nacheinander berechnet, dies alles muss durch den Rasterizer – ob sichtbar oder nicht spielt dabei zunächst einmal keine Rolle. Durch den Draw Stream Binning Rasterizer können Pixel entfernt werden, die nicht sichtbar sind. Ein Shading ist in diesem Fall nicht mehr notwendig. Dadurch wird Speicherkapazität und Speicherbandbreite eingespart. In bisherigen GPU-Architekturen von AMD ist der Pixel- und Texturspeicher nicht coherent ausgelegt und musste daher teilweise doppelt verwendet werden. Mit der Vega-Architektur nutzen die Geometry Pipeline, die Compute Engine und die Pixel Engine den zur Verfügung stehenden L1- und L2-Cache parallel. Dies gilt auch für die Render Backends.

Die immer komplexere Fertigung mit mehr und mehr Transistoren stellt für AMD natürlich auch eine Herausforderung dar. Die Leistung muss ebenso steigen wie die Effizienz. Einiges davon kann durch eine verbesserte Fertigung erreicht werden, ein Großteil der aber über eine verbesserte Architektur. Dazu trägt bei Vega unter anderem die neue Speicherhierarchie bei, aber auch die neuen Entwicklungen bei der Compute und Pixel Engine. Ein Ergebnis dieser Entwicklung, die vor vier Jahren startete, ist der Infinity Fabric.

[h3]Infinity Fabric[/h3]

Bei den Zen- bzw. RYZEN-Prozessoren tauchte immer wieder der Begriff Infinity Fabric oder Infinity Control Fabric auf. Doch was steckt dahinter? Eben diese Frage versuchen wir nun einmal zu klären.

Mit der Zen- und Vega-Architektur führt AMD einen neuen Interconnect ein. An diesem Infinity Fabric hat AMD seit 4 Jahren gearbeitet. Der Name Fabric legt im Grunde schon nahe, um welche Struktur es sich handelt, denn Fabric heißt übersetzt Stoff und eben so ist auch dieser Interconnect aufgebaut. Laut AMD ist der Infinity Fabric modular aufgebaut und kann beliebig komplex ausgeführt werden. Eben diese Skalierbarkeit soll den Infinity Fabric in allen neuen Prozessoren und GPUs einsetzbar machen.

Der Infinity Fabric teilt sich auf in einen Control Fabric und Data Fabric. Der Control Fabric ist für die Ansteuerung der verschiedenen Engine-HUBs verantwortlich. Auf Basis des Control Fabric können Technologien wie das Power Management, Sicherheitsfunktionen, Reset&Initialization und das Testing durchgeführt werden. Der Data Fabric hingegen ist ein extrem schneller Interconnect, der dafür verantwortlich ist, dass die Daten schnellstmöglich innerhalb einer Architektur bewegt werden können. Über den Data Fabric wird auch die Verbindung zum Speicher sichergestellt. Im Falle der Vega-GPU bedeutet dies, dass der Interconnect bis zu 512 GB/s zur Anbindung des HBM2 bereitstellen muss. Im Falle eines Mobile-Prozessors mit DDR4-Arbeitsspeicher sind aber auch nur 40-50 GB/s notwendig. Eben dies soll zeigen, wie flexibel der Infinity Fabric ist.

Der Infinity Fabric ist Bestandteil der Vega-Architektur bei den Grafikkarten, aber auch von Summit Ridge bzw. den RYZEN-Prozessoren sowie den für das 2. Halbjahr geplanten Mobile-Prozessoren Raven Ridge, die ebenfalls unter der Marke RYZEN vermarktet werden sollen. Im Falle der Vega-Architektur soll der Infinity Fabric als Mesh, also in einer Gitterstruktur ausgeführt werden. Dies liegt vor allem daran, dass in einer GPU tausende von Shadereinheiten mit Daten gefüttert werden müssen und eine effiziente Verteilung der Daten ist über ein Mesh am besten möglich. Bei den Prozessoren sollen weniger komplexe Topologien für den Infinity Fabric zum Einsatz kommen. AMD wollte keine weiteren Details verraten, eine Ringstruktur wäre hier aber denkbar und wird beispielsweise auch von Intel so umgesetzt.

Der Infinity Fabric ist aber kein reiner Interconnect innerhalb einer CPU oder einer GPU. Laut AMD soll der Infinity Fabric auch in Multi-Socket-Verbindungen zum Einsatz kommen. Dort dient er als technische Basis für AMDs HyperTransport. Mehr zum Infinity Fabric werden wir sicherlich erfahren, wenn AMD den Vorhang zu Zen und Vega vollständig lüftet.

[h3]Bis zur ersten Hardware wird es noch etwas dauern[/h3]

Im Verlaufe der Demos zu Radeon Instict erwähnte Raja Koduri, Chef der Radeon Technologies Group, dass die gezeigte Hardware erst wenige Wochen alt gewesen sei. Der erste Tape Out von Vega 10 soll im Sommer stattgefunden haben. Dies deckt sich in etwa mit dem Zeitrahmen, den AMD zur Polaris-Architektur nannte. Auch hier soll das sogenannte Final Silicon Ende November bzw. Anfang Dezember 2015 vorhanden gewesen sein, wie wir alle wissen erschien die Radeon RX 480 Ende Juni 2016, also rund ein halbes Jahr später. Diesen Zeitplan auf Vega angewendet sehen wir die erste Desktop-Hardware auch nicht viel früher als Mai oder Juni 2017.

Dennoch können wir neben den theortischen Details zur Vega-Architektur auch noch ein paar weitere Details aus den Fotos des Events gewinnen. So hielt Raja Koduri die GPU mehrfach in die Kameras. Im GPU-Package zu erkennen sind zwei HBM-Speicherstacks. Damit könnte die GPU auf 8 oder 16 GB an HBM2 kommen. Das ausgestellte Demo-Systeme zeigte allerdings nur 8 GB an.

Derzeit wissen wir auch noch nicht, um welchen Ausbau der Vega-Architektur es sich bei der gezeigten Hardware handelt. Wir gehen davon aus, dass AMD bisher nur Vega 10 und damit die kleinere Ausbaustufe gezeigt hat. Kommen wir nun wieder zurück zum Demo-System mit Vega und den besagten 8 GB Speicherausbau. Mit HBM2 bestückt wäre es für AMD am logischsten, hier zwei Speicherstacks zu verwenden. Bei 4Hi HBM2 ergäbe dies die 8 GB Gesamtspeicherausbau und bei einem Takt von 1.000 MHz werden hier 256 GB/s pro Speicherstack und insgesamt 512 GB/s erreicht.

Aus der Vorstelltung der Radeon Instinct MI25, die ebenfalls eine Vega-GPU verwendet und zu der AMD eine Rechenleistung von 25 TFLOPS (FP16) angibt, ergibt sich aus angenommenen 4.096 Shadereinheiten ein GPU-Takt von 1.520 MHz. Ob dies letztendlich auch für die Desktop-Version zutrifft, wird sich noch zeigen müssen. Aufgrund der FPS in DOOM bei 3.840 x 2.160 Pixel und dem Ultra-Preset kann aktuell davon ausgegangen werden, dass die erste Vega-Grafikkarte etwas schneller als eine GeForce GTX 1080 sein wird. Genaueres lässt sich derzeit aber noch nicht abschätzen.

Da sich AMD mit der Angabe von technischen Daten noch etwas zurückhält, haben wir versucht aus den Bildern noch ein paar weitere Erkenntnisse zu gewinnen. Gefertigt wird diese wohl in 14 nm. Aus den Bildern der GPU sowie der bekannten Größe der HBM2-Speicherstacks (7,75 mm × 11,87 mm und 91,99 mm²) ergibt sich eine Die-Größe von etwa 520 bis 540 mm². Die Polaris-10-GPU kommt bei 232 mm² auf 5,7 Milliarden Transistoren. Vega 10 mit 520 mm² besäße damit in etwa 12,8 Milliarden Transistoren und wäre ähnlich komplex wie die GP102-GPU von NVIDIA auf der Titan X. Sollte die Größe über 500 mm² tatsächlich zutreffen sein, wäre die erste Vega-GPU deutlich komplexer, als zunächst vermutet. Die daraus zu erwartende Rohleistung müsste deutlich über dem liegen, was NVIDIA mit der GeForce GTX 1080 bieten kann.

Nun heißt es aber zunächst einmal zurücklehnen, denn so schnell werden wir noch keine Grafikkarte mit Vega-GPU sehen. Bis dahin wird AMD sicherlich auch noch einige Informationen veröffentlichen und spätestens mit dem finalen Release und der Verfügbarkeit werden dann auch die letzten Fragen zum Takt und Leistung beantwortet.