HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 115.245

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

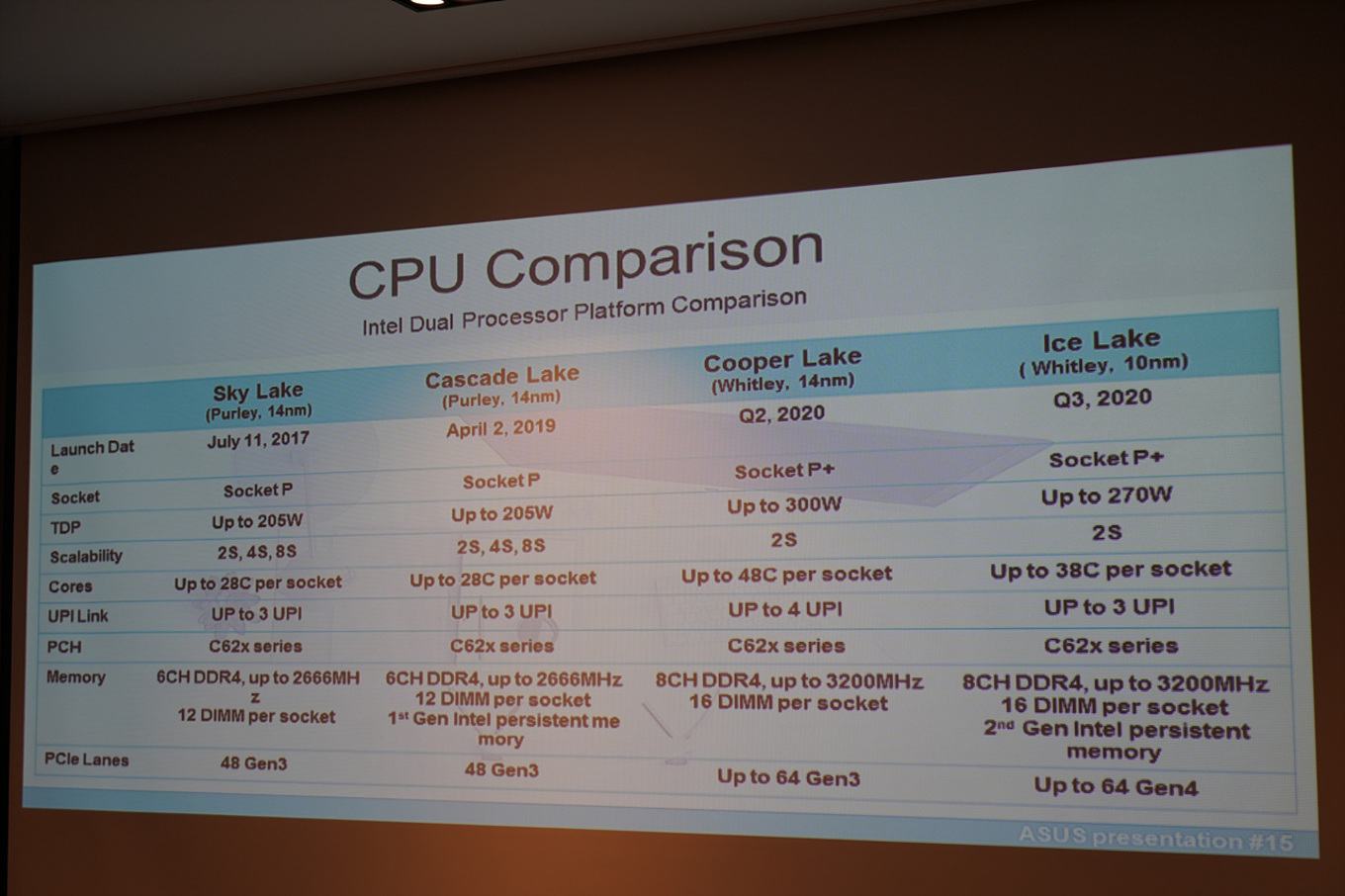

Fragen wirft auch auf, warum es maximal 2 Sockel System sein sollen, aber Cooper Lake sogar bis zu 4 UPI Links bekommen wird und auch Ice Lake bis zu 3.

Wo steht das ? oder ich bin wohl blind.Fragen wirft auch auf, warum es maximal 2 Sockel System sein sollen, aber Cooper Lake sogar bis zu 4 UPI Links bekommen wird und auch Ice Lake bis zu 3.

Größer als ein Board für ein 8 Socket Skylake oder Cascade Lake wird das Board auch nicht werden, auch wenn der Sockel nochmals ein paar Pins mehr bekommt. Das Argument zieht also nicht, zumal dies sowieso keine Boards sein werden die man so im Handel bekommen wird, oder hast Du schon ein 8 Sockelt LGA3647 auf Geizhals gefunden? 3 und erst recht 4 UPI machen bei maximal Dual Socket keinen Sinn!Versuch mal 4 so riesige Sockel auf einem Board unterzubringen.

Auf der Folie:Wo steht das ? oder ich bin wohl blind.

3 und erst recht 4 UPI machen bei maximal Dual Socket keinen Sinn!

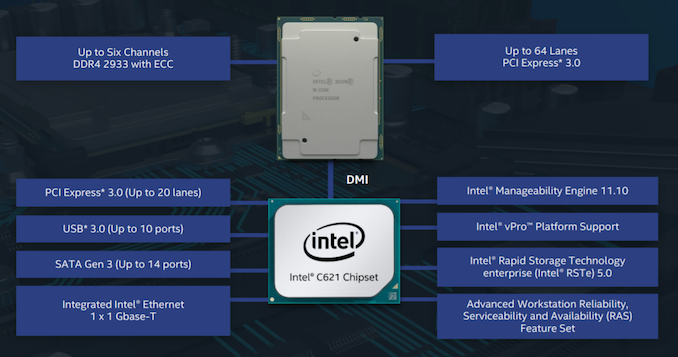

Entscheidend ist für Intel, dass so Gleichstand bei den wichtigen 2S Systemen herrscht. Die EPYCs verbrauchen je 64Lanes=128Lanes für die CPU-CPU-Kopplung. Intel dank der UPIs nicht, so dass man bei beiden 2S Systemen 128 Lanes zur Verfügung haben wird.Nun gut, 64 Lanes sind immerhin 50% eines ThreadRipper.

Der LGA3647 und die Dies haben also auch die Möglichkeit für 64 Lanes und da sind die 4 die als DMI3 zur Anbindung des Chipsatz genutzt werden, noch gar nicht mitgezählt.

ok sind 100% zum ThreadRipper, war wohl schon bei den EPYCs.Entscheidend ist für Intel, dass so Gleichstand bei den wichtigen 2S Systemen herrscht. Die EPYCs verbrauchen je 64Lanes=128Lanes für die CPU-CPU-Kopplung. Intel dank der UPIs nicht, so dass man bei beiden 2S Systemen 128 Lanes zur Verfügung haben wird.

Aktuell werden 4x16 Lanes für die Kopplung genutzt. Das entspricht zumindest im PCIe 3.0 Mode (keine Ahnung wie es im IF Mode aussieht) 4x15,75GBytes/s ca. 63 GByte/s. Da ist Intel also noch immer deutlich vorne: Denn es gibt bei 2S entweder 2x41GByte/s=82GByte/s oder 3x41GByte/s=123GByte/s. PCIe 4.0 verdoppelt nun die Transferrate, d.h. AMD kommt auf gleiche Werte wie Intel. Angesichts der Tatsache, dass man neue Boards entwerfen müsste und ohnehin kaum EPYC Boards verfügbar sind, denke ich nicht, dass sich da was ändern wird. AMD wird eher von der verbesserten Bandbreite profitieren wollen. Das war bisher ein großer Nachteil bei AMD Server CPUs.Wenn ich es richtig verstanden habe, werden von den 64, keine Lanes für die Infintiy Fabric benötigt: Why AMD EPYC Rome 2P Will Have 128-160 PCIe Gen4 Lanes and a Bonus

Wenn die Cooper Lake wieder als AP, also Doppel CPU in einem Gehäuse, kommen, dann machen 4 UPI schon Sinn, da man für eine bessere Bandbreite ja schon bei Skylake-SP Dual Socket dies beiden Sockel mit zwei UPI Links verbinden kann. Dann wären 2 für die Anbindung des Dies unter dem gleichen HS und die anderen beiden für die Anbindung je eines der Dies mit dem anderen Socket. Aber dann wären mit den nicht AP Modellen ja mehr als 2 Sockets zu erwarten, denn letztlich ist diese AP Geschichte ja nichts anderes als ein kompaktes Quad Socket System.

Da bist du mMn auf dem Holzweg, es ist nicht (nach der Huawaii Roadmap) ein zusätzlicher UPI Link, sondern es wird pro Prozessor genannt - und davon sollen zwei verschiedene kommen mit Cooper Lake.Das ein einzelnes Cooper lake Die aber nur 4 RAM Channels hat, halte ich für unwahrscheinlich, vielmehr werden bei den AP dann wohl nur 4 pro Die verwendet. Die Reduzierung auf 26 Kerne dürfte nämlich dem Umstand geschuldet sein, dass man statt zwei Kernen den Platz im Grid für die RAM Controller und das zusätzlichen UPI gebaucht hat, davon abgesehen dürfte es beim Aufbau wie bei den XCC der Vorgänger geblieben sein.

Auf der Huawaii Roadmap standen <=26C, auf dieser standen auch <=48C bzw. <=26C ein Cooper Lake, während auch schon von 56C/28C gesprochen wurde. MMn ist das sogar wahrscheinlicher als deine Annahme von nur halb aktivem SI. Denn das ergibt für mich keinen Sinn und nichtmal einen Vorteil, da es stark danach ausschaut, dass alles unter dem AP Ansatz mit Ice Lake bedient wird und der Cooper Lake primär AP like und für 4/8P herhalten soll. Vllt gibt's paar Ausnahmen, ist heute nicht abschätzbar...Es wurde schon am 17.11.2017, also vor fast genau 2 Jahren, von 38 Kernen geredet: