HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 112.400

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

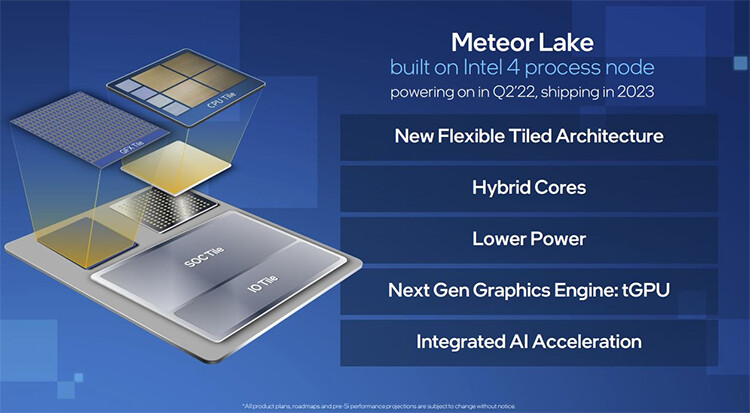

Im oberen Satz klingt es, als wäre I/O und SoC zwei getrennte Tiles, im zweiten als wäre es nur ein Die. Der Unterschied zwischen einer CPU und einem SoC ist, dass letzterer keinen extern Chipsatz hat und damit alle I/O Funktionen in der CPU integriert sind. Nun ist I/O ja recht vielschichtig, die Controller für RAM und PCIe Lanes wurden schon vor vielen Jahren in die CPUs integriert und damit die Northbridge eliminiert, die letzteren machen dann auch den PCH (aka Southbridge) überflüssig, wie es bei den mobilen CPUs der U Serien von Intel schon lange üblich ist. Die Frage ist aber eigentlich, ist es jetzt nur ein Tile oder übernehmen da zwei Tiles unterschiedliche I/O Ausgaben?Die SoC- , I/O- und die GPU-Tiles

...

für den I/O- und SoC-Tile

Nö, das missinterpretierst du...Im oberen Satz klingt es, als wäre I/O und SoC zwei getrennte Tiles, im zweiten als wäre es nur ein Die.

Da das nach wie vor meines Wissens nach nicht bekannt ist, dürfte das nicht aktuell beantwortbar sein.Die Frage ist aber eigentlich, ist es jetzt nur ein Tile oder übernehmen da zwei Tiles unterschiedliche I/O Ausgaben?

Nicht so?So sollte das aussehen:

Das Bild von Don oben zeigt zumindest eine genau so "tiled" CPU wie auf dem Bild zu sehen. Das von TPU ist ja "übermalt" - könnte zudem noch gespiegelt sein und es steht ja sogar drunter, dass es nicht Maßstabsgetreu ist.Wird interessant zu sehen ob Intel den dritten Typ an Cores in den SoC Tile schiebt. Falls ja, können die im Idle einfach den Compute Tile komplett abschalten. Das wäre mal ne Innovation.

Nicht so?

Na, das hat uns Intel doch hochoffiziell beigebracht... ;-) ... .... ... ...Warum sollte die Klebetechnik minderwertig sein?

Weil das damals eben messbar Nachteile bedeutet hat (Stichwort: Kommunikation zwischen den Modulen).Na, das hat uns Intel doch hochoffiziell beigebracht... ;-) ... .... ... ...

Nicht so?

Intel hatte damals die lahme IF kritisiert und die daraus resultierenden hohen Latenzen bei der Die-to-Die Kommunikation. AMD hatte ja auch insbesonderen an diesem Punkt bei den Nachfolgern gearbeitet..Na, das hat uns Intel doch hochoffiziell beigebracht... ;-) ... .... ... ...

Eben, die Verbindungstechnologie der Tiles macht den Unterschied und da setzt Intel mit Halbleiterinterposern auf eine weit fortschrittlichere Technologie als AMD bei seinen CPUs, die viel mehr Verbindungen ermöglichst und dafür sorgen dürfte, dass man eben keinen Unterschied zu einem monolithischen Design merken wird. Das war bei den ersten EYPC anderes, da war es ein großer Unterschied ob eine CPU auf RAM zugreift welches an ihrem eigenen RAM Controller hängt oder eben auf solches an einem RAM Controller eines anderen Dies. Dies hat AMD mit dem Übergang zum Chipletdesign mit einem zentralen I/O Die ja schon behoben, aber es bleiben immer noch deutlich höhere Latenzen zwischen den Kernen auf unterschiedlichen Dies. Wobei es aber eben sowieso nie zu vermeiden ist, auch bei einem Ringbus oder mit Mesh nicht, dass die Latenzen zwischen unterschiedlichen Kernen auch unterschiedlich ausfallen.Weil das damals eben messbar Nachteile bedeutet hat (Stichwort: Kommunikation zwischen den Modulen).

Heute hoffentlich nicht mehr.

Oder es ist durchweg ein Fake. Letzteres könnte erklären wieso auf der unteren Folie bei DDR5 von "up to 96GB" die Rede ist, bei 1DPC (also ein DIMM pro Kanal) wären dies mit 48GB Riegeln (die meines Wissens nach nicht geplant sind) oder 3 RAM Channels sprechen, aber bei LPDDR5 ist von "up to 64GB" die Rede (wobei das ) dahinter fehlt und dies würde wieder nur für 2 RAM Channels sprechen, denn wieso sollte ein RAM Controller nur bei DDR5 3 Kanälen, aber bei der Lower Power Version davon nur 2 Kanäle unterstützen?

Ich musste erst einmal Google bemühen, um in Erfahrung zu bringen, was Trendforce überhaupt ist. Dann habe ich eine Artikel von denen entdeckt, wo diese folgendes behauptet haben: "While the company is planning to kick off mass production of Core i3 CPUs at TSMC’s 5nm node in 2H21, Intel’s mid-range and high-end CPUs are projected to enter mass production using TSMC’s 3nm node in 2H22."Eine Hiobsbotschaft wenn man es so nennen will:

Aber aber, wenn du dein AMD Abwatschen unterlassen würdest, könntest du zumindest nicht mehr als negatives Beispiel gelten.Aber Hey, es ist Intel Bashing und dies liegt im Trend, also Rein immer rein in die Olga..

Ich habe nur die Nachricht hier verlinkt und mir ist das voll egal ob und was Intel, AMD oder die Marsmännchen liefern.Nur aufgrund irgendwelcher Gerüchte, ohne wirkliche Quellenangabe, direkt von einer "Hiobsbotschaft" zu schreiben, ist ein wenig übertrieben, findest du nicht auch?

Aber Hey, es ist Intel Bashing und dies liegt im Trend, also Rein immer rein in die Olga..

Also dieser Part ^ sieht mir nicht nach einer reinen Verlinkung aus, sondern eher wie eine Bewertung der Nachricht. Und so, wie du diesen Part formuliert hast, suggeriert dies mir als Leser deines Beitrags, als würdest du davon ausgehen, dass dieses haltlose Gerücht bereits eine Tatsache sei.Eine Hiobsbotschaft wenn man es so nennen will: