HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 120.871

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Da gibts verschiedene Möglichkeiten und Intel hat auch schon solche FPGAs in Xeon-Prozessoren gepackt.Was macht der Altera chip?

So furchtbar viel mehr wird auch in Produktivsystemen zumindest der Basistakt nicht hergeben können.Der angegebene Takt auf dem Package beträgt vergleichsweise niedrige 1,3 GHz. Dies ist für Engineering Samples von Intel allerdings nicht unüblich.

Gerüchten zufolge 15-16 Kerne pro Chiplet, von denen 14 aktiv sind.Hmm.

Per Die 32 Cores und 20~25 Mrd. Transistoren?

Mehr cache macht durchaus sinn, mann will ja so wenig wie möglich daten über die leitungen zu den chiplets oder wie hier, gluelets schieben.Also entweder Intel hat riesige Mengen an Cache auf jedem Die oder es sind weit mehr Kerne untergebracht als man uns verraten will...

Nein, weil man keinen derart schlechten Interconnect wie IF verwenden wird.Ob man nun auch mit "inconsistent performance and higher latencies due to die-to-die interconnect" wirbt?

Jetzt bin ich aber gespannt... Was genau hat Intel denn bereits über den Interconnect gesagt? Hast du evtl. einen Link? Und wie kommst du drauf das es bei AMD am IF liegt?weil man keinen derart schlechten Interconnect wie IF verwenden wird.

Fast die halbe Die-Fläche ist off-core und kein fetter zusätzlicher L3 weit und breit; sieht ganz nach dem üblichen Cove-Design aus.Das das Auffüllen vom Platz ausschließlich mit Cache utopisch ist sollte klar sein. Aber irgendwas müssen die dort ja gemacht haben, man wird wohl kaum den Chip größer machen als nötig.

Intel wird EMIB nutzen, wie sie es schon bei Kaby Lake-G gemacht haben, während AMD bei allen seinen CPUs bisher einfach Dies auf eine Platine lötet, also im Grunde nur BGA nimmt. Erst mit dem gestapelten 3D V-Cache kommt dann auch bei AMD eine modernere Verbindungstechnologie bei CPUs zu Einsatz die viel mehr Verbindungen erlaubt. Mit EMIB und Mesh kann Intel die Dies wahrscheinlich so verbinden, dass es für die Latenz keinen wirklichen Unterschied macht ob benachbarte Kerne auf dem gleichen oder unterschiedlichen Dies sitzen. Das das Ansatz bei Naples und den X399er TR nicht gerade glücklich war, hat AMD doch selbst erkannt und ist deshalb mit Zen2 auf den zentralen I/O Dies umgestiegen, der viele der vorherigen Probleme mit unterschiedlichen Latenzen vermeidet. Mit Zen3 hat AMD dann auch mit dem Wechseln von 4 auf 8 Kerne von CCX das Problem behoben, dass bei Zen2 auch die Kerne auf unterschiedlichen CCX des gleichen Dies nur über das I/O Die miteinander kommunizieren können. Bei Anwendungen / Benchmarks wie Cinebench wo die Kerne jeder für sich auf einem eigenen Teil der Daten arbeiten ohne viel miteinander kommunizieren zu müssen, macht sowas alles nicht viel aus, aber bei Anwendungen mit viel Kommunikation zwischen den Kernen eben schon.Jetzt bin ich aber gespannt... Was genau hat Intel denn bereits über den Interconnect gesagt?

Das muss man unabhängig von Fertigungsproblemen schon wegen der gewaltig steigenden Entwicklungskosten für das Desgin bei kleineren Fertigungsverfahren, vom Design bis zu den Masken. Die machen es immer unwirtschaftlicher sehr komplexe Chips zu entwickeln und dann noch ähnliche Chips in unterschiedlichen Konfigurationen wie Intel es bei den Xeons bisher in Form der LCC, HCC und XCC Dies macht. Es ist aber auch unwirtschaftlich nur das XCC Die mit 40 oder mehr Kernen zu entwickeln und dann davon auch 8 Kerner zu verkaufen, bei dem 3/4 des Dies ungenutzt bleiben und solche Xeons sind die Brot-und Butter Modelle, die Topmodell machen nur wenige Prozent der Verkäufe aus. Daher macht es mehr Sinn einfach den Uncore in einem eigenen Dies zu fertigen, der kann auch in 14nm gefertigt werden, wenn man dies will und dann eben Chiplets mit 8 oder 12 Kernen und je nach Modell mehr oder weniger viele davon, die alle über EMIB und das Mesh mit ihren Nachbarn verbunden sind.Dennoch bleibt Intel in Anbetracht der Probleme mit dem Fertigungsprozess keine andere Wahl, als auf einen Ansatz mit chiplets umzustellen.

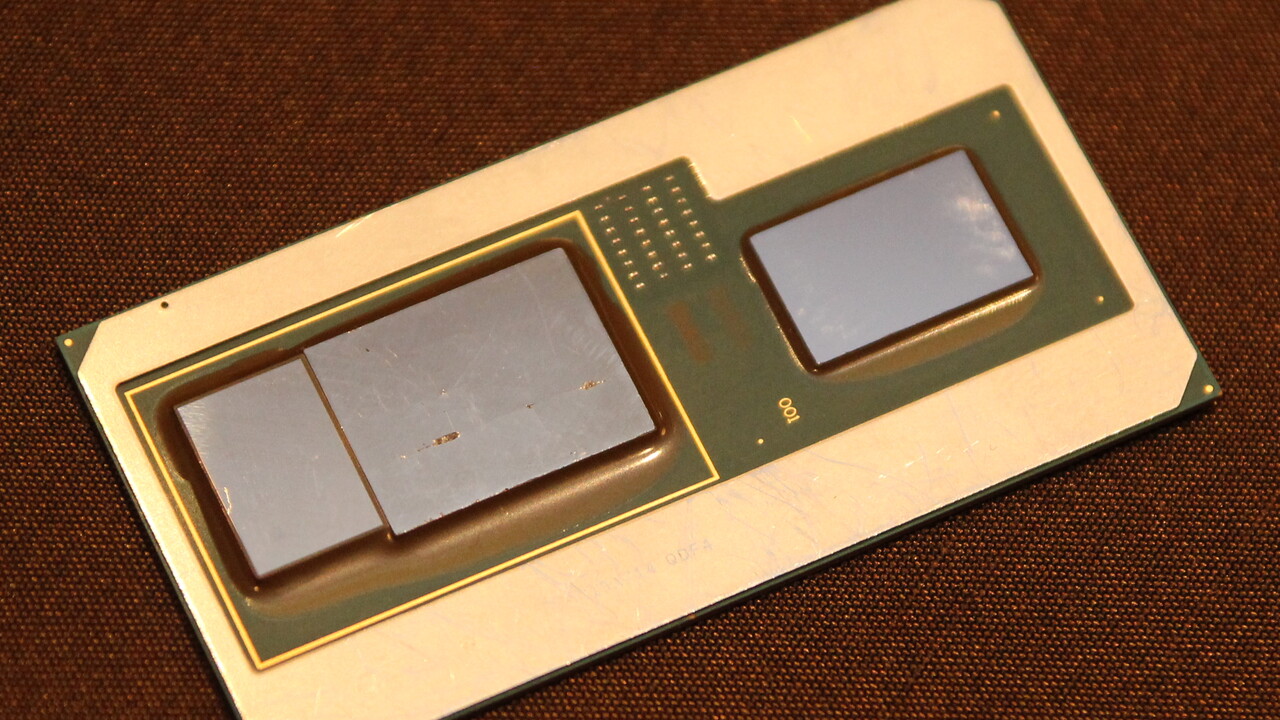

Wenn 20 Dies auf einem Chiplet sind und es 4x5 = 20 davon gibt, dann wäre dies sogar 400 Kerne. Dies scheint mir nun aber doch übertrieben, so viel weniger Chipfläche braucht ein Dies dann in 10nm auch wieder nicht und die Kerne werden ja nicht abgespeckt. Aber auf diesem Bild sieht man klar 4x5 Dies und es sieht so aus, als wären an der Seite noch weitere Dies für den Uncorebereich. Also entweder sind die 20 Strukturen auf den einzelnen Dies gar nicht je ein Kern oder es ist wie bei Xeon Phi ein kleiner Kern um extrem viele Kerne zu ermöglichen. Oder das ganze war ein Fake, denn die zuletzt veröffentlichten Fotos sagen ja folgendes aus:

Wobei man auf dem Dieshot keine zusätzlichen Dies sieht, die direkt mit den 4 per Halbleiterinterposer verbunden sind. Demnach dürfte der Uncore Bereich, also was bei AMD im I/O Die steckt, in einem Chiplet unter den CPU Chiplets stecken, genau wie bei Lakefield, eine Technik die Intel Foveros nennt.

Intel wird EMIB nutzen, wie sie es schon bei Kaby Lake-G gemacht haben, während AMD bei allen seinen CPUs bisher einfach Dies auf eine Platine lötet, also im Grunde nur BGA nimmt. Erst mit dem gestapelten 3D V-Cache kommt dann auch bei AMD eine modernere Verbindungstechnologie bei CPUs zu Einsatz die viel mehr Verbindungen erlaubt. Mit EMIB und Mesh kann Intel die Dies wahrscheinlich so verbinden, dass es für die Latenz keinen wirklichen Unterschied macht ob benachbarte Kerne auf dem gleichen oder unterschiedlichen Dies sitzen. Das das Ansatz bei Naples und den X399er TR nicht gerade glücklich war, hat AMD doch selbst erkannt und ist deshalb mit Zen2 auf den zentralen I/O Dies umgestiegen, der viele der vorherigen Probleme mit unterschiedlichen Latenzen vermeidet. Mit Zen3 hat AMD dann auch mit dem Wechseln von 4 auf 8 Kerne von CCX das Problem behoben, dass bei Zen2 auch die Kerne auf unterschiedlichen CCX des gleichen Dies nur über das I/O Die miteinander kommunizieren können. Bei Anwendungen / Benchmarks wie Cinebench wo die Kerne jeder für sich auf einem eigenen Teil der Daten arbeiten ohne viel miteinander kommunizieren zu müssen, macht sowas alles nicht viel aus, aber bei Anwendungen mit viel Kommunikation zwischen den Kernen eben schon.

Das muss man unabhängig von Fertigungsproblemen schon wegen der gewaltig steigenden Entwicklungskosten für das Desgin bei kleineren Fertigungsverfahren, vom Design bis zu den Masken. Die machen es immer unwirtschaftlicher sehr komplexe Chips zu entwickeln und dann noch ähnliche Chips in unterschiedlichen Konfigurationen wie Intel es bei den Xeons bisher in Form der LCC, HCC und XCC Dies macht. Es ist aber auch unwirtschaftlich nur das XCC Die mit 40 oder mehr Kernen zu entwickeln und dann davon auch 8 Kerner zu verkaufen, bei dem 3/4 des Dies ungenutzt bleiben und solche Xeons sind die Brot-und Butter Modelle, die Topmodell machen nur wenige Prozent der Verkäufe aus. Daher macht es mehr Sinn einfach den Uncore in einem eigenen Dies zu fertigen, der kann auch in 14nm gefertigt werden, wenn man dies will und dann eben Chiplets mit 8 oder 12 Kernen und je nach Modell mehr oder weniger viele davon, die alle über EMIB und das Mesh mit ihren Nachbarn verbunden sind.

Nachdem TSMC ja nun offenbar auch solche Verbindungstechnologien besitzt, wird man früher oder später auch bei AMD so einen Ansatz sehen, einfach weil der sich dann genau wie ein monolithisches Die verhält, wenn man das Design richtig gemacht hat, was bei der Verbindungstechnik die AMD bisher nutzt, eben nicht geht, da man einfach nicht genug Verbindungen zwischen den Dies realisieren kann, dies geht nur wenn Halbleiterinterposer nimmt, also Halbleiter mit Halbleiter verbindet. Genau das macht man ja auch bei gestapelten NAND Dies, Intels 144L NAND ist das erste so sogar 3 Dies gestapelt sind und die 670p die dieses Dies hat, performt viel besser als ihre Vorgänger und auch bei dem gestapelten 3D V-Cache wird das zusätzliche RAM auf die Zen3 Chiplets gesetzt und direkt durchkontaktiert.

Solche Verbindungstechniken kosten natürlich auch Geld, wobei man sich beim Stapeln im Gegensatz zu EMIB das zusätzliche Die für die Verbindung spart. Es ist auch kein Zufall, dass solche Verbindungstechnologien jetzt verfügbar sind, sondern es war absehbar, dass man sie brauchen würde, je kleiner die Fertigungsverfahren werden und damit Entwicklungskosten für große monoplitische Dies werden, so dass ihre Wirtschaftlichkeit nur noch bei immer größeren Stückzahlen erreicht werden kann. Das liegt auch der Grund warum AMD bei Zen und Naples diese Ansatz gewählt hat, die hatten entweder gar nicht das Geld oder wollten das gewaltige Risiko nicht eingehen, große monolithische Dies für Server CPUs zu entwickeln, deren Absatzchancen gar nicht vorhersehbar waren, nachdem sie diesen Markt über Jahre praktisch gar nicht mehr bedient hatten.

Aber auch für Intel wird es nicht leichter werden die nötigen Stückzahlen zu erreichen, zumal Server CPUs immer mehr Kerne haben können und es damit immer mehr unterschiedliche Modelle geben muss, um den Kunden das für sie passende Modell bieten zu können. Vor nicht einmal 8 Jahren erschien Ivy Bridge-EP mit 18 SKUs basierend auf 3 Dies mit 6, 10 und 12 Kernen. Vor fast 4 Jahren erschien Skylake-SP mit bestimmt dreimal so vielen SKUs (habe sie nicht gezählt) und maximal 28 Kernen. Für Ice Lake-SP gibt Intels Seite auch maximal 28 Kerne an, obwohl durch den kleineren 10nm Fertigungsprozess weit mehr auf die gleiche Diefläche passen würden, grob doppelt so viele. Dies wird man mit Sapphire Rapids dann auch nutzen wollen, zumal der Sockel und damit der Platz unter dem HS noch größer wird. Wie viele SKUs es dann geben wird, kann man sich ja vorstellen-

Wenn 20 Dies auf einem Chiplet sind und es 4x5 = 20 davon gibt, dann wäre dies sogar 400 Kerne. Dies scheint mir nun aber doch übertrieben, so viel weniger Chipfläche braucht ein Dies dann in 10nm auch wieder nicht und die Kerne werden ja nicht abgespeckt. Aber auf diesem Bild sieht man klar 4x5 Dies und es sieht so aus, als wären an der Seite noch weitere Dies für den Uncorebereich. Also entweder sind die 20 Strukturen auf den einzelnen Dies gar nicht je ein Kern oder es ist wie bei Xeon Phi ein kleiner Kern um extrem viele Kerne zu ermöglichen. Oder das ganze war ein Fake, denn die zuletzt veröffentlichten Fotos sagen ja folgendes aus:

Wobei man auf dem Dieshot keine zusätzlichen Dies sieht, die direkt mit den 4 per Halbleiterinterposer verbunden sind. Demnach dürfte der Uncore Bereich, also was bei AMD im I/O Die steckt, in einem Chiplet unter den CPU Chiplets stecken, genau wie bei Lakefield, eine Technik die Intel Foveros nennt.

Intel wird EMIB nutzen, wie sie es schon bei Kaby Lake-G gemacht haben, während AMD bei allen seinen CPUs bisher einfach Dies auf eine Platine lötet, also im Grunde nur BGA nimmt. Erst mit dem gestapelten 3D V-Cache kommt dann auch bei AMD eine modernere Verbindungstechnologie bei CPUs zu Einsatz die viel mehr Verbindungen erlaubt.

Wo soll ich angeblich was durcheinanderwerfen?Du schmeißt hier die Techniken durcheinander

Also hast Du gesehen, wo da EMIB eingesetzt wurde.EDIT: nevermind...

TSMC hat inzwischen vergleichbare Packingstechnologien, daher vermute ich ja, dass künftig auch AMD solche Technologien einsetzen wird, weil das eben die Nachteile von Chiplet Designs bezgl. der Verbindung der Chiplets ausgleicht. Deshalb steht ja auch auf der Folie in Post #2 oben "Implementation matters" und wie sehr das stimmt, hat man ja bei EPYC und TR beim Wechsel von Zen(+) mit 4 Desktop Dies auf Zen2 mit dem I/O Die auch schon deutlich gesehen.TSMCs Entsprechung von Intels EMIB

Richtig und ich habe ja auch nie behauptet, dass es etwas mit der Technologie der physischen Anbindung der Dies untereinander zu tun hätte, die ist bei beiden gleich und im Prinzip wie BGA. Naples ist eben eine glued together Prozessor aus 4 Desktop Dies der eigentlich Multi-Prozessor-System auf einem gemeinsamen Träger ist und weniger eine komogene CPU, wie man sie dann mit Technologien wie EMIB erreichen kann. Daher ist die Folie in Post #2 richtig und taugt nicht um darüber zu spotten, wenn Intel nun auch auf Chiplets setzt. "Implementation matters" und dies zeigt sich eben auch deutlich beim Wechsel von Naples auf Rome, also von vier Desktop Dies unter einen HS zu 4 CCX Chiplets mit einem zentralen I/O Die, unabhängig von der verwendeten Verbindungstechnologie für diese Dies.Von Zen zu Zen2 hat sich die Topologie der CPU völlig geändert:

Naples ist eigentlich ein Multi-Prozessor-System auf einem gemeinsamen Träger.

Rome ist ein Prozessor mit auf verschiedene Dies aufgeteilten Resourcen.

Das hat erst einmal grundsätzlich mit der physischen Anbindung der Dies untereinander nichts zu tun.

Die IF braucht man eben, um mit den beschränkten Anzahl an Verbindungen auszukommen die mit dieser Verbindungstechnologie möglich ist, trotzdem eine hohe Bandbreite zu erreichen.Der Nachteil von AMDs Chiplet-Design ist die Latenz der IF-Die-zu-Die-Verbindung.

Mal sehen was AMD da in Zukunft machen wird, Intels Wechsel vom Ringbus zu Mesh dürfte jedenfalls bzgl. des Chiplet Designs ein guter Schritt gewesen sein, da man damit die Dies über das Mesh verbinden und so sehr vielen parallele Verbindungen bekommen kann.Ich bin gespannt, ob sowas realisiert werden wird.