Averomoe, AM4 hat mit einer RYZEN CPU (mit den APUs sind es teils weniger) 16 PCIe 3.0 Lanes die für die Graka sind und nur in x8/x8 aufgeteilt werden können, zumindest offiziell, bei TR der ja die gleichen Dies hat, geht auch x4/x4/x4/x4. Dann gibt es je bei den ganzen AM Prozessoren auch einen internen Chipsatz, der bietet nochmal 4 (bei APUs teils nur 2) PCIe 3.0 Lanes und 2 SATA Ports, allerdings sind die geshared. Bei B350/450 Boards mit 6 SATA Ports sieht man dies häufig, der B350/450 ist der externe Chipsatz und hat selbst nur 4 SATA Lane, die andere beiden kommen dann meist von internen Chipsatz und fallen eben weg, wenn man den M.2 Slot belegt. Diesen externen Chipsätze sind auch noch mal mit 4 PCIe 3.0 Lanes angebunden und weil es ja auch die Pseudo-Chipsätze A300 und X300 gibt die selbst keine I/O bieten und daher auch nicht diese 4 Lanes belegen, zählt AMD sie mit und kommt auf 24 PCIe 3.0 Lanes, aber außer einem Board in einem Mini-Formfaktor welches kürzlich vorgestellt wurde, gibt es keine A300 oder X300 und damit praktisch also 20 PCIe 3.0 Lanes.

Die externen Chipsätze haben auch noch mal PCIe Lanes, aber nur bis zu 8 PCIe 2.0 Lanes. Bei einigen wenigen X370/470 Boards werden auch die 2 PCIe 3.0 Lanes verwendet, die sind dann aber nie an Slots, sondern immer fest mit einem Controller Onboard verbunden, denn sie sollen gerüchteweise die PCIe Spezifikation nicht einhalten und damit kann man da eben nur Controller anhängen die damit kein Problem haben.

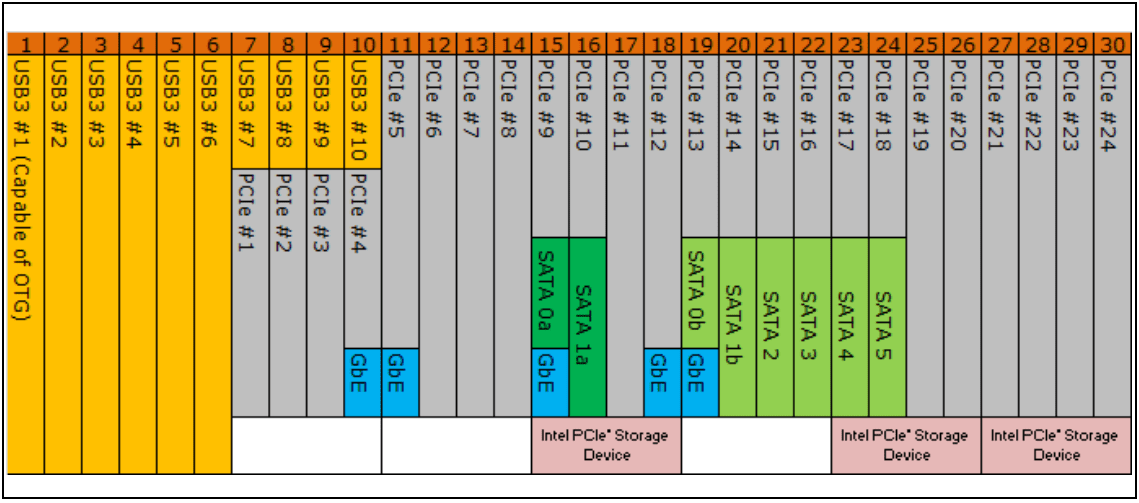

Bei Intels S. 1151(v2) sieht es so aus, dass die CPUs ebenfalls 16 PCIe 3.0 Lanes haben die wie die 16 von AM4 für die Graka gedacht sind, aber nicht zwangsweise so verwendet werden müssen. Diese lassen sich bei Intel auf Boards mit Z Chipsatz (oder C für die Xeons) dann in x8/x8 oder x8/x4/x4 aufteilen. Dazu kommen 4 für die Anbindung des Chipsatzes, die sich zwar DMI3 nennt, technisch aber PCIe 3.0 x4 ist. Die Chipsätze bieten bei Intel seit den 100ern (außer dem H110 und H310) PCIe 3.0 Lanes und zwar bis zu 24 im Fall der Z270, Z370 und Z390. Dieses sind aber auch teilweise mit anderen I/O geshared:

Die wo unten Intel PCIe Storage Device steht, sind die üblicherweise an die M.2 Slots geführt werden, denn nur die unterstützen RAID oder das Caching mit den Optane SSDs. Die die Anfangs erwähnten 16 direkt von der CPU kommen noch dazu, insgesamt kann man bei S.1151(v2) also bis zu 40 PCIe 3.0 Lanes haben, bei AM4 bis zu 20 (22 sollte das Boards die beiden des externen Chipsatzes nutzen) plus 8 PCIe 2.0 Lanes. AMD hat ja 500er Chipsätze angekündigt, mal sehen was sie da bzgl. der PCIe Lanes machen werden.

Intel dürfte erst mit dem nächsten Sockel, also frühestens Ende des Jahres mit Ice Lake, sollten sie es schaffen den bis dahin auf den Markt zu bekommen, dann auf PCIe 4.0 wechseln und dann ist auch da die Frage ob dies nun nur die Lanes der CPU betrifft die für die Graka gedacht sind oder auch gleich die Lanes der Chipsätze (und damit natürlich auch deren Anbindung). Historisch haben diese ja die schnelleren PCIe Lanes immer erst eine ganze Weile später bekommen, so hatte Iva Bridge PCIe 3.0 Lanes, aber erst mit Skylake kamen diese in die Chipsätze und AMD hat mit FM2+ PCIe 3.0 eingeführt, aber im Grunde bis heute nicht wirklich in den Chipsätzen, von den beiden genannten Lanes und dem internen Chips der CPU mal abgesehen.

Mehr PCIe Lanes wird der AM4 Sockel nicht bekommen können, dazu bräuchte man mehr Pins und hätte man diese gewollt, so hätte man dies schon von Anfang an haben können, denn im Zeppelin Die stecken noch mindestens 8 PCIe 3.0 Lanes mehr drin, sonst wären es bei den TR ja nicht möglich so viele PCIe Lanes zu haben. Die TR haben nämlich 60 plus den 4 für den X399er Chipsatz und zwar sind das 16+16 (die eben auch bei AM4 für die Graka da sind) +8+8 (diese 8 Lanes bleiben bei AM4 ungenutzt) +4+4 (der beiden internen Chipsätze) +4 (die eben für die Anbindung des externen Chipsatzes genutzt werden, aber man braucht sie ja nur von einem Die dafür, bei anderen Die sind sie daher frei).

Mo3Jo3, nein man kann nicht einfach eine PCIe 3.0 x4 SSD an zwei PCIe 4.0 Lanes mit voller Performance betreiben. Bei PCIe gilt bzgl. der Anzahl als auch der Geschwindigkeit der Lanes jeweils der kleinste gemeinsame Nenner, als dem Fall dann 2 Lanes mit den 8Gb/s von PCIe 3.0 Um die zu umgehen wäre ein entsprechender PCIe Switch (auch als PLX Chips bekannt) nötig, die sind aber teuer (

vor allem seit Avago 2014 PLX übernommen hat) und brauchen viel Strom, weshalb sie kaum noch auf den Boards zu finden sind, während es früher öfter welche gab um mehr PCIe Lanes für Grakas zur Verfügung zu stellen.

Wie teuer die PLX Chips sind, zeigt der Vergleich der

ASUS Hyper M.2 X16 Card (90MC05G0-M0EAY0) (die war schon mal für 40€ zu haben) die keinen PLX Chip hat, so dass nur dann alle M.2 Slots funktionieren, wenn der x16 Slot PCIe Lane Bifurkation auf x4/x4/x4/x4 erlaubt (wie bei TR4 und S.2066) mit dem Preis der

HighPoint SSD7102 die

einen PLX Chip hat, da gehen also immer alle 4 M.2 Slots, egal was der PCIe Slot kann in dem sie steckt und selbst wenn der nur eine PCIe Lane besitzen würde, könnte man damit 4 SSDs betreiben, wenn auch mit unterirdischer Performance.

:

: