Werbung

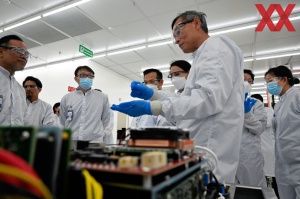

Im Rahmen der Intel Tech Tour 2023 hatten wir Gelegenheit, die wichtigsten Einrichtungen des Chipgiganten in Malaysia zu besuchen. Viele werden sich sicherlich nicht des vollen Umfangs bewusst sein, wie umfangreich die Anstrengungen eines Prozessor-Herstellers sind, um aus einem Silizium-Wafer das finale Endprodukt zu entwickeln. Die Dimensionen dieser Anstrengungen einmal vor Ort zu erleben, ist aber noch einmal eine andere Geschichte. Ein wenig des Erlebten wollen wir an dieser Stelle auch an euch Leser transportieren – zumindest soweit dies über geschriebenen Text und ein paar Bilder eben geht.

Vorweg sei gesagt: Hardwareluxx hat auf Einladung Intels an der Tech Tour 2023 teilgenommen. Sämtliche Reise- und Übernachtungskosten wurden übernommen.

"Warum Malaysia?", könnte man sich nun fragen? Wer schon einmal einen genauen Blick auf die Verpackung oder den Prozessor selbst geworfen hat, wird, unabhängig davon, ob es sich um ein Modell von AMD oder Intel handelt, festgestellt haben, dass hier oftmals "Assembled in Malaysia" zu lesen ist. Neben der reinen Fertigung der Chips besitzt Intel fast 40 % der weltweiten Kapazität im Bereich des FCBGA- und FCLGA-Packaging. Eben diese Formen des Packagings werden für die aktuellen Prozessoren verwendet – sowohl im Endkunden- wie auch im Server-Segment.

1972 eröffnete Intel als erster Halbleiterhersteller ein Packaging-Werk in Malaysia. 100 Mitarbeiter setzten in der Einrichtung namens A1 die ersten Mikroprozessoren zusammen. Inzwischen arbeiten etwa 15.000 Mitarbeiter für Intel in Malaysia – aufgeteilt in einem guten Dutzend an Gebäuden in zwei Industrieparks in Penang und Kulim. Neben fast allen alten Prozessor-Generationen von Intel werden auch die kommenden Meteor-Lake-Prozessoren in Malaysia zusammengesetzt.

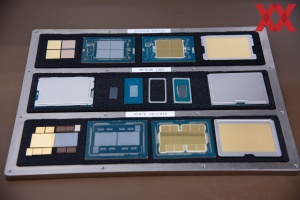

Mit dem Wechsel zu einem desintegrierten Design (Chiplet- oder Tile-Design) wird das Packaging auch bei Intel immer wichtiger. Dies ist allerdings kein neuer Trend oder etwas, was völlig unerwartet kommt. Nahezu alle Chip-Hersteller arbeiten in diese Richtung oder haben es bereits getan. Meteor Lake wird Intels erster Prozessor für Endkunden sein, der auf ein Chiplet-Design setzt.

Um die Bedeutung von Intel Malaysia zu verstehen, muss man sich die Prozess-Kette einmal vor Augen führen. Intel unterhält Wafer Fabs in den USA (Oregon, Arizona, Ohio), Irland und Israel - dort werden die Wafer belichtet. Unser Besuch in Israel im vergangenen Jahr zeigt den Weg bis dahin, was nun in den weiteren Schritten geschieht. Auf diese einzelnen Schritte werden wir noch genauer eingehen, zunächst einmal aber der grobe Ablauf:

- Die Wafer kommen in der DSDP-Einrichtung (Die Sort und Die Preparation) an. Hier werden die einzelnen Dies separiert und sortiert, sodass sie am Ende entsprechend ihrer Funktion der jeweiligen CPU-Variante zugeordnet werden können.

- Von dort geht es dann zum PGAT (Penang Assembly und Test). Hier werden die Chips zu einem Package verarbeitet und getestet.

- Bereits während der Produktion untersucht das Failure Analysis Lab eventuelle Schwachstellen. Hier kommen dann teilweise Chips hinzu, die sich im Development Lab noch in der Test- und Evaluierungsphase befinden.

- Design und Development Lab bzw. Forschung und Entwicklung sind mit 6.000 Mitarbeitern ein großer und wichtiger Bestandteil der Bestrebungen von Intel in Malaysia. Vom IP-Design (USB, PCI-Express, DDR) über eine Pre-Silicon-Validierung bis hin zur Entwicklung von CPU-, SoC-, Chipsatz- und FPGA-Designs decken die Einrichtungen von Intel in Malaysia gut 80 % aller Produkte von Intel ab.

- Schlussendlich betreibt Intel mit SIMS (System Integration and Manufacturing Services) auch noch eine große Forschungs- und Entwicklungsabteilung in Malaysia, welche die Testplattformen selbst entwickelt und herstellt, die dann zu Tausenden in den Fabriken rund um den Globus zum Einsatz kommen.

Es sei an dieser Stelle aber gesagt, dass uns Intel aus organisatorischen Gründen an zwei Tagen in einer anderen Reihenfolge durch die Einrichtungen geführt hat. Wir haben uns zunächst das Design und Development Lab angeschaut, danach das Failure Analysis Lab und am Ende des ersten Tages Penang Assembly und Test. System Integration and Manufacturing Services sowie Die Sort und Die Preparation standen am zweiten Tag auf dem Plan. In gewisser Weise haben wir den Prozess von hinten aufgerollt, in diesem Bericht aber wollen wir den Weg nachzeichnen, den ein Chip macht.

DSDP: Die Sort und Die Preperation

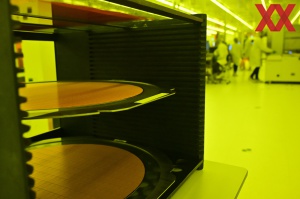

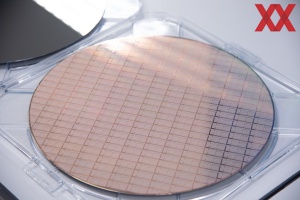

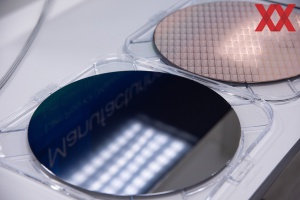

Beginnen wir also von vorne – zumindest in den Fällen, in denen die Wafer direkt und ohne Zwischenschritt von der Fab nach Malaysia kommen. Sind zuvor weitere Verarbeitungsschritte, zum Beispiel das Verbinden mehrere Chips mittels Foveros-Technologie, notwendig, geschieht dies aktuell noch nicht in Malaysia.

Die Wafer kommen also vor Ort an und sollen vereinzelt werden. Je nach Chip wird der Wafer zunächst auf eine vorher definierte Dicke heruntergeschliffen. Notebook-Chips sind meist etwas dünner, die Chips der Desktop- und Server-Prozessoren etwas dicker. Das Power-Budget bzw. die Kühlung und Verteilung der Abwärme spielt hier eine wichtige Rolle.

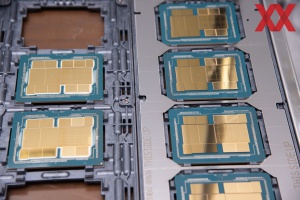

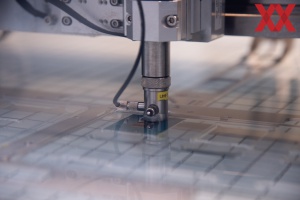

In einem nächsten Schritt geht es dann an die wirkliche Vereinzelung der Chips. Dies geschieht anhand der Scrible-Linien, die sich bereits zwischen den einzelnen Chip befinden. Auf Basis dieser wird erkannt, wo geschnitten werden soll. Ein Laser macht einen Pre-Cut und bereitet die Arbeit der Diamantsäge vor. Zwei kleine Sägeblätter fahren über den Wafer und schneiden diesen. Wenige Mikrometer bleiben stehen, sodass die Chips noch immer auf dem Wafer-Träger gehalten und transportiert werden können. Bei diesem Prozessschritt sind wir im Übrigen auf einen Wafer gestoßen, der offensichtlich Emerald-Rapids-XCC-Dies trug. Auf Emerald Rapids sind wir in der DSDP-Abteilung des Öfteren gestoßen. Die Fertigung dieser Prozessoren läuft also auch bereits auf Hochtouren.

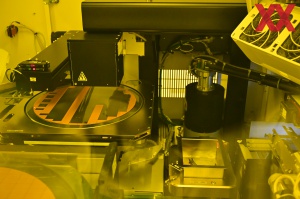

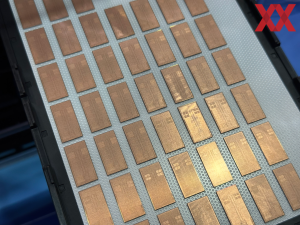

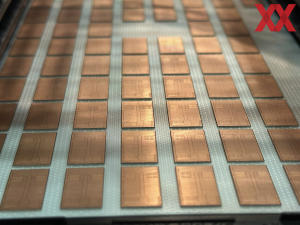

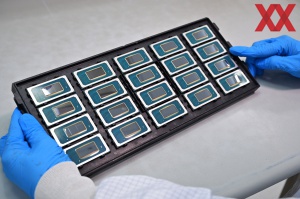

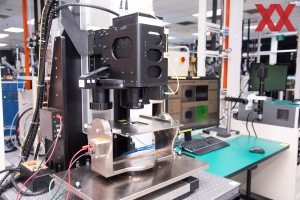

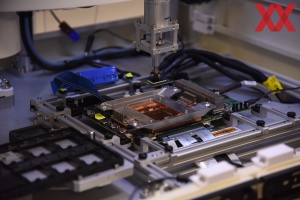

Ein Picker nimmt die vollständigen Chips – am Rand befinden sich je nach Größe der Chips auf dem Wafer immer ein gewisser Ausschuss, der an der Rundung des Wafer abgeschnitten ist – und setzt diese auf einen Tray. In diesem Tray begeben sich die Chips in die Sortieranlage, in der jeder einzelne Chip geprüft wird. Per Adhäsion halten die Chips auf dem Tray. Im SDX-Tester wird jeder einzelne Chip auf eine Probing Card gesetzt. Diese besitzt bis zu 20.000 feine Probing-Nadeln, die Kontakt mit dem Chip aufnehmen. Die Abstände der Nadeln können dabei durchaus ein Niveau erreichen, welches auch für die Abstände der Interconnects infrage kommt. Wir sprechen hier also von wenigen Dutzend Mikrometern.

In der Sortieranlage findet noch kein Binning statt. Über das Testen jedes einzelnen Chips stellt Intel bereits an dieser Stelle sicher, dass nur funktionsfähige und solche, die alle vorher definierten Spezifikationen erfüllen, in das Packaging gehen. Nach dem Testen werden die Chips auf Rollen (Tray to Tape Reel) gepackt, auf denen sie dann wiederum zum Packaging transportiert werden.

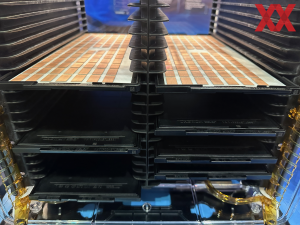

Im Prozess des Die Sort und Die Preparation sind zwei Dinge nicht zu unterschätzen: Erstens verarbeitet Intel pro Tag mehr als 1.000 Wafer in seinen Anlagen in Malaysia. Je nach Größe der einzelnen Chips sprechen wir von ein paar Dutzend oder bis zu hunderten Chips pro Wafer. Entsprechend viele Chips müssen durch die Sortier- und Testanlage. Hunderte Tester prüfen die Chips und nur über derart viele parallelisierte Prozesse kann Intel überhaupt den gewünschten Output erreichen. Überwacht werden die Tester von mehreren Operatoren, die an ihrem Arbeitsplatz etwa 300 der SDX-Tester überwachen. In einer Einrichtung wie KM1 stehen mehrere Hundert SDX-Tester, die parallel arbeiten und natürlich auch nicht alle eine Art von Chips testen. Zusammengefasst sind diese zu einer SDX-Einheit. Jede Einheit besteht aus 20 individuellen Testern und selbst in einer solchen Gruppe können unterschiedliche Arten von Chips getestet werden.

Um den Zufluss an Chips nach der Vereinzelung zu den SDX-Testern zur gewährleisten, betreibt Intel ein automatisches Transport- und Lager-System. In 10.000 Boxen befinden sich jeweils bis zu 30 Trays mit den Chips darauf. AGVs (Automated Guided Vehicles) fahren durch die Halle, nehmen die Boxen aus dem Lager oder direkt von der Vereinzelung und bringen diese zu den SDX-Einheiten. Von dort werden sie nach dem Testen auch wieder aufgenommen und dem schon erwähnten "Tray to Tape Reel"-Prozess zugeführt.

Alle diese Tester entwickelt und fertigt Intel zudem auch noch selbst. Auch dies geschieht in Malaysia, aber dazu kommen wir später noch. Die Chips befinden sich nun also auf den Rollen und können zur Assembly-Linie gebracht werden, wo dann ein Prozessor aus ihnen wird.

PGAT: Penang Assembly und Test

Assembly und Tests sind die nächsten Schritte, in denen aus einem Chip dann ein Prozessor wird. Die Chips werden auf Rollen angeliefert. Im Falle von Meteor Lake kommt das bereits gefertige Foveros-Package aus dem US-Bundesstaat Oregon, da in Malaysia noch kein Advanced Packaging stattfindet. Aber beispielsweise die Raptor-Lake-Prozessoren können in hier in Penang zu einem kompletten Package verarbeitet werden. Die Chips kommen aktuell noch aus Oregon und werden dort in der Testproduktion in Intel 7 gefertigt. Für Meteor Lake findet die Massenprodktion der Compute Tiles dann in Irland statt, sie gehen dann für das Foveros-Packaging nach Oregon und landen für den finalen Assembly-Schritt in Malaysia.

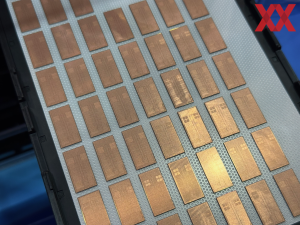

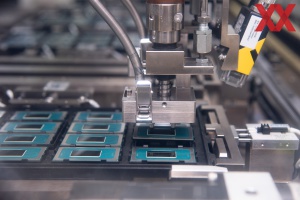

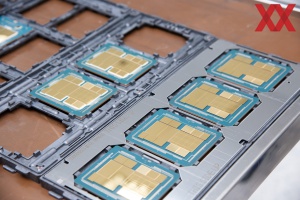

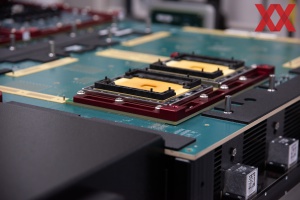

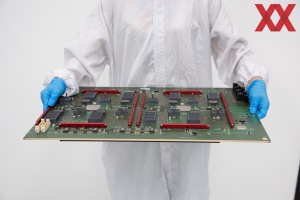

Per Pick&Place-Machine werden die Chips von den Rollen aufgenommen und auf das Package-Substrat gesetzt. Wir haben dies im Falle eines Sapphire-Rapids-Prozessors verfolgen können. Bis die vier Tiles sich auf dem Substrat befinden, vergeht einiges an Zeit. Nach dem Platzieren der Chips und der optischen Prüfung, ob sich diese an der richtigen Stelle befinden, findet durch Erwärmung ein Verlöten statt. Anschließend wird der Raum unter den Chips mittels Epoxidharz verfüllt. Auch dieser Prozess nimmt einiges an Zeit in Anspruch. Die entsprechenden Maschinen können mit einer oder zwei Düsen arbeiten und bringen das Epoxidharz neben dem Chip auf – meist nur auf einer Seite. Das Harz läuft dann unter den Chip und verfüllt diesen.

Sind der oder die Chips mit dem Package-Substrat vereint, kann der Heatspreader aufgebracht werden. Dies geschieht aber nicht für die Notebook-Prozessoren, da diese ohne Heatspreader verbaut werden. Eine geringere Bauhöhe ist der Hauptgrund dafür, dass bei diesen Prozessoren auf einen Heatspreader verzichtet wird. Auf dem Package-Substrat, neben dem Chip, wird ein Silikonkleber aufgebracht, der letztendlich dafür sorgen soll, dass der Heatspreader an seinem Platz bleibt. Je nachdem ob Chip und Heatspreader verlötet werden, wird dann das TIM (Thermal Interface Material), also entweder eine Wärmeleitpaste oder das Löt-Material (meist Indium) aufgebracht. Im Falle eines verlöteten Prozessors müssen die Chip-Oberfläche und die Unterseite des Heatspreaders noch vorbereitet werden. Eine dünne Goldschicht sorgt dafür, dass sich alle Materialien im Löt-Vorgang auch gut miteinander verbinden.

Es folgt ein Burn-in-Test, in dem die Prozessoren hohen Temperaturen und Spannungen ausgesetzt werden um zu prüfen, ob es im Rahmen des Packaging zu einem Defekt gekommen ist.

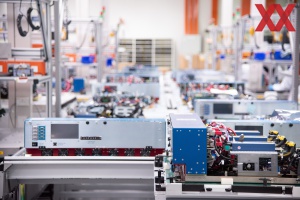

Anschließend prüft ein Test die volle Funktionalität des Chips. Eine weitere Platform Performance Validierung (PPV) geht dabei auf ein ähnliches Level an Funktionstests, wie es der Prozessor dann letztendlich beim Kunden und Nutzer auch sehen wird. Es geht also darum, den Prozessor in einer Software- und Betriebsparameter-Umgebung zu testen, die möglichst nahe an der späteren Realität ist. Auch diesen Tester entwickelt und fertigt Intel in Malaysia.

In der PPV findet dann auch der letzte Schritt statt: Der Prozessor wird zu einem konkreten Modell. Über Fuses wird festgelegt, welcher Funktionsumfang aktiv sein soll – beispielsweise wie viele Kerne verwendet werden. An dieser Stelle erfolgt auch das Binning, also die Festlegung des maximal möglichen Taktes und damit eine weitere Modelleinordnung. Nach der Bestimmung des jeweiligen Modells folgt die Lasergravur auf der Oberseite des Heatspreaders. In Trays verpackt werden die Prozessoren dann weitergeschickt. Großkunden erhalten die Prozessoren in Trays. Sollen sie in den Einzelhandel, muss eine Verpackung und eventuell ein Kühler hinzukommen. Ein Retail-Packaging findet in Malaysia aber nicht statt.

Failure Analysis Lab

In der Fertigung von mehreren Millionen Prozessoren kommt es natürlich auch zu Fehlern. Eben diesen auf den Grund zu gehen, ist die Aufgabe des Failure Analysis Lab. Hier werden verschiedene Methoden der Analyse angewendet. Dies reicht von zerstörungsfreien Analysen mittels Infrarotkamera oder Ultraschall über das Zerschneiden des Chips und der Untersuchung mittels Mikroskop.

Auch Stichproben aus der Fertigung werden im Failure Analysis Lab beprobt, sodass proaktiv gegen eventuelle Fehler in der Fertigung gearbeitet werden kann. Ist der Fehler gefunden, kann es an dessen Behebung gehen.

Neben der Untersuchung des Packages kann in Penang auch ein Debugging auf Transistor-Ebene stattfinden. Das heißt, die entsprechenden Bereiche im Chip werden per Ionenstrahl freigelegt und es können andere Routen aufgebracht werden. Beide Prozessschritte setzen natürlich größte Präzision voraus, denn schließlich reden wir von Reparaturarbeiten im Mikro- und Nanometer-Bereich. Aber so ist es möglich, gewisse Fehler im Design zu beheben, dieses weiter zu testen, eventuell vorhandene Fehler zu sammeln und diese allesamt in einer neuen Revision zu beheben. Bei mehr als einem Dutzend Metalllayern und mehreren Milliarden Transistoren kann sowohl die Fehlersuche als auch das Beheben dieser Fehler natürlich extrem komplex sein.

Im Failure Analysis Lab sind wir übrigens auf einen Tray gestoßen, der offensichtlich Chips der nächsten Arc-Generation enthalten hat – zumindest hatte man bereits entsprechende Chips in der Analyse, die als "BMG G10" klar daraufhin deuten.

Aktuell fährt die Massenproduktion von Meteor Lake hoch. Als Meteor Lake-P werden wir diese Prozessoren vermutlich zum Jahreswechsel in den ersten Notebooks sehen. Entsprechend viele Tests werden für Meteor Lake durchgeführt, wenngleich Intel womöglich an dieser Stelle zeigt, was bereits vor einigen Monaten durch die Labore ging. Ein "MTL682_C0" in der Software einer der Teststationen bestätigt das bereits Bekannte: Meteor Lake wird in einer Version erscheinen, die sechs Performance-Kerne, acht Efficiency-Kerne und eine GT2-Gafikeinheit enthält. Entsprechend der bereits bekannten Nomenklatur aus den vorherigen Generationen wird dies ersichtlich. Interessant an der Stelle ist, dass es sich um eine Revision C0 handelt und es hier also offenbar keine größeren Probleme im Post-Silicon-Prozess gab.

SIMS: Intel System Integration and Manufacturing Services

Im Rahmen von DSDP sowie Assembly und Test kommen Maschinen zum Einsatz, die Intel nicht bei einem Zulieferer bezieht, sondern selbst entwickelt. Dies geschieht größtenteils in Kulim, einer Einrichtung auf dem Festland von Malaysia – System Integration and Manufacturing Services (SIMS) nennt sich diese Abteilung.

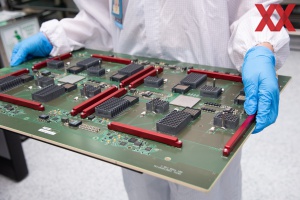

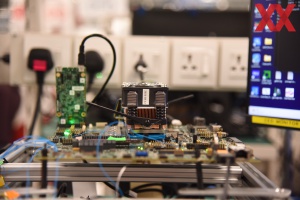

SIMS ist unter anderem verantwortlich für die Entwicklung der Mainboards für die Reference Validation Platform (RVP). Dabei handelt es sich unter anderem um die Mainboards, die dann z.B. im Design und Development Lab zum Einsatz kommen. Auch das Failure Analysis Lab verwendet teilweise diese Mainboards.

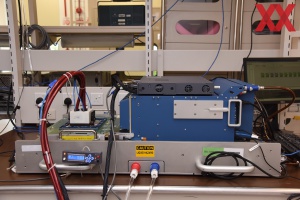

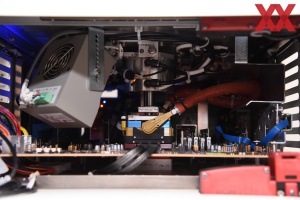

Während die Entwicklung spezieller Mainboards, die schon recht nahe an den Produktionsvarianten sein können, noch vergleichsweise einfach ist, gilt dies für die Entwicklung, Fertigung und Reparatur der Tester nicht. Es handelt sich dabei um Systeme und Einzelkomponenten, die extrem komplex aufgebaut und mehrere hundert Kilogramm wiegen können.

Im Bereich des Die Sort und Die Prep kommen High Density Modular Tester (HDMT) zum Einsatz. Diese bestehen aus einer Kontrolleinheit und den im entsprechenden Abschnitt beschriebenen Probing Cards.

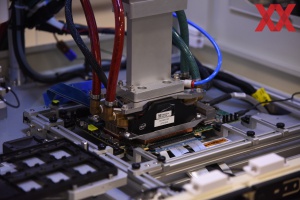

In den finalen Schritten von Assembly und Test zum Einsatz kommen die High Density Burn-in Tester (HDBI). Auf ihnen wird das bereits fertige Package getestet, um so letzte Probleme jedes einzelnen Prozessors zu erkennen.

SIMS ist demnach ein integraler Bestandteil in der Fertigung bei Intel – und das weltweit für alle Fabs (Fertigung von Wafern) und sonstige Einrichtungen, in denen Chips oder Prozessoren als fertiges Package getestet werden müssen. Dabei muss Intel hier nicht nur die Hardware und gesamten Systeme entwickeln und fertigen, sondern sich auch überlegen, wie die schnell einige Kilogramm schweren Einzelkomponenten und später mehrere hundert Kilogramm schweren Tester gehandhabt werden.

Design und Development Lab

Intel hat weltweit mehrere Designcenter, in denen die unterschiedlichen IP-Blöcke (CPU-Kerne, ein SoC-Design, Chipsätze, GPUs, USB, Thunderbolt, …) entwickelt werden. Auch in Malaysia gibt es ein Design und Developement Lab. Hier fand unter anderem die Post-Silicon-Validierung der Efficiency-Kerne der nächsten Generation (Crestmont) statt.

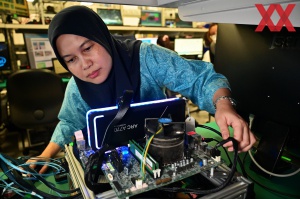

Analog zu dem, was wir im vergangenen Jahr in Israel zu Raptor Lake gesehen haben, wurde in Penang aber auch Meteor Lake als komplette Plattform getestet. Bring-Up und die erste Phase der Post-Silicon Validation sind in Anbetracht der Vielfalt und Komplexität, in der sich der Prozessor später bewähren muss, extrem schmal gehalten. Sobald die Prozessoren sozusagen aus dem Gröbsten heraus sind, geht es einen Schritt weiter.

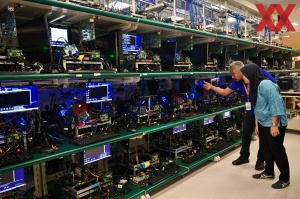

Hier geht es dann darum, die komplette Plattform zu testen. So unterstützten die Meteor-Lake-Prozessoren offensichtlich DDR5 sowie PCI-Express 5.0. Dies alles muss natürlich getestet werden – mit unzähligen Möglichkeiten an unterschiedlicher RAM-Bestückung und einer nicht weniger komplexen Vielfalt an PCIe-Geräten und vielem mehr. USB, die integrierte GPU, die dazugehörigen Videoausgänge, Temperaturabhängigkeiten, das Verhalten mit unterschiedlichen Ausbaustufen an Strom- und Spannungsversorgungen – man kann sich sicherlich vorstellen, wie komplex solche Tests werden können. Dies ist auch der Grund dafür, warum nicht ein paar Dutzend sondern mehrere hundert Teststationen im Labor in Penang stehen, auf denen die meisten dieser Kombinationen getestet und geprüft werden sollen.

Intel Malaysia wächst weiter

Intel hat große Ausbaupläne für seine beiden Standorte in Malaysia. In Penang und Kulim befinden sich bereits jeweils eine "Assembly und Test"-Anlage (PGAT und KuAT). Hinzu kommt die bereits bestehenden "Kulim Die Sort Die Prep"-Anlage (KMDSDP) in Kulim. System Integration und Manufacturing (SIMS) ergänzt diese drei Anlagen – hinzu kommen die beschriebenen Design, Development und Failure Analysis Labs.

Derzeit im Bau befindet sich eine Einrichtung für das Advanced Packaging, die in Penang entsteht. Der Rohbau für die Pelican getaufte Anlage entsteht aktuell. Der Einbau der Anlagen für das Advanced Packaging wird aber die weitaus größere Herausforderung sein. Mit einer Inbetriebnahme von Pelican ist frühestens 2025, wohl eher 2026 zu rechnen.

Im Kulim-Standort wird eine weitere "Assembly und Test"-Anlage aufgebaut, die unter dem Namen Falcon entsteht. Durch die etwas einfacheren Verfahren dort ist davon auszugehen, dass Falcon weitaus früher fertiggestellt werden kann.

Intel benötigt hohe Packaging-Kapazitäten

Xeon Sapphire Rapids, Ponte Vecchio – was Intel aktuell im Bereich des Advanced Packaging macht, wird zukünftig nur ein Tropfen auf den heißen Stein sein. Mit Meteor Lake rückt ein Produkt in den Fokus, welches millionenfach verkauft werden soll und daher auch in entsprechenden Stückzahlen gefertigt werden muss. Der Standort bei Oregon ist nicht in der Lage, diese Stückzahlen zu bedienen. Im US-Bundesstaat New Mexico entsteht aktuell eine weitere Anlage für das Advanced Packaging. Diese sollte im kommenden Jahr in Betrieb gehen und für deutlich mehr Durchsatz in diesem Segment sorgen können. Der Ausbau der Kapazitäten wird aber weitergehen, denn Intel will im Rahmen seiner Intel Foundry Services (IFS) nicht nur die Fertigung, sondern auch das Advanced Packaging externen Kunden anbieten.

Zudem soll nicht nur im deutschen Magdeburg eine moderne Fab entstehen, sondern quasi direkt daneben in Polen eine Einrichtung für 5,6 Milliarden US-Dollar, die ebenfalls für das Advanced Packaging vorgesehen ist.

Meteor Lake ist wie gesagt nur der Anfang. Arrow Lake und Lunar Lake auf der Client-Seite werden folgen und setzen ebenso auf das Advanced Packaging wie alle zukünftigen Xeon-Prozessoren wie beispielsweise Emerald Rapids, Sierra Forest und Granite Rapids.

In Anbetracht der vielen geopolitischen Abhängigkeiten sei an dieser Stelle aber auch erwähnt, dass Malaysia und China extrem eng verflochtene wirtschaftliche Beziehungen pflegen. China investiert großflächig in gigantische Infrastrukturprojekte – so zum Beispiel eine Brücke zwischen Penang und Festland-Malaysia sowie Bauprojekte in Penang. China will sich damit einen gewissen Einfluss sichern, allerdings werden diese Bestrebungen auch in Malaysia nicht ganz kritikfrei hingenommen.

Wir aber wollen uns zum Abschluss noch einmal auf die Technik und das Gesehene konzentrieren. Die Dimensionen solcher Anlagen sind immer wieder beeindruckend und lassen uns auch besser verstehen, warum diese Dimensionen notwendig sind, wenn Millionen an Prozessoren gefertigt werden sollen. Bevor es aber dazu kommen kann, werden gigantische Summen investiert – auch dies wird nach unserem Besuch deutlicher denn je.