Werbung

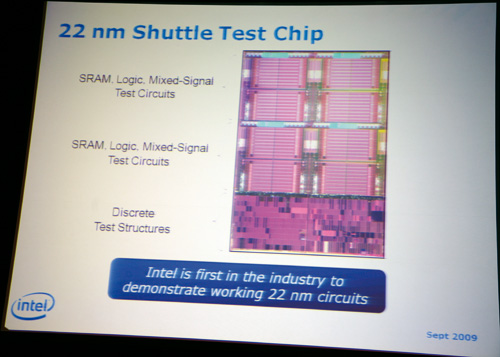

In einer Technologie-Einführung zur 22-nm-Technik gab Marc Bohr weitere Informationen zur kommenden Intel-Fertigungstechnik. Der bereits in der Keynote gezeigte 22-nm-Test-SDRAM-Chip besitzt eine 364 MBit Array Size mit 2,9 Milliarden Transistoren. Er basiert auf der dritten Generation der High-K- + Metal-Gate-Technik. Intel verwendete auf dem Chip zwei verschiedene SRAM-Zellen, eine mit 0,092 um für High-Density-Applications und eine weitere mit 0,108 um für Low-Power-Applications. Erstmals verwendete Intel auf dem Testchip auch I/O Circuits, um die Fertigungstechnik für kommende Mikroprozessoren besser validieren zu können.

Der P1270 genannte Prozess wird für CPUs vorgesehen, für SoC-Produkte wird Intel einen weiteren Prozess (P1271) verwenden, der auf niedrige Leakage ausgelegt ist und somit weniger Energie verbrauchen wird. Dieser Prozess ist für die Atom-Prozessorserie vorgesehen. Für die Fertigung verwendet man größtenteils die Tools der bisherigen Fertigungstechnik. Die Umrüstung der bisherigen 32-nm-Fabriken wird somit beschleunigt, zudem kann Intel den neuen Prozess mit relativ geringen Zusatzkosten einführen. Es wird weiterhin die 193 nm Litographie verwendet. Intel geht davon aus, den 22-nm-Prozess mit der selben schnellen Geschwindigkeit auf den Markt bringen zu können, wie zuletzt die 45-nm-Technik, und auch wie die kommende 32-nm-Technik. Die Wafergröße bleibt beim 22-nm-Prozess weiterhin bei 300 mm. Intel geht davon aus, dass erst zur 15-nm-Generation (ab 2015) größere Wafer eingesetzt werden. Zur 15-nm-Technik möchte Intel auch gerne die ELV-(Extreme Ultriviolet)-Litographie einsetzten, aber man befürchtet, dass man bis dahin mit dieser neuen, herausfordernden Technik nicht einsatzbereit ist. Somit sieht man die ELV-Litographie erst für die 11-nm-Technik vor.

Die interessanten Infos, wie Voltages, Gate Length und weitere Details wollte Marc Bohr noch nicht preisgeben - diese Infos möchte man sich für spätere Pressetermine aufheben.