Werbung

In einem Briefing zur 32-nm-SOC-(System-on-a-Chip)-Technik gab Marc Bohr einige Details zu Intels SOC-Plänen in den kommenden Monaten preis. Intels SOC-Fertigung unterscheidet sich dabei hauptsächlich hinsichtlich der Optimierung für eine niedrige Leakage und eine hohe Packdichte sowie niedriger Spannung von dem 32-nm-Prozess der normalen Prozessoren. Intel bietet hier einen Mix für verschiedene SOC-Produkte an, um durch die Fertigung ein Optimum für den späteren Einsatz des Produktes zu bieten.

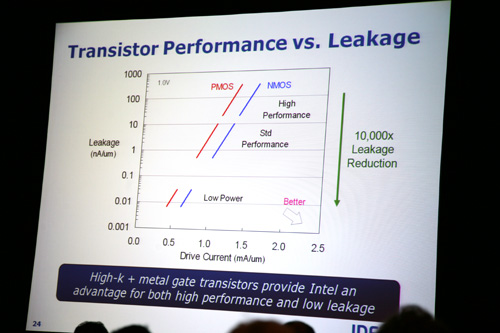

Insbesondere durch eine Reduzierung der Leakage kann Intel mit Low-Power-Transistoren beispielsweise für CE-Produkte SOCs für niedrigen Stromverbrauch produzieren. Die 32-nm-Technik mit High-k-und Metal-Gate-Fertigung ist dabei ein Aspekt, man verwendet aber auch verschiedene Metalllagen für die SOC-Fertigung. In der Regel sind die oberen CPU-Layers dicker, um möglichst hohe Transistorperformance zu erreichen (hohe Taktraten). Bei SOCs ist dies nicht unbedingt notwendig, daraus ergibt sich die Möglichkeit, die Lagen dünner zu gestalten und somit den Energieverbrauch zu minimieren.

Im Vergleich zur 45-nm-SOC-Fertigungstechnik konnte die Frequenz bei gleicher Leakage mit dem 32-nm-SOC-Prozess um 22% gesteigert werden.

Bohr gab auch einen Ausblick auf die kommende 22-nm-SOC-Fertigung mit dem Namen P1271. Auch diese unterscheidet sich signifikant von der verwendeten Technik für die 22-nm-CPU-Fertigung (P1270). Beim kürzlich vorgestellten 22-nm-Test-Chip testete man bereits indirekt die 22-nm-SOC-Fertigung, da man unterschiedliche SRAM-Zellen auf dem Test-Chip erstellte, insbesondere die 0,1802 um SRAM-Zellen.