Werbung

Mit der Verabschiedung des finalen Standards für DDR5 steht dem nächsten großen Wechsel im Bereich dieser Technik nun nichts mehr im Wege. Ohnehin haben die DRAM-Hersteller bereits über Monate kräftig die Werbetrommel gerührt und die Massenproduktion entsprechender Chips angekündigt. Nun sind die Weichen endgültig für eine Markteinführung in 2021 gestellt.

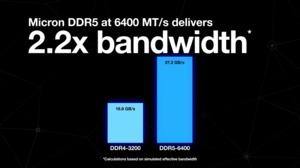

DDR5 soll in vielerlei Hinsicht Verbesserungen gegenüber dem aktuellen DDR4 bieten. Die maximale Datenrate soll von DDR4-3200 auf DDR5-6400 verdoppelt werden. SK Hynix sprach sogar schon über DDR5-8400, wenngleich es sich dabei aber sicherlich um einen Ausblick auf Lösungen handelt, die genau wie aktuell schnellerer Speicher oberhalb des spezifizierten Spektrums angesiedelt sind. Außerdem soll DDR5 die Kapazität pro DRAM-Chip und Speichermodul weiter erhöhen. 64 GBit pro DRAM-Chip und bis zu 2 TB pro Speichermodul nennen die Spezifikationen. Diese Maximalkapazitäten werden sicherlich nicht zum Start von DDR5 zur Verfügung stehen.

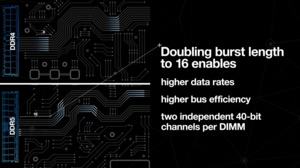

Um den DDR5-Speicher schneller und flexibler zu machen, wird ein Speichermodul künftig über zwei Kanäle angesprochen. Damit umgeht man das Problem, dass sich der eigentliche DRAM-Speicher gar nicht so hoch takten lässt, um die gewünschten Datenraten zu erreichen. Wie in einem RAID0 für Festplatten und SSDs wird ein DDR5-Modul also über zwei jeweils 32 Bit (2x 40 Bit mit ECC) breite Datenkanäle angesprochen. DDR4 arbeitet mit einem 64 Bit breiten Bus. Diesen Dual-Channel-Betrieb von DRAM kennt man jedoch schon von LPDDR4 und GDDR6, wo ähnlich vorgegangen wird – auch um die eigentliche Limitierung des DRAM-Speichers zu umgehen.

Mehr Daten parallel übertragen zu können ist der Eine, den Bus als solches schneller machen zu können der zweite Punkt. Dazu kommt die Decision Feedback Equalization (DFE) zum Einsatz. Dabei handelt es sich um dedizierte Schaltkreise, welche die Signalintegrität verbessern sollen. Im Grunde bleibt man bei der selben Bus-Struktur wie bei DDR4, setzt aber engere Toleranzen an. Um diese einhalten zu können, gibt es die DFE.

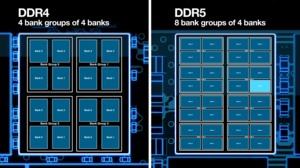

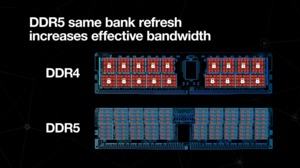

DDR5-Module bieten zudem die Möglichkeit, aus 32 Banks – bestehend aus acht Bank Groups (8x4) – aufgebaut zu sein. Dies bedeutet eine Verdopplung gegenüber DDR4, wo nur 16 Banks in 4x4 oder 2x8 Groups angesprochen werden können. Außerdem wurde die Burst Length (BL) von acht auf 16 verdoppelt, was den Zugriff auf den Speicher deutlich beschleunigt. DDR4 kann während einer Refresh-Operation keinerlei weitere ausführen. DDR5 unterstützt ein Same Bank Refresh, was bedeutet, dass Banks eine Refresh-Operation ausführen können, während auf anderen Banks andere Operationen laufen können.

DDR5-DIMMs: 288 Pins, eigene Spannungsversorgung und Temperatursensoren

Trotz zweier Kanäle und einem schnelleren Bus: Es bleibt für die DDR5-DIMMs bei 288 Pins. Allerdings sind die Pin-Outs völlig unterschiedlich. Anstatt 24 ADD/CMD-Pins gibt es nur noch 2x 7 Pins. Dafür wird der Data-Bus von 40 + 32 Pins auf 2x 40 Pins erweitert. SPD- und VREF-Pins gibt es it DDR5 nicht mehr. Stattdessen bieten DDR5-DIMMs einen I2C- und I3C-Bus.

Mit DDR5 wird die Spannung für den Betrieb des Speichers von 1,2 auf 1,1 V gesenkt. Damit wird vor allem die Effizienz des Speichers gesteigert. Viel wichtiger ist jedoch, welche Änderungen hinsichtlich der Spannungsversorgung vorgenommen werden. Die Spannungsregulierung von DDR5 erfolgt nicht mehr über das Mainboard, sondern über eine integrierte Spannungsregulierung auf dem DDR5-DIMMs selbst. Dies gilt außerdem für UDIMMs und LRDIMMs.

Die Komplexität wird in gewisser Weise verlagert. Musste das Mainboard je nach Plattform dazu ausgelegt sein bis zu 16 DIMMs versorgen zu können, wandert dies Komplexität nun auf die DIMMs selbst. Die Mainboards sollten dadurch etwas günstiger werden, wer viel Speicher einsetzt bezahlt die teureren DDR5-DIMMs. Ob sich die Kosten dieser Maßnahmen nachvollziehen lassen, lässt sich nur schwer sagen. Die Integration der Spannungsregulierung bietet in jedem Fall das Potenzial für eine höhere Effizienz des Speichers selbst.

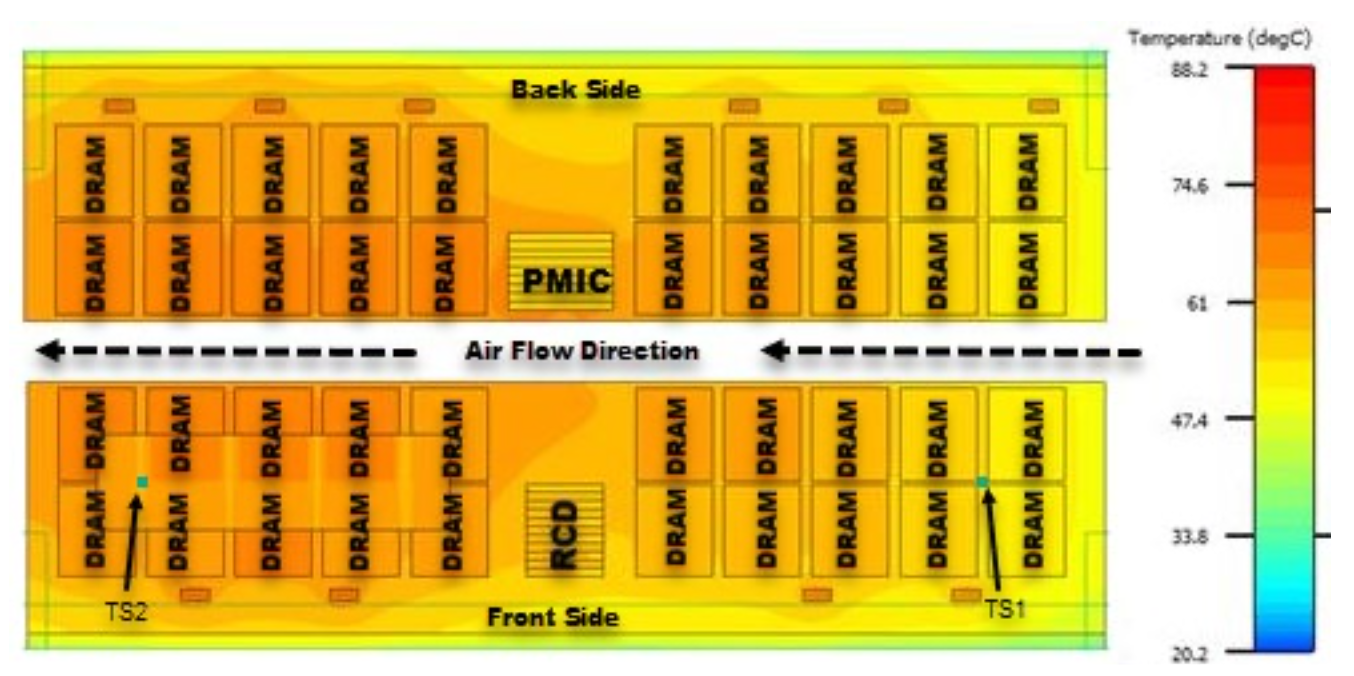

DDR5-DIMMs sehen mindestens zwei Temperatursensoren vor. Diese sollen vor allem im Server dazu beitragen zu hohe Temperaturen frühzeitig zu erkennen. DDR4-DRAM bzw. -DIMMs sind teilweise schon mit Sensoren ausgestattet. Für DDR5 sind diese in den JEDEC-Spezifikationen festgeschrieben.

Das Sampling läuft bereits

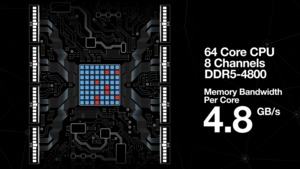

Alle großen Speicherhersteller haben bereits mit dem Sampling von DDR5 begonnen. Bei AMD, Intel und Co. dürften bereits die ersten Prozessoren mit DDR5 in den Laboren laufen. In den kommenden zwölf bis 18 Monaten sollen die ersten Prozessoren mit Unterstützung von DDR5 auf den Markt kommen. Bei Intel sind dies die Xeon-Prozessoren auf Basis von Sapphire Rapids. Bei AMD die EPYC-Modelle auf Basis des Genoa-Designs mit Zen-4-Kernen. Datacenter-Prozessoren auf Basis eines ARM-Designs werden ebenfalls in diesem Zeitraum auf DDR5 wechseln. Kandidaten sind hier die zukünftigen Ampere-Prozessoren. Aber auch Apple dürfte mit seinen eigenen Chips bereits DDR5 ins Auge gefasst haben.