Die Veröffentlichung des Programms der 2024 IEEE International Solid-State Circuits Conference (ISSCC) offenbart einige Details zu den geplanten Vorträgen. Aus dieser Vor-Veröffentlichung stammen die ersten Informationen zum schnelleren GDDR7, der ebenfalls dort vorgestellt werden soll.

Auch ein weiterer Vortrag sorgt bereits für großes Interesse: "A 280-Layer 1Tb 4b/cell 3D-NAND Flash Memory with a 28.5Gb/mm² Areal Density and a 3.2GB/s High-Speed IO Rate"

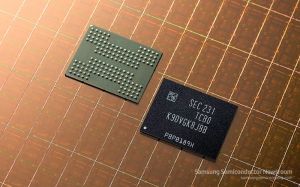

Samsung wird also die nächste Generation seines NAND mit 280 Lagen vorstellen, der als QLC vier Bit pro Speicherzelle speichern kann und eine Speicherdichte von 28,5 GBit/mm² erreichen soll. Damit würde man an Hersteller wie Intel, Sk hynix, Kioxia und YMTC wieder vorbeiziehen. Auf QLC-Zellen bezogen wäre man neuer Spitzenreiter.

NAND-Flash Speicherdichte

TLC, QLC und PLC

Werbung

Der Werte für Intels 192L PLC und den 300L+-TLC von Sk hynix sind nicht bestätigt. Einige Datenpunkte stammen direkt vom Hersteller, aber auch ComputerBase diente uns als Quelle.

Mit 3,2 Gbit/s wäre der QLC mit 280 Lagen aber nicht nur in der Flächendichte gut positioniert, sondern auch hinsichtlich seiner Geschwindigkeit.

Mehr Lagen bedeuten eine immer größere Speicherdichte. In den im Datacenter üblichen Formfaktoren sind bereits 61,44 TB und mehr möglich. Allerdings wird die Fertigung immer komplexer und im Falle des QLC geht es auch darum, dass die Schreibraten mithalten können müssen. Mit 3,2 GBit/s für den V9 VNAND ist Samsung hier aber auf gutem Wege.

Auf der ISSCC, bzw. im Vortrag wird Samsung weitere Details zum NAND mit 280 Lagen bekanntgeben.