Werbung

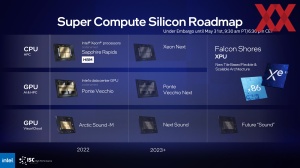

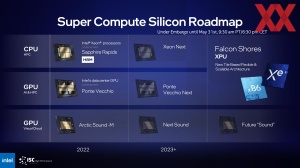

Zur International Supercomputing Conference (ISC) sprach Intel über einige Details seiner Roadmap, die man bisher noch unter Verschluss gehalten hatte. Genauer gesagt hat man den Namen und erste Details zum Nachfolger des Xe-HPC-Beschleunigers Ponte Vecchio (PVC) preisgegeben, der in der Tradition der Benennung durch Brücken in Venedig – Rialto Bridge – heißen wird. Neben dem Namen gab es erste interessante Einblicke in die technischen Details.

Für die zweite Jahreshälfte 2022 sind die Ponte-Vecchio-Beschleuniger angekündigt worden. Sie sollen sowohl in Supercomputern zu Dutzenden, Hunderten oder gar Tausenden zum Einsatz kommen, aber auch über die OEMs und SIs erhältlich sein. Bislang haben wir allerdings PVC noch nicht in freier Wildbahn gesehen.

Intel sieht Ponte Vecchio als Tock, denn es handelt sich um das erste Produkt einer komplett neuen Serie – hinsichtlich der Architektur und natürlich dem Packaging. Den Nachfolger Rialto Bridge sieht man als Tick, der nur kleinere Verbesserungen erfahren wird, dessen grundsätzlicher Aufbau jedoch beibehalten wird. Genauer wird Intel an dieser Stelle allerdings nicht. Einzig die Anzahl der Xe-Cores wird mit derer 160 genannt – ausgehend von 128 für Ponte Vecchio. Intel will außerdem im Packaging einige Veränderungen vornehmen, die Rialto Bridge hinsichtlich der Fertigung der einzelnen Chiplets und des Packaging ausbalancieren. Zwar sind die einzelnen Chiplets, oder wie Intel sie nennt Tiles, relativ einfach zu fertigen, dafür aber hat Intel die Komplexität in das Packaging verschoben.

Neben der größeren Anzahl an Xe-Cores – unbekannt ist hier, ob diese auf der zweiten Generation der Xe-HPC-Architektur basieren werden – nennt Intel größere Fähigkeiten im Hinblick auf die I/O-Funktionen und einen neuen Formfaktor der OAM-V2-Karten (OCP Acceleration Module). Diese sollen eine höhere Leistungsaufnahme der darauf eingesetzten Chips ermöglichen.

Mit Rialto Bridge wird Intel auf unterschiedliche Fertigungsgrößen und unterschiedliche Fertiger zurückgreifen. Es werden also auch hier nicht alle Chips In-House gefertigt. Vermutlich wird TSMC wieder einen Teil beisteuern.

Für Mitte 2023 erwartet Intel die Einführung von Rialto Bridge. Ob man diesen Zeitplan in Anbetracht der aktuellen Verschiebungen von Ponte Vecchio so wird einhalten können, bleibt offen. Die Chips sollen in bestehende OAM-Boards passen, bzw. zu diesen kompatibel sein. Allerdings sieht Intel mit Rialto Bridge eine höhere Leistungsaufnahme vor. Dies muss dann natürlich bei einem Wechsel des Chips bedacht werden. Die volle Leistung wird Rialto Bridge also nur im OAM-V2-Format erreichen.

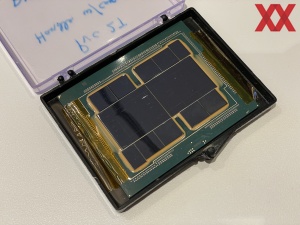

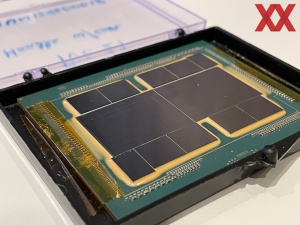

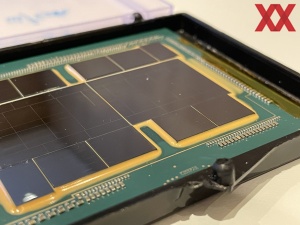

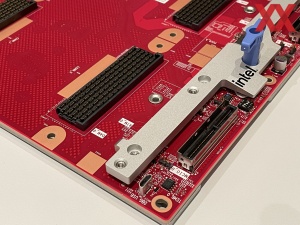

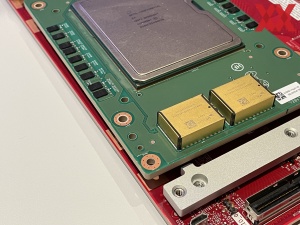

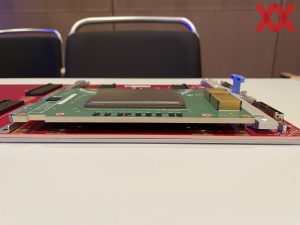

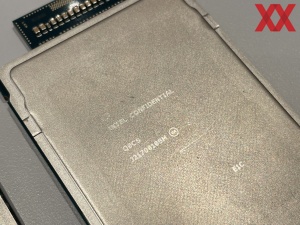

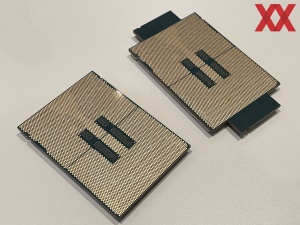

Auf der ISC hatten wir die Gelegenheit, uns ein Package von Ponte Vecchio genauer anzuschauen. Einmal haben wir hier das reine Package mit seinen 63 Tiles – davon 41 aktiv. Aber wir sehen auch das komplette OAM-Modul, welches deutlich weniger komplex ist, als die SMX4-Module von NVIDIA. Das Engineering Sample ist beschriftet mit "PVC 2T OAM 600W", was einerseits die TDP-Auslegung von 600 W bestätigt, aber auch das Design bestehend aus zwei Compute-Bereichen, die miteinander verbunden sind. Ursprüngliche plante Intel wohl eine 4T-Variante – also die doppelte Ausbaustufe dessen, was wir hier sehen.

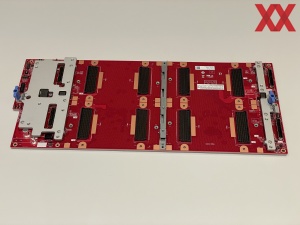

Das OAM-Modul wird dann auf eine Trägerplatine gesetzt, die wie hier abgebildet vier Module aufnimmt. Intel plant solche Platinen allerdings auch mit acht Modulen.

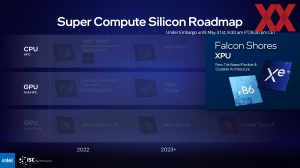

CPUs und GPUs werden zusammengeführt

Auf den Tick in Form von Rialto Bridge wird mit Falcon Shores eine komplett neue Architektur, bzw. ein komplett neuer Aufbau für solche Beschleuniger folgen. Die x86-und Xe-Kerne werden flexibel miteinander kombiniert. Das Verhältnis aus x86- und Xe-Kernen wird vom jeweiligen Anwendungsbereich bestimmt. Intel zeigt hier beispielhaft Falcon-Shores-Chips komplett mit x86-Kernen, solche ausschließlich mit Xe-Kernen aber auch Mischbestückungen.

Die Tiles werden in Intel 20A oder kleiner gefertigt. Das Packaging erfolgt mittels Foveros Direct oder Co-EMIB. Intel erwartet eine Steigerung des Performance/Watt-Verhältnis um den Faktor fünf oder mehr. Mindestens um dieses Niveau soll sich die Leistungsdichte sowie die Speicherbandbreite und Kapazität erhöhen. Das Leistungs- und Effizienzplus lässt sich in der Form aber noch nicht auf die Praxis übertragen, da Intel hier Verbesserungen mit und durch die x86- und Xe-Kerne vermischt.

Die ersten Falcon-Shores-Chips werden nicht vor 2024 erwartet. Interessant wird zudem sein, wie Intel parallel dazu seine Xeon-Produktpalette weiterführen wird. Hier wird es auf die aktuell anstehende Generation Sapphire Rapids die Chips auf Basis von Granite Rapids mit Performance-Kernen geben. Gleichzeitig baut Intel die Xeon-Produktpalette zweigleisig auf und liefert mit Sierra Forrest Xeon-Prozessoren rein mit Efficiency-Kernen.

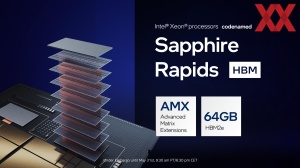

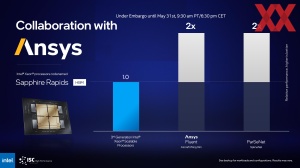

Wenig Neues zu Sapphire Rapids

Recht wenig Neues gibt es zur nächsten Xeon-Generation alias Sapphire Rapids. Intel zeigte nur einige Benchmarks, die das Leistungsplus dank der 64 GB HBM2E unterstreichen sollen.

Intel wollte sich nicht auf einen genaueren Termin für Sapphire Rapids festnageln lassen. Noch immer spricht man nur von der zweiten Jahreshälfte 2022. Die HBM-Versionen sollen zudem weiterhin etwas nach den Standard-Varianten erhältlich sein. Allerdings scheint man den zeitlichen Abstand verkürzt zu haben – ohne diesen genauer zu spezifizieren.

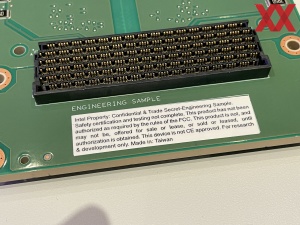

Die Xeon-Prozessoren auf Basis von Sapphire Rapids konnten wir auf der ISC ebenfalls ablichten.

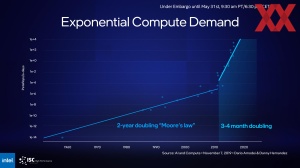

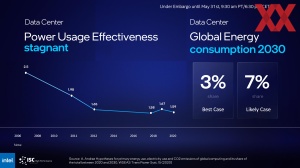

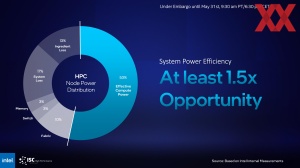

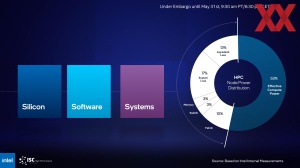

Auch Intel sieht die Effizienz der Hardware im Fokus

Recht eindrucksvoll eroberte der Frontier vor wenigen Tagen den ersten Platz der Top500-Liste. Mit einer Energieeffizienz von 52,23 GFLOPS/W als Gesamtsytem sowie 62,2 GFLOPS/W setzt das System in diesem Segment neue Maßstäbe. An diesem Punkt will Intel ansetzen, denn seit einigen Jahren sieht man sich hier in einem Bereich der Stagnation. Im Jahre 2030 sollen Datacenter für 3 % des Gesamtstromverbrauchs verantwortlich sein – schlimmstenfalls sogar für 7 %.

Hard- und Software sowie der Betrieb des Datacenters sind die Stellschrauben, an denen gedreht werden soll. Auch hier ein Verweis auf die aktuelle Nummer eins, die ihre Prozessoren und GPUs bei 85 °C mit einer Warmwasserkühlung arbeiten lässt. Damit steigt die Effizienz, da keine stromhungrige Kühlung zum Einsatz kommt. Auf der anderen Seiten lassen AMD und das OLCF als Betreiber des Supercomputers einiges an Leistung liegen.