Werbung

Erstmals nennt Intel konkretere Zahlen zur Rechenleistung seines GPU-Beschleunigers Ponte Vecchio und spricht über seine Entscheidungen im Hinblick auf die Größen des Caches. Zur ISC 22 im Frühjahr nannte Intel erste Daten zur Rechenleistung, scheint das Chiplet-Konstrukt nun aber weiter getestet und einen finalen Takt festgelegt zu haben, so dass man für die verschiedenen Genauigkeiten nun weitere Leistungsdaten nennen kann.

Ohne die Werte für FP64, FP32 usw. nun einzeln zu nennen müssen, haben wie die offiziellen Angaben mit denen von NVIDIA zum H100 verglichen:

| Genauigkeit | Ponte Vecchio | H100 |

| FP64 | 52 TFLOPS | 30 TFLOPS |

| FP32 | 52 TFLOPS | 60 TFLOPS |

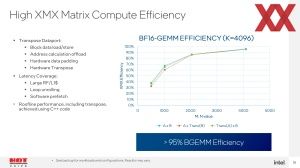

| XMX Float (TF32) / Tensor Cores | 419 TFLOPS | 1.00 TFLOPS |

| XMX BF16 | 839 TFLOPS | 2.000 TFLOPS |

| XMX FP16 | 839 TFLOPS | 2.000 TFLOPS |

| XMX INT8 | 1.678 TFLOPS | 4.000 TFLOPS |

Während Intel mit Ponte Vechhio also für die höchste Genauigkeit mit FP64 die höhere Rechenleistung zu bieten hat, zieht NVIDIA mit dem H100 auf Basis der Hopper-Architektur für die niedrigen Genauigkeiten davon. Dies leisten vor allem die Tensor Cores der vierten Generation, die NVIDIA weiter optimiert hat und die dank Sparsity im Extremfall eine deutliche Beschleunigung erreichen.

Sowohl Ponte Vecchio also auch NVIDIAs H100 arbeiten im OAM-Modul mit einer TDP von mehr als 500 W. NVIDIA peilt für den H100-Beschleuniger 700 W an, bei Intel sind es 600 W.

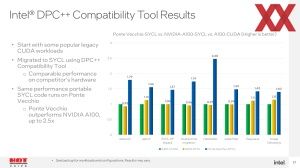

Zwar kann Intel im Rahmen der Präsentation gewisse Vorteil gegenüber der aktuellen Lösung A100 von NVIDIA proklamieren, aber sollte Ponte Vecchio nicht in den kommenden Monaten auf den Markt kommen, hat man es nicht mehr mit dem A100-Beschleuniger zu tun, sondern schon mit dessen Nachfolger H100.

Für Ponte Vecchio verzichtet Intel auf einen L3-Cache, nach dem L2-Cache folgt auf der nächsten Speicherebene der Grafikspeicher und dieser ist bei Ponte Vecchio ein 128 GB großer HBM2E. Die Cache-Hierarchie sieht wie folgt aus:

64 MB an Register File in den Xe-Kernen. Der L1-Cache ist mit 64 MB genauso groß wie die Register File. Die Bandbreite vom für den L1-Cache sinkt aber von 419 auf 105 TB/s über das gesamte Package hinweg. Der L2-Cache bemisst sich mit 408 MB und ist damit im Verhältnis 6:1 größer als der L1-Cache. Dafür gibt es laut Intel gute Gründe, denn einige Anwendungen profitieren deutlich von einem derart großen L2-Cache – andere wiederum nicht. Die Bandbreite für Lesezugriffe sinkt abermals von 105 TB/s im L1-Cache auf 13 TB/s auf den L2-Cache. Von hier geht es dann mit 3,2 TB/s zum HBM2E.

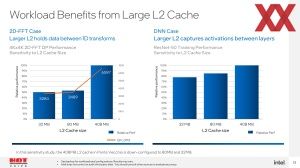

Für zwei Anwendungen zeigt Intel die Auswirkungen des L2-Caches. Für eine 2D-FFT-Netzwerk liegt die relative Rechenleistung mit 80 anstatt 408 MB bei nur noch knapp über 50 % – bei 32 MB ist der Rückgang deutlich geringer. Der große L2-Cache von Ponte Vecchio zahlt sich an dieser Stelle also aus.

Anders sieht dies für ein Deconvolutional Neural Network (DNN) aus. Zwar sinkt auch hier die Rechenleistung um etwa 15 % ab, die Abhängigkeit ist allerdings nicht ganz so groß.

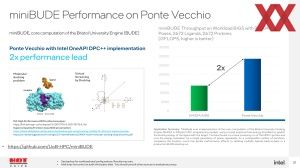

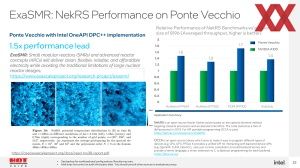

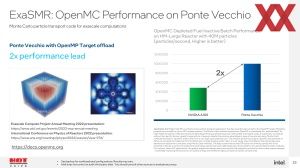

In weiteren Benchmarks will Intel seine Leistungsvorteile gegenüber NVIDIAs A100 demonstrieren. Zum Teil kennen wir diese Werte bereits und einmal mehr sei gesagt: Intel vergleicht den noch immer nicht verfügbaren Ponte-Vecchio-Beschleuniger mit Hardware, die seit zwei Jahren erhältlich ist. Der eigentliche Gegner ist sicherlich NVIDIAs H100 und der Radeon Instinct MI250X von AMD.