Werbung

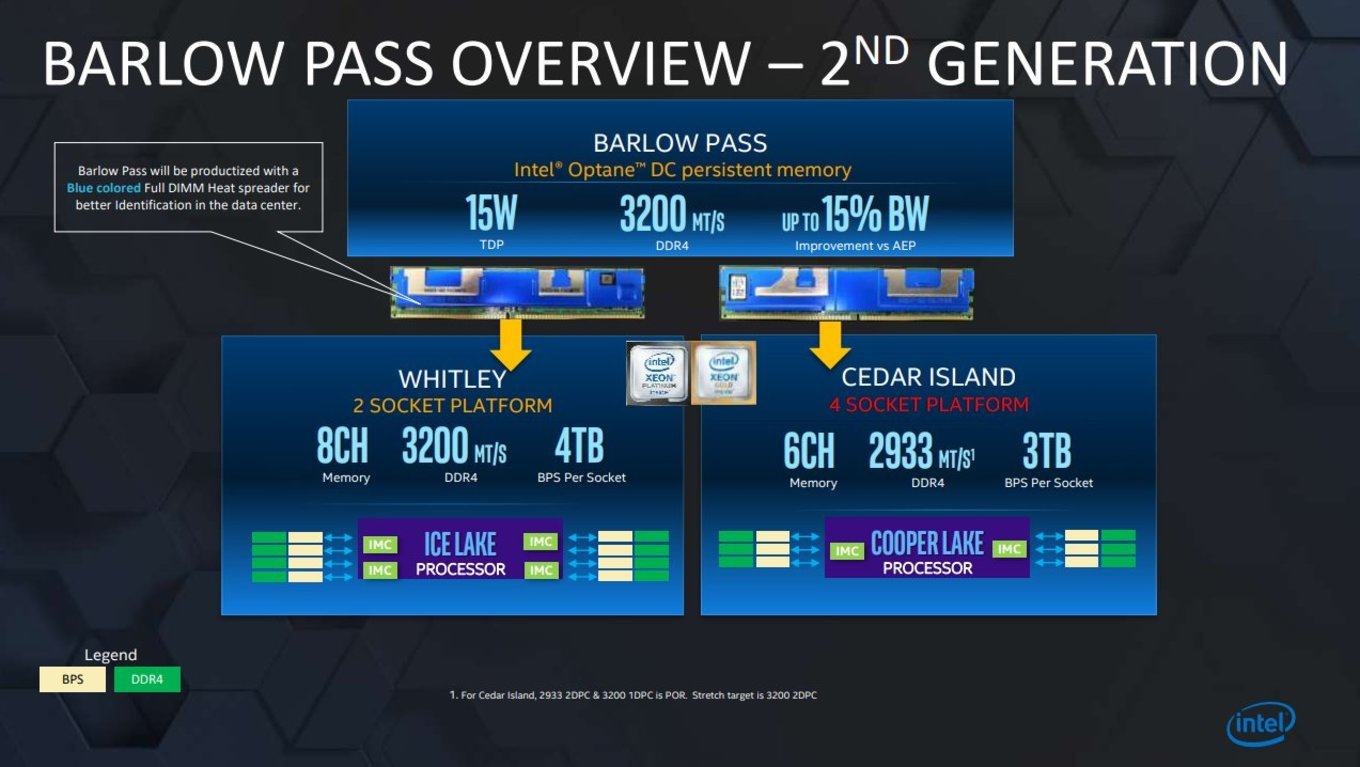

Eine Präsentationsfolie verrät weitere Details zum Optane DC Persistent Memory der zweiten Generation alias Barlow Pass sowie den Xeon-Prozessoren, die diesen verwenden sollen. Twitterer @KOMACHI_ENSAKA hat die bisher unbekannte Folie veröffentlicht.

Auf einem Memory & Storage Day hat Intel im September des vergangenen Jahres über seine zukünftige Speicher-Strategie gesprochen. Thema war damals auch schon die nächsten Generation des Optane DC Persistent Memory, die unter dem Codenamen Barlow Pass geführt wird.

Barlow Pass soll 3200 MT/s erreichen können, während die aktuelle Generation mit 2666 MT/s arbeitet. Dies entspricht auch in etwa den 15 % an Steigerung der Bandbreite, die Intel in der Folie erwähnt. Die TDP wird mit 15 W angegeben. Die Module der ersten Generation des Optane DC Persistent Memory sind ebenfalls nicht gerade sparsam. Je nach gewünschter Leistung können sie zwischen 12 und 18 W in 0,25-W-Schritten konfiguriert werden. Abhängig von den jeweiligen Zugriffen auf den Speicher (lesen/schreiben) und der Konfiguration der Leistung liegt die Bandbreite zwischen 0,73 und 8,3 GB/s für ein DIMM des DCPM.

Scheinbar will Intel die DCPM-Module der zweiten Generation mit einem blauen Heatspreader ausstatten, damit diese leichter zu erkennen sind.

Der zweite Teil der Folie beschäftigt sich mit den Plattformen, in denen der neue Speicher eingesetzt werden soll. Dies währen Whitley und Cedar Island. Whitley wird die 2S-Plattform für die Xeon-Prozessoren auf Basis von Ice Lake sein. Hier will Intel ein Octa-Channel-Speicherinterface mit der Unterstützung von DDR4-3200 und 4 TB an Gesamtspeicherkapazität pro Sockel bieten.

Interessanterweise spricht Intel von vier IMCs (Integrated Memory Controller) in einem Ice-Lake-Prozessor. Jeder der vier Dual-Channel-Speichercontroller kann sowohl normalen DDR4-Speicher als auch DCPM ansprechen.

Cedar Island hingegen nimmt die Cooper-Lake-Prozessoren auf. Als 4S-Plattform können vier Prozessoren in einem Node verwendet werden. Die Prozessoren unterstützen ein Hexa-Channel-Speicherinterface mit einer Kapazität von 3 TB pro Sockel und mit einer Geschwindigkeit von 2933 MT/s (DDR4-2933).

Erst Cooper Lake, dann Ice Lake

Zunächst werden die Cooper-Lake-Prozessoren erwartet, die unter anderem Bfloat16 unterstützen werden. Sie sollen vor allem für Multi-Socket-Systeme interessant sein und bieten pro Sockel bis zu 56 Kerne. Gefertigt werden die Cooper-Lake-Xeons noch in 14 nmm.

Gegen Ende des Jahres sollen dann auch die Ice-Lake-Xeons hinzukommen, die bis zu 28 Sunny-Cove-Kerne bieten sollen und in 10 nm gefertigt werden. Es werden die ersten 10-nm-Prozessoren mit derart vielen Kernen sein.