Werbung

Einige Kollegen der Presse wurden von Intel nach Hillsboro, Oregon, eingeladen. Dort wurden einige weitere Details zur kommenden Xeon-Phi-Generation alias Knightss Landing verraten. Demnach wird der Chip auf 8 Milliarden Transistoren kommen und ist damit ähnlich komplex wie der GM200 auf der GeForce GTX Titan X von NVIDIA (Hardwareluxx-Artikel). Für Intel ist es ein neuer Rekord in Sachen Transistoranzahl und -dichte, wenngleich man noch keine Angaben zur Chipgröße macht. Gefertigt werden soll Knightss Landing im 14-nm-FinFET-Verfahren.

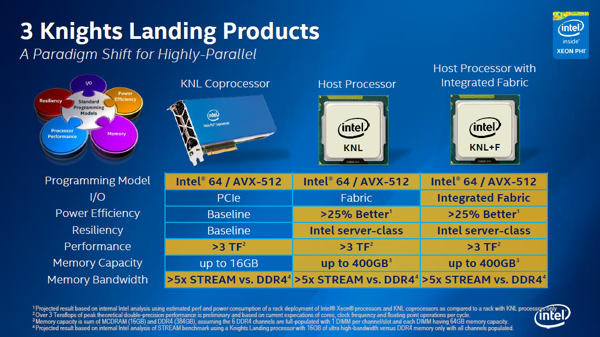

Die Informationen stammen von den Kollegen von Golem.de, die sich in den USA befinden und denen ein tiefergehender Eindruck gewährt wurde. Demnach plant Intel für die F-Version der Xeon-Phi-Beschleunigerkarten die Verwendung von mindestens 60 Beschleunigerkernen, die auf der "Silvermount"-Architektur basieren. Denkbar sei auch ein Ausbau mit 72 solcher Rechenkerne. Diese bauen auf der klassischen x86-Architektur der "Silvermount"-Architektur auf und können pro Kern vier Threads bearbeiten. Daneben besitzen sie noch AVX512-Einheiten. Im Vergleich zum Einsatz in der "Bail Trail"-Plattform sind aber einige Änderungen vorgenommen worden, die auf den Xeon-Phi-Karten besonders interessant sind. Dazu zählt unter anderem eine andere Cache-Hierarchie. Eine höhere Pack-Dichte im Server will Intel durch die Sockelbarkeit der neuen "Knights Landing"-Xeon-Phi erreichen.

Insgesamt sollen die neuen Xeon-Phi-Beschleuniger auf über 3 TFLOPS Double-Precision-Performance kommen. Zum Vergleich: AMDs FirePro W9100 kommt auf 2,62 TFLOPS und NVIDIAs Tesla K80 erreicht 2,91 TFLOPS. Wichtig ist aber auch der lokal verfügbare Speicher, der 16 GB groß sein soll. Beim Speicher handelt es sich um Hybrid Memory Cubes von Micron, die im gleichen Package untergebraucht sind, wie der Xeon-Phi-Chip. Damit will Intel die Zugriffszeiten auf diesen Speicher reduzieren und auch die Bandbreite erhöhen. Letztgenannte soll bei 480 GB pro Sekunde liegen, was in etwa 1/3 schneller ist, als das was AMD und NVIDIA derzeit als Anbindung ihrem Grafikspeicher zur Verfügung stellen können.

Die Xeon-Phi-Beschleunigerkarten der "Knights Landing"-Generation können aber nicht nur als eigenständige Beschleunigerkarte mit PCI-Express-Interface angeboten werden, sondern auch direkt als Host-Prozessor. Diesen Prozessoren soll es dann möglich sein bis zu 384 GB DDR4 Arbeitsspeicher anzusprechen, was gerade den Speicherintensiven Anwendungen zugute kommen sollte. Diese 384 GB sind aufgeteilt in sechs Speicherkanäle mit je einer Kapazität von 64 GB DDR4-2400. Die Speicherbandbreite liegt hier bei 115 GB pro Sekunde.

Wichtiger Bestandteil eines jeden Xeon-Phi-Beschleunigers ist der Omni-Path. Darin will man nicht nur die Geschwindigkeit auf bis zu 100 GBit pro Sekunde hochschrauben, sondern auch die Latenzen verringern sowie die Anzahl der Switches in einem solchen Netzwerk reduzieren. Intel positioniert Omni-Path direkt gegen die etablierte InfiniBand-Technik, die aktuell in den meisten derartigen Systemen zum Einsatz kommt.

Im zweiten Halbjahr 2015 möchte Intel die ersten Modelle von Knights Landing ausliefern. Komplette HPC-Systeme sind für 2016 geplant.