Werbung

Im Rahmen des sogenannten "Form 10-K", einem Bericht von Intel an die US-amerikanische Börsenaufsicht Securities and Exchange Commision (SEC), hat Intel auch Details zur Zukunftsstrategie der eigenen Fertigung veröffentlicht. Schon seit geraumer Zeit wird ein Ende von Moore's Law vorausgesagt, da immer kleinere Fertigungstechnologien auch immer höhere Kosten nach sich ziehen. Bisher kann dies durch die Unternehmen mithilfe verschiedener Tricks noch aufgefangen werden. Wie lange dies noch gelingen wird, lässt sich kaum abschätzen.

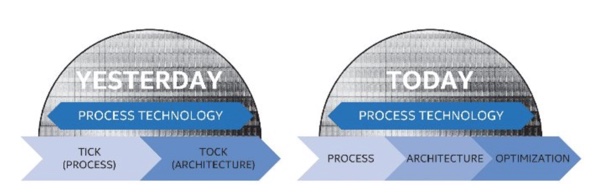

Doch bei Intel hat bereits ein Umdenken stattgefunden. Seit einigen Jahren verfolgt Intel hinsichtlich der Fertigung folgende Prinzip: Das Tick-Tock-Prinzip beschreibt einen Tick als Wechsel des Fertigungsprozesses, während ein Tock einen Wechsel der Architektur darstellt. Somit kann Intel mögliche Komplikationen beim Wechsel der Architektur oder der Fertigungstechnologie voneinander trennen. Dieses Prinzip soll auch noch in mindestens zwei Schritten weitergeführt werden. Spätestens danach aber sieht Intel einen Wechsel auf eine Strategie in drei Schritten vor: Process-Architecture-Optimization.

"As part of our R&D efforts, we plan to introduce a new Intel Core microarchitecture for desktops, notebooks (including Ultrabook devices and 2 in 1 systems), and Intel Xeon processors on a regular cadence. We expect to lengthen the amount of time we will utilize our 14nm and our next generation 10nm process technologies, further optimizing our products and process technologies while meeting the yearly market cadence for product introductions."

Der Hauptgrund für die Umstellung sind also die Kosten für immer kleinere Fertigungsprozesse und daraus zieht Intel auch den Schluss bzw. sieht bereits in der aktuellen Fertigung in 14 nm eine deutliche Verlängerung des Zeitraumes, bis zu dem ein solch neuer Fertigungsprozess hinsichtlich der Kosten die Investitionen rechtfertigt. Aus diesem Grund hat Intel auch einige eigentlich schon früher geplante Wechsel weiter nach hinten geschoben und so wurden in den vergangenen drei Jahren nur zwei neue Produktgenerationen auf den Markt gebracht.

Derzeit lässt Intel in seinen Fabriken in Irland, Arizona und Oregon in 14 nm fertigen, während die Produktion in 22 nm neben Arizona und Oregon zusätzlich noch in Israel durchgeführt wird. Für den Wechsel auf 10 nm gibt es noch keine konkreten Ausbaupläne für die Fabriken, allerdings scheint ein Wechsel auf größere Wafer durch Intel geplant zu sein. Derzeit verwendet Intel solche mit einem Durchmesser von 300 mm. Zukünftig sollen es 450 mm sein, was die Kosten durch eine bessere Ausbeute reduzieren sollte.

Der schrumpfende Vorsprung Intels hinsichtlich der Fertigung ist wahrnehmbar, allerdings ist Intel der Konkurrenz noch einige Schritte voraus. Samsung, TSMC und GlobalFoundries fertigen zwar bereits in 16/14 nm, allerdings sind die Chips die darin gefertigt werden deutlich kleiner, als bei Intel. Hier werden Chips mit einer Fläche von 400 mm2 gefertigt, während es bei Samsung und TSMC gerade einmal etwas über 100 mm2 erreicht haben. GlobalFoundries wird erst mit den AMD-GPUs auf Basis der Polaris-Architektur überhaupt solch große Chips in dieser Fertigungstechnologie produzieren. In weiten Bereichen wird Intel auf absehbare Zeit als die Voreiterrolle behalten.

Offen ist noch die Frage, welche Auswirkungen der 3. Schritt des Process-Architecture-Optimization-Rhythmus haben wird. Optimierung kann vieles bedeuten, über solche auf Ebene der Mikroarchitektur bis hin zu niedrigeren Spannungen und höhere Taktraten aufgrund einer optimierten Fertigung. Spannend wird auch zu sehen sein, in wie weit Intel die Plattform im PAO-Rhythmus stabil halten kann und beispielsweise kein Wechsel des Sockel oder Chipsatzes notwendig wird. Daran dürften auf der einen Seite die Kunden Interesse haben, die ihre Infrastruktur nicht notwendigerweise wechseln müssen, auf der anderen Seite nutzen die Mainboard-Hersteller einen häufigen Wechsel gerne um die eigenen Produkte zu erneuern und neue Absatzmärkte zu finden.

Wir sind gespannt, wann Intel sich etwas genauer zum Process-Architecture-Optimization-Rhythmus äußern wird und weitere Details veröffentlicht.