Werbung

Mehr und mehr Kerne finden ihren Weg in moderne SoCs. Zehn Kerne gehören im High-End-SoC-Bereich bereits zum Standard – auch wenn man über die Sinnhaftigkeit sicherlich streiten darf. Prozessoren mit Kernen auf Basis der ARM-IP drängen aber auch zunehmend in den Serverbereich und zum Beispiel Netzwerkhardware kann hier die Vorteile der Effizienz sehr gut ausspielen. In solchen SoCs sind dann auch 128 Kerne keine Seltenheit mehr.

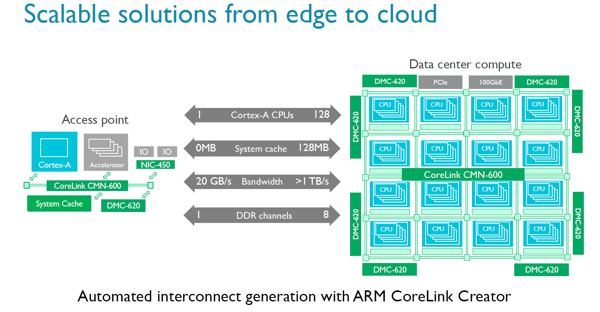

Prozessoren mit 128 Kernen benötigen aber nicht nur schnelle Rechenkerne, sondern auch einen möglichst schnellen Interconnect, damit die Kerne die Daten untereinander und mit den Caches und Register austauschen können. Auch die Speicheranbindung spielt eine wichtige Rolle und in diesem Zuge hat ARM nun mit dem CoreLink CMN-600 einen schnelleren Interconnect und mit dem DMC-620 einen 8-Channel-DDR4-IMC (Integrated Memory Controller) vorgestellt.

Der Vorgänger des CoreLink CMN-600, der CoreLink CMN-512, unterstützt zwölf Cluster mit jeweils vier Kernen. Per Coherenter Anbindung konnten damit SoCs mit bis zu 48 Kernen realisiert werden. Der neue CoreLink CMN-600 unterstützt bis zu 128 Kerne in 32 Clustern zu jeweils vier Kernen. Als Teil des CoreLink CMN-600 wird ein neuer Agile System Cache eingeführt. Dieser soll die Kommunikation von I/O-Geräten mit dem SoC verbessern.

Der neue DMC-620 unterstützt bis zu 8-Channel-DDR4-Speicher, während der Vorgänger DMC-520 auf vier Kanälen nur DDR3 unterstützt. Jeder Kanal des DMC-620 kann bis zu 1 TB DDR4-Speicher verwalten, so dass ein entsprechender SoC auf eine maximale Ausstattung von 8 TB kommt. Für den DMC-620 verspricht ARM eine um 50 % reduzierte Latenz und die Bandbreite soll um den Faktor Fünf steigen. Dies kommt vermutlich aufgrund der Unterstützung von DDR4-3200 zu Stande, der mit 3.200 MT/s doppelt so schnell ist, wie der DDR3-1600 mit 1.600 MT/s. Da sich auch die Anzahl der Kanäle verdoppelt hat, wäre die Vervierfachung zu nennen, das ARM aber von einem Faktor fünf spricht, dürfte ARM hier noch weitere Optimierungen implementiert haben.

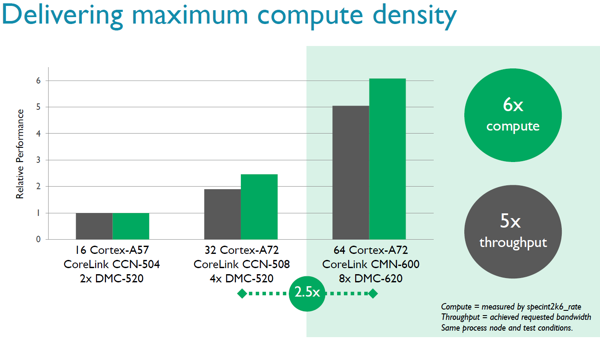

Auch einige Leistungswerte für die Rechenleistung nennt ARM. 64 Cortex-A72 sollen 2,5 x schneller sein als 32 Cortex-A72 im SPEC int2600_rate. Im Vergleich zu 16 Cortex-A57 sollen die 64 Cortex-A72 um den Faktor Sechs schneller sein. Die Benchmarks zeigen also eine recht gute Skalierung durch den verbesserten Speichercontroller. Beim Wechsel von DDR3 auf DDR4 bei den Desktop-Prozessoren waren solche Leistungszugewinne nicht zu beobachten.

Der CoreLink CMN-600 und der DMC-620 IMC wird vermutlich in Kürze in ersten Server-SoCs zu finden sein. Da die Hersteller ihre Lizenzen aber oft nicht öffentlich machen, wird es schwer herauszufinden sein, wer die IP von ARM nutzt. Hersteller wie Qualcomm, Avago und Broadcom sind aber heiße Kandidaten.