Werbung

Mit dem Kauf von Altera hat sich Intel auf dem Markt für FPGAs (Field Programmable Gate Array - ein integrierter Schaltkreis, in den eine logische Schaltung programmiert werden kann) stärker aufgestellt und veröffentlicht mit dem Stratix 10 auch eine neue Generation an SoC in diesem Bereich. Dazu verwendet Intel die von Altera entwickelte HyperFlex-Technologie und steuert die eigene Fertigung in 14 nm bei. Üblicherweise können FPGAs in größeren Fertigungstechnologien gefertigt werden, als dies bei aktuellen Prozessoren, GPUs oder SoCs der Fall ist. Die Fertigung im 14-m-Verfahren bietet aber vor allem hinsichtlich der Leistungsaufnahme einige Vorteile.

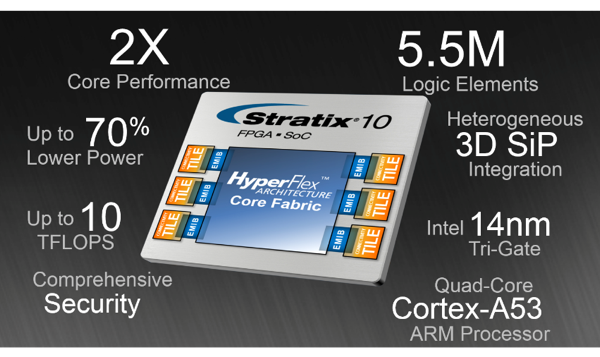

Der Stratix 10 soll eine um den Faktor zwei höhere Leistung als der Stratix V bieten und erreicht durch die kleinere Fertigung einen um den Faktor fünf kompakteren Aufbau des SoC. Ähnlich aufgebaute FPGAs sollen im Vergleich zwischen dem Stratix 10 und 5 um 70 % sparsamer sein. Der Logikteil, der interne Speicher und die DSP-Blocks erreichen dabei einen Takt von 1.000 MHz. Intel verwendet in der Stratix-10-Serie bis zu vier CPU-Kerne auf Basis der ARM-Cortex-A53-Architektur.

FPGAs wie die der Stratix-10-Serie sind speziell für einen hohen Datendurchsatz ausgelegt. Dieser ist in Data-Centern ebenso erforderlich wie in Netzwerkinfrastruktur. Hier sieht Intel daher auch das Haupteinsatzgebiet der neuen FPGA-Serie und untermauert dies auch mit einigen Zahlen. So sind 2012 etwa 77 TBits/s durch das Internet geflossen. 2017 sollen es hingegen schon 11,2 EBit/s sein - eine Steigerung um den Faktor 140. Gleichzeitig benötigt die Verarbeitung derart vieler Daten im Netzwerk auch viel Strom. Zwischen 2011 und 2012 ist der Bedarf an Strom in den Rechenzentren bereits um 63 % auf 38 GW gestiegen und in den darauffolgenden Jahren wurde ein ähnlicher Anstieg anvisiert. Die um 70 % sparsameren Stratix-10-FPGAs sollen dem Trend zumindest ein wenig entgegenwirken.

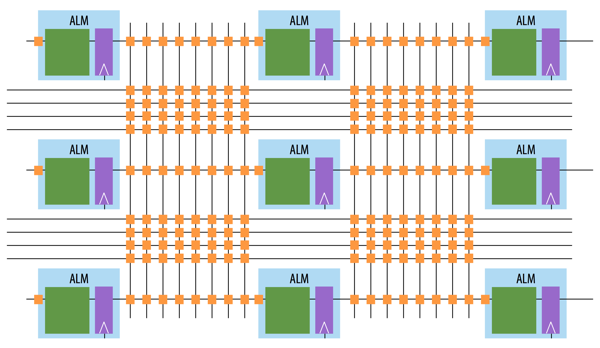

Um eine Leistung von bis zu 10 TFLOPs in einem solchen FPGA zu erreichen, verwendet Altera in der Architektur die bereits erwähnte HyperFlex-Technologie. Diese verbindet alle Komponenten des SoCs über einen extrem breiten Bus mit bis zu 1.024 Bit und enthält auch einen internen Interconnect, die sogenannten Hyper-Register, die alle Adaptive Logic Modules (ALMs) miteinander verbinden. Ebenfalls über diesen Interconnect angebunden sind der integrierte Speicher sowie die DSP-Blocks. Innerhalb des Netzes aus Verbindungen können einzelne Knoten auch übersprungen werden, um den schnellsten Pfad für die einzelnen Datenverbindungen zu finden.

Weitere Architektur-Details wie das Hyper-Retiming, Hyper-Pipelining und Hyper-Optimization sollen ebenfalls dafür sorgen, dass die Stratix-10-Serie schneller als jeder andere FPGA ist. Das Design unterstützt dabei die in diesem Bereich übliche Quartus-II-Software. Erste Samples der Stratix-10-FPGAs werden derzeit an die Partner von Altera ausgeliefert. Mit ersten Produkten soll im kommenden Jahr zu rechnen sein. Auf der Seite von Altera sind die einzelnen Produkte auf Basis des Stratix 10 aufgeführt.