Werbung

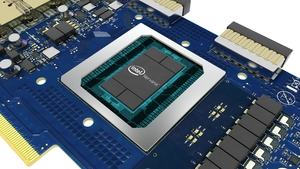

Mitte Oktober stellte Intel seinen Neural Network Processor (NNP) offiziell vor. Der NNP ist auf Anwendungen im Bereich der Artificial Intelligence ausgelegt. Nun, zur Neural Information Processing Systems oder kurz NIPS, die derzeit in Long Beach in den USA stattfindet, hat man weitere Details zum Prozessor veröffentlicht.

Mit dem NNP adressiert Intel Anwendungen, die bereits auf einem neuronalen Netzwerk arbeiten, die aber mit immer größeren Daten gefüttert werden sollen. Damit dies funktioniert, müssen drei Bedingungen erfüllt werden: Erstens muss die Rechenleistung weiter gesteigert werden. Zweitens muss es möglich sein, das neuronale Netzwerk auf deutlich mehr Hardware (mehreren Nodes) ausführen zu können. All dies soll drittens mit einer möglichst niedrigen Leistungsaufnahme möglich sein.

Der NNP setzt dazu auf eine spatiale Architektur. Diese macht es möglich, dass große Datensätze auch über alle HBM2-Speicherstacks hinweg abgelegt werden können und damit stets nahe an den Recheneinheiten vorliegen. Das Speichermanagement soll aber auch sicherstellen, dass Daten so wenig wie möglich hin und her geschrieben werden müssen. Müssen Daten auf externen Speicher ausgelegt werden, so bestimmt das Speichermanagement auch hier, welche Daten ausgelagert werden und welche auf dem HBM2 verbleiben können. Pro Compute Unit stehen 30 MB an lokalem HBM2 zur Verfügung, der dediziert nur dieser einen Unit zugeteilt ist.

Muss eine zweite Compute Unit auf Daten einer anderen zugreifen, können sich diese den bereits verwendeten Speicherbereich teilen, so dass keine Neuzuteilung der eigentlichen Daten notwendig ist. Laut Intel ist es sogar möglich, dass eine Compute Unit eines NNP auf Daten einer Compute Unit eines zweiten NNP zugreifen kann, ohne dass diese vom HBM2 der ersten NNP auf den HBM2 des zweiten NNP kopiert werden muss. Intel nennt dies zero-cycle, was dabei helfen soll, die Speicherbandbreite zu optimieren.

Mit dem NNP führt Intel ein neues Datenformat ein. Der Flexpoint-Datentyp soll in diesem Bereich Vorteile gegenüber dem Floating-Point-Datentyp haben, da er kleinere effizientere Multiplikatoren verwendet. Für FP16 hat Flexpoint auch eine höhere Genauigkeit bei der Berechnung von Matrizen, da die vollen 16 Bit für die Mantisse verwendet werden und nicht wie bei FP16 Floating Point dazu nur noch 11 Bit zur Verfügung stehen. Flexpoint bedarf zunächst einmal keiner weiteren Anpassung durch den Nutzer, denn entsprechende Daten können per Autoflex automatisch überführt werden. Intel hat zum Flexpoint-Datentyp einen ausführlichen Artikel veröffentlich, der zahlreiche Informationen enthält.

Mit der ersten NNP-Generation ermöglicht Intel also einen 16 Bit Multiplikator mit einem 5 Bit Exponenten. Ein zukünftiger NNP könnte aber auch kleinere Datentypen ermöglichen.

Der NNP verwendet einen eigens entwickelten Interconnect, der aus zwölf bidirektionalen Links mit 100 GBit/s besteht. Insgesamt kommt der Interconnect also auf 1,2 TBit/s. Dieser Interconnect ist per Software konfigurierbar. Es gibt virtuelle Kanäle, denen Bandbreite zugeteilt werden kann. Auch ist es möglich, innerhalb eines Kanals verschiedene Prioritäten zu etablieren.

Werden mehrere NNPs miteinander verknüpft, so stellt sich dies für den Entwickler und letztendlich auch für die Applikation (das neuronale Netzwerk) so dar, dass diese als einzelnes Compute-Element funktionieren. Es findet also keine Parallelisierung der Daten in oberster Ebene statt. Dies soll die Skalierung der Rechenleistung verbessern.

Angaben zum Preis oder der genauen Verfügbarkeit macht Intel noch immer nicht. Die ersten NNPs sollen aber noch in diesem Jahr ausgeliefert werden.