Werbung

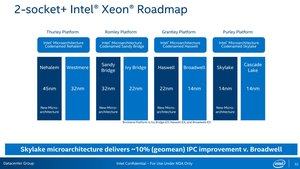

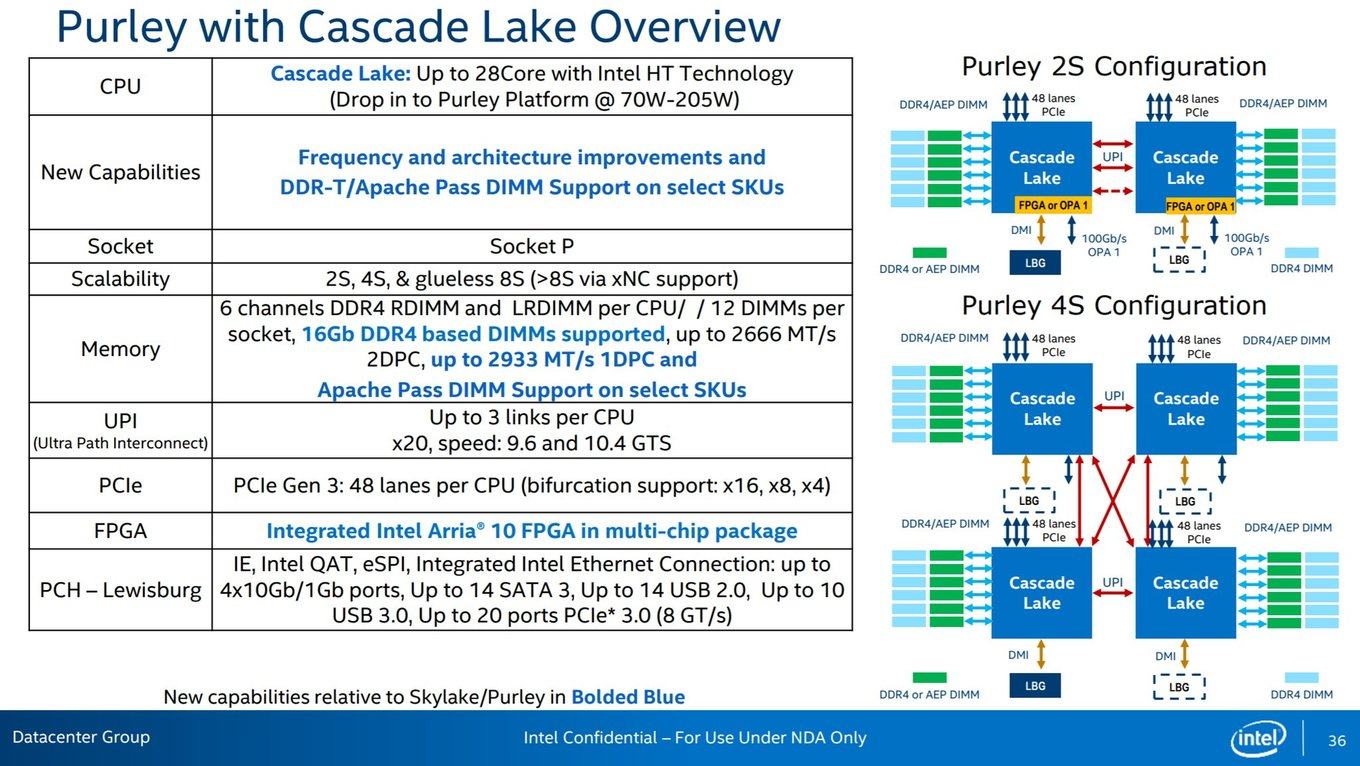

Auf einer Konferenz zum Thema High Performance Computing in Saudi Arabien sind weitere Details zu den zukünftigen Server-Prozessoren aus dem Hause Intel bekannt geworden. Die dazugehörigen Cascade-Lake-Prozessoren sind zur bestehenden Purley-Lake-Plattform kompatibel und bieten einige bereits bekannte Änderungen, scheinen aber vor allem der bisherigen Strategie für Multi-Sockel-Server von Intel treu zu bleiben.

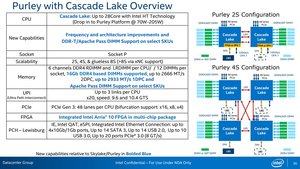

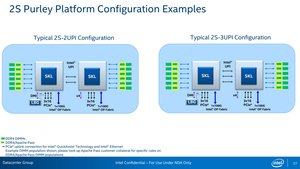

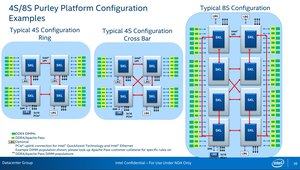

Server mit zwei oder mehr Sockeln sind im HPC-Bereich noch immer ein wichtiger Faktor. Während AMD mit den Epyc-Prozessoren maximal zwei Sockel unterstützt (hier dann aber bis zu 64 Kerne, 128 PCI-Express-Lanes und bis zu 4 TB an Arbeitsspeicher in Octa-Channel-Konfiguration anbieten kann), wird Intel auch mit Cascade Lake Server mit zwei, vier oder gar acht Sockeln anbieten. In der Präsentation spricht Intel zudem von einer „glueless" Konfiguration und spielt damit auf den Umstand an, dass AMD in den Epyc-Prozessoren jeweils vier Zeppelin-Dies per Multi-Chip-Module (MCM) zusammenführt und damit auf bis zu 32 kommt, während bei Intel ein monolithisches Design gewählt wurde. Mit Cascade Lake wird es für Intel bei maximal 28 Kernen und 56 Threads bleiben.

Cascade Lake wird ein Hexa-Channel-Speicherinterface anbieten und DDR4-2933 unterstützen. Die Cascade Lake-Prozessoren werden auch die ersten sein, die DIMMs mit 3DXPoint unterstützen werden. Bei 15 bis 18 W Verbrauch pro DIMM-Modul nimmt Intel hier auch einen gewissen Mehrverbrauch in Kauf und in den Servern muss die Stromversorgung entsprechend ausgelegt sein.

Über die Änderungen, bzw. Optimierungen in der Architektur von Cascade Lake gibt es bisher keinerlei Informationen. Bekannt ist nur, dass Intel mit Cascade Lake die Sichereitslücken Spectre (Variante 2) und Meltdown in Hardware beheben möchte. Zudem kommen mit AVX-512 Vector Neural Network Instructions neue Instruktionen hinzu.

Cascade Lake-SP mit integriertem FPGA

Interessant ist Cascade Lake aber auch noch aus einem anderen Gesichtspunkt. So wird Intel hier erstmals in einen Serverprozessor per MCM einen FPGA integrieren. Bestimmte Modellvarianten werden mit einem Arria 10 ausgestattet sein. Als Arria 10 GX bietet Intel diese derzeit auf PCI-Express-Beschleunigerkarten mit einer Rechenleistung von 1,5 TFLOPS für Fließkommaberechnungen mit einfacher Genauigkeit an. Vermutlich wird Intel hier einmal mehr seine MCM-Technologie namens Embedded Multi-die Interconnect Bridge oder kurz (EMIB) einsetzen, um die Cascade-Lake-Prozessor mit dem FPGA zu verbinden.