Werbung

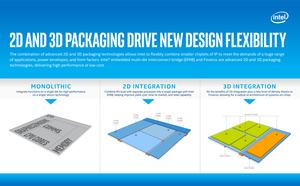

Über Jahre hinweg hilt Intel an einem monolithischen Aufbau der Prozessoren fest. Für Spezialanwendungen wurden bereits FPGAs oder GPUs im Package per EMIB oder einer anderen Interposer-Technologie angebunden, aber zumindest mit der Ankündigung die Cascade-Lake-AP-Prozessoren bestünden aus zwei CPU-Dies mit jeweils 24 Kernen war klar, dass auch bei Intel ein Umdenken in der allgemeinen Strategie begonnen hat.

Die Konkurrenz macht es vor, was nicht zwangsläufig heißt, dass dies der beste Weg ist. AMD wird mit den EPYC-Prozessoren der zweiten Generation das Multi-Chip-Module-Design (MCM) weiter ausbauen. Bis zu vier CPU-Chiplets werden mit einem zentralen I/O-Die verbunden. Intel forscht schon lange an Technologien, die es ermöglichen sollen, mehrere Chips miteinander zu verbinden. Die Embedded Multi-die Interconnect Bridge oder kurz EMIB macht es möglich unterschiedliche Chips, auch aus unterschiedlichen Fertigungen, miteinander zu kombinieren.

Dabei spricht Intel auch davon, dass eine kleinere Fertigung nicht zwangsläufig die bessere sein muss. Bei der Entwicklung eines Designs müsse man sich aber früher oder später auf eine bestimmte Fertigung festlegen. Diese Auslegung macht es aber umso schwerer bzw. unwirtschaftlich, später noch einmal wechseln zu können. Das was Intel unter 14 nm, 14 nm+, 14 nm++ usw. führt, ist mitunter recht kompliziert umzusetzen.

EMIB ist der Oberbegriff für das, was als Foveros ab 2019 in breiteren Einsatzgebieten verfolgt werden soll. Es geht darum, für ein MCM-Design bestehend aus CPU, GPU, Speicher und anderen Bauteilen immer die dazu ideale Fertigung nutzen zu können. Auch dies macht AMD bei den EPYC-Prozessoren der zweiten Generation vor: Während die CPU-Chiplets aus der 7-nm-Fertigung stammen, wird der I/O-Die in 14 nm gefertigt.

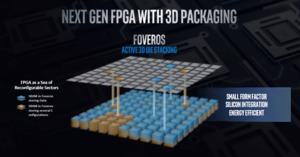

Dies ist aktueller Stand der Technik, denn bei den GPUs und CPUs kommen aktive Interposer bereits zum Einsatz. Intel kombiniert Skylake-CPUs mit Stratix-FPGAs in einem Package. Dieser Ansatz soll nun weiter ausgebaut werden – und in die dritte Dimension überführt werden. In einem Beispiel spricht Intel von einem Hybrid-SoC, der bereits 2019 auf den Markt kommen soll. Dieser besteht aus einem Basis-Package, auf dem wiederum ein I/O-SoC sitzt. Darauf wird ein Compute-Die gestapelt und darüber befindet sich ein sogenannter PoP-Speicher.

Einige Bereiche der verwendeten Fertigungstechnik sind bereits bekannt und werden schon angewendet. So gibt es bereits Speicher, der aus vertikal zueinander gestapelten Schichten besteht. High Bandwidth Memory und sogenannter 3D-NAND sind derart aufgebaut. Mit der Foveros-Technologie soll es nun aber möglich sein, einen solchen 3D-Speicher auf einem anderen Chip zu platzieren, beide Chips zueinander, aber auch weitere Chips über den Interposer mit allen weiteren zu verbinden. Es gibt demnach Thru-Silicon Vias (TSVs) zum Package, aber auch solche die vom gestapelten Chip durch die erste Ebene führen.

Das erste Produkt soll bereits 2019 vorgestellt werden und besteht aus einem I/O-SoC, gefertigt in 22 nm, auf dem ein Compute-Die aus der 10-nm-Fertigung sitzt. Beides sitzt wiederum auf einem Package bzw. dem PCB des Package und darüber wird ein Speicher im PoP-Design (Package on Package) verbaut.

Das gesamte Package ist nur 12 x 12 x 1 mm groß und soll sich daher für den mobilen Einsatz eignen. Intel spricht von einer Standby-Leistung von gerade einmal 2 mW.

Offen ist noch die Frage, ob sich eine solche Technik auch für Hardware einsetzen lässt, die leistungsstärker als das ist, was 2019 im ultramobilen Bereich erwartet wird. Die Kühlung ist bei einem solchen Design sicherlich das größte Problem und daher wird sich die Foveros-Technologie vorerst wohl auf besonders sparsame Prozessoren beschränken.