Werbung

Server- oder Datacenter-Prozessoren auf Basis von ARM-Kernen haben sich trotz aller Unkenrufe in gewisser Weise etabliert. Zwar ist deren Einsatz noch immer sehr beschränkt, inzwischer aber ist es allgemeiner Konsens, dass wir solche Hardware in Zukunft mehr und mehr im Hintergrund werden arbeiten sehen. Die Skalierbarkeit der jeweiligen Aufgaben ist die Stärken solcher Prozessoren und mit dem Ampere eMag (32 Kerne), Cavium ThunderX2 (32 Kerne) und dem Qualcomm Centriq 2400 (48 Kerne) gibt es bereits einige weitere Modelle von anderen Herstellern, die mit einer hohen Anzahl an Kernen auftrumpfen. Huaweis Kunpeng 920 bietet 64 ARM-Kerne und wird in 7 nm gefertigt.

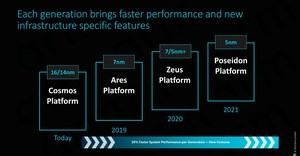

ARM stellt sich ab 2019 nun mit den Neoverse N1 und E1 in diesem Bereich neu auf. Die dazugehörige Plattform hört auf den Namen "Ares" und greift auf die 7-nm-Fertigung zurück. 2020 soll "Zeus" heißen und in 7 bzw. 5 nm gefertigt werden. Bereits 2021 soll "Poseidon" dann endgütig auf 5 nm wechseln. ARM hat also sowohl längerfristige, als auch schnell wachsende Pläne.

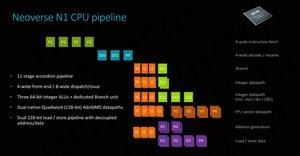

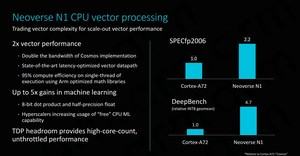

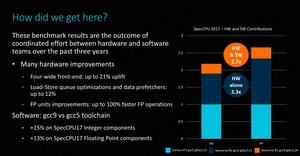

Als Basis bietet die N1-CPU eine ähnlich organisierte Pipeline wie das Cortex-A76-Design. Es handelt sich um einen 4-wide Fetch bzw. 8-wide Decoder/Dispatcher mit einer nur elf Stages tiefen Pipeline als Front-End. Im Back-End vorhanden sind drei ALUs – zwei für Multiplikationen und Divisionen und eine dritte, 128 Bit breite SIMD für Vektor- und Fließkommaberechnungen.

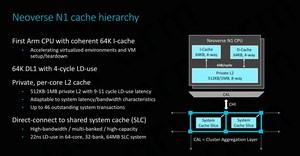

Hinsichtlich der Caches sieht ARM jeweils 64 kB für Instruktionen und Daten im L1-Cache und 512 oder 1.024 kB an L2-Cache vor. Hinzu kommt ein 128 MB großer System Level Cache (SLC), der allen Kernen zur Verfügung steht. Systemübergreifend geht es darum die Caches mit besonders niedrigen Latenzen anzulegen. Möglichst große Branch Target und Direction Buffer sollen Sprungvorhersagen optimieren.

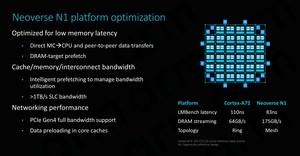

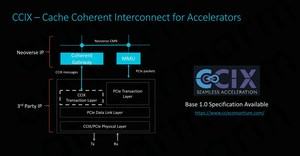

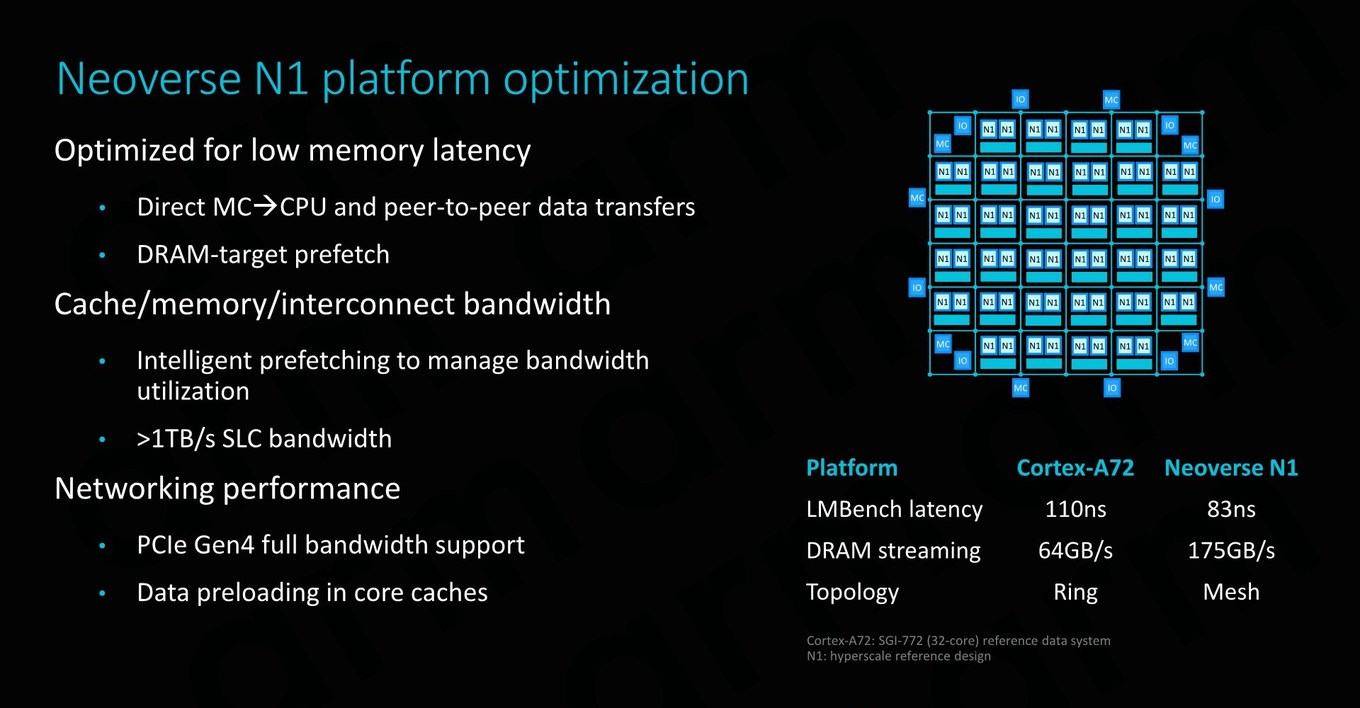

Rückgrad eines SoCs auf Basus der N1-Kerne bildet die Component Aggregation Layer (CAL). Diese besteht aus zwei Interfaces und wird in einer Mesh-Topologie ausgelegt. Eines der Interfaces bildet die Netzwerkebene, die in einem Mesh aus zahlreichen Kreuzungen besteht, die als Switch oder Router als XP (Crosspoint) bezeichnet werden. Das zweite Interface des CAL bindet den System Level Cache an. Das Mesh-Netzwerk arbeitet mit etwa 2/3 des Taktes der CPU-Kerne und auch hier spielen natürlich besonders niedrige Latenzen die wichtigste Rolle.

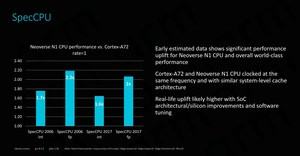

Daneben ist der Durchsatz von entscheidender Bedeutung. Diesen will ARM im Vergleich zum Cortex-A72-Design mehr als verdoppelt haben.

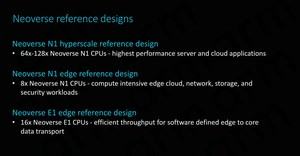

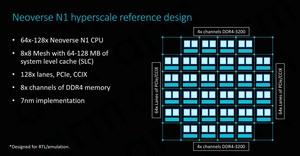

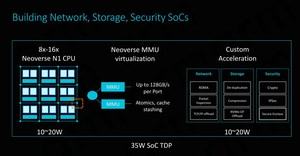

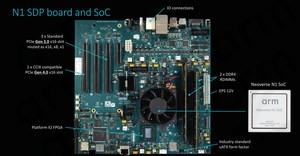

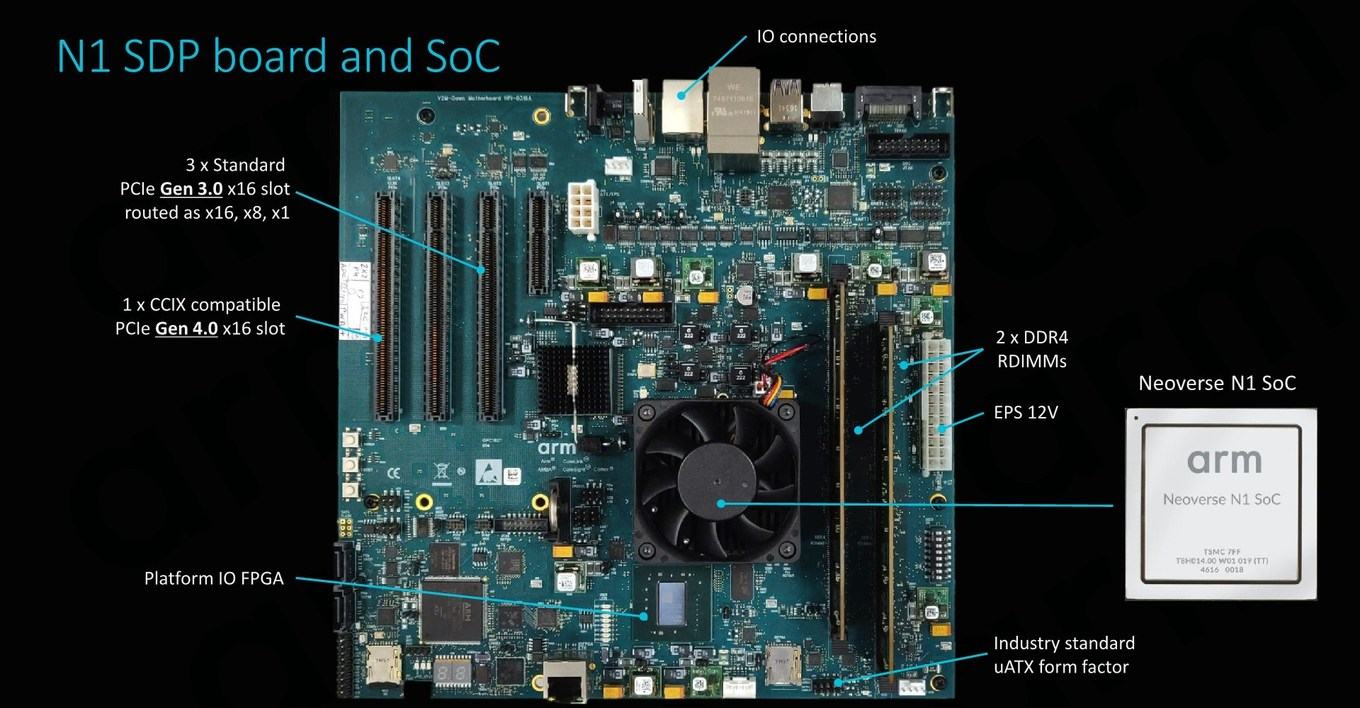

Bereits in seinen Referenzplattformen sieht ARM unterschiedliche Lösungen auf Basis der N1-CPU vor. Das N1-Edge-Design soll in Netzwerk-, Edge-Cloud- und Speicheranwendungen Verwendung finden. Hier sieht ARM bis zu acht Neoverse-N1-CPUs vor. Das N1-Hyperscale-Design zeigt das Potenzial der Architektur im vollen Umfang. 64 bis 128 N1-CPUs sind hier vorgesehen, die in einem 8x8-Mesh zusammengefasst sind. Entweder 64 oder 128 MB an System Level Cache sind dann vorhanden. Hinzu kommen 128 PCI-Express-4.0-Lanes und ein Octa-Channel-Speicherinterface.

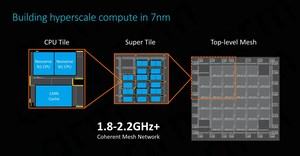

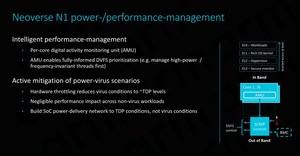

Organisiert ist ein solcher SoC wie folgt: Es gibt "CPU-Tiles", die aus jeweils zwei N1-Kernen bestehen. Acht dieser CPU-Tiles sind zu einem "Super Tile" zusammengefasst. Dieser wiederum bilden die Grundbausteine für das N1-Hyperscale-Design mit bis zu 128 Kernen. Das Mesh-Netzwerk soll mit einem Takt zwischen 1,8 und 2,2 GHz arbeiten. Entspricht dies 2/3 des Taktes der Kerne, so kommen diese auf 2,4 bis 3,0 GHz.

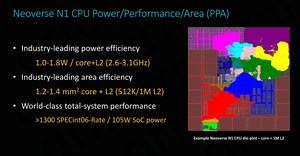

Ein derart aufgebauter SoC soll in der Variante mit 64 Kernen eine Leistungsaufnahme von 105 W besitzen. Je nach Anwendung soll er die Intel- und AMD-Prozessoren mit 28 und 32 Kernen aber weit hinter sich lassen und damit wesentlich effizienter sein.

Neoverse E1 als erstes erstes ARM-Design mit Simultaneous Multi Threading

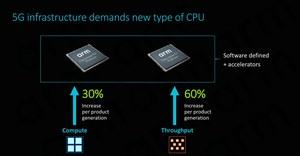

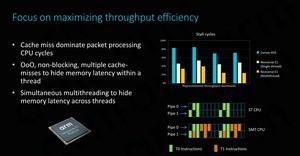

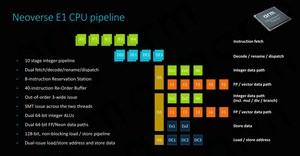

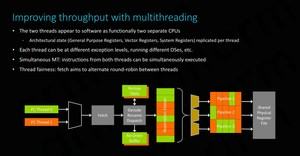

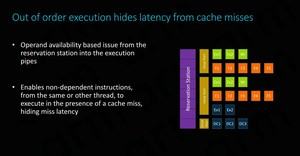

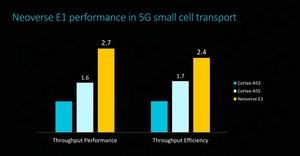

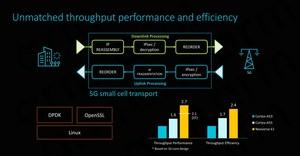

Geht es beim Neoverse N1 darum, Daten möglichst schnellstmöglich zu verarbeiten, stellt ARM mit dem Neoverse E1 auch gleich ein Design vor, welches auf die Verarbeitung großer Datenmengen ausgelegt ist. Es handelt sich um das erste ARM-Server-Design, welches Simultaneous Multi Threading (SMT) unterstützt.

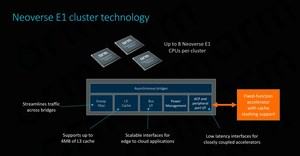

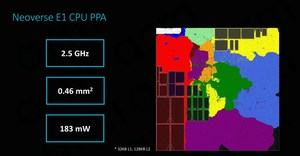

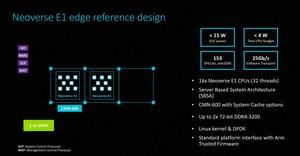

Entsprechend der Auslegung, mehrere Threads gleichzeitig verarbeiten zu können, sind auch die Caches und Prefetch-Einheiten anders ausgelegt. Ausgelegt ist das Neoverse-E1-Design auf SoCs mit bis zu 16 Kernen. Theoretisch sind auch mehr denkbar, die Auslegung des System Level Caches und vieler weiterer Komponenten ist aber auf ein 2x 8-Core-Cluster hin vorgesehen. Unter anderem bietet ein solcher Prozessor ein Dual-Channel-DDR4-3200. Die Leistungsaufnahme des gesamten SoCs soll weniger als 15 W betragen, die Kerne benötigen zusammengenommen nur 4 W – dies zeigt, in welchem Rahmen sich die weiteren Komponenten wie Netzwerk-Interfaces im Power-Budget verhalten.

ARM geht mehr als ambitioniert an die Sache

Eines zeigt sich durch die Vorstellung des Neoverse E1 und Neoverse N1 sicherlich ganz deutlich: ARM meint es ernst mit den Ansprüchen am Servermarkt. Man will nicht mehr nur einen Nischenmarkt bedienen, sondern konkurrenzfähig zu Intel und AMD sein. Vor allem Huawei hat in den vergangenen Monaten gezeigt, dass man mit der Entwicklung eigener Server-Prozessoren mit ARM-Design einen entscheidenden Richtungswechsel vollzogen hat. ARM überführt die dort verwendeten Cortex-Designs in dedizierte Plattformen auf Basis von Neoverse E1 und Neoverse N1.

Die kommenden zwei Jahre werden zeigen müssen, ob sich das Konzept schlussendlich durchsetzen wird. ARM geht davon aus, dass der erste kommerzielle Einsatz der Neoverse-N1-Plattform noch mindestens zwölf Monate dauern wird. Das Serversegment ist recht träge, bis hier ein Plattformwechsel in bestimmten Bereichen vollzogen wird, dauert es mehrere Jahre.