Werbung

Nach einer noch recht offen gehaltenen Ankündigung des Compute Express Link oder kurz CXL hat Intel auf einem Interconnect Day 2019 erste genauere Details zur Technik und dem Einsatzbereich verraten. CXL wird von Intel als ein offener Standard bezeichnet, allerdings wird der Zugang zu den dazu notwendigen Details nicht offen gestaltet. Vielmehr stellt Intel CXL als Konkurrenzprodukt zu CCIX, OpenCAPI und Gen-Z auf.

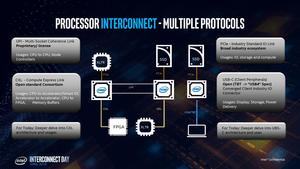

Zunächst einmal hat Intel den CXL in der Hierarchie der Interconnects und Netzwerkverbindungen eingeordnet und spricht davon, dass CXL ein Prozessor-Interconnect ist – also die Verbindung zwischen mehreren Prozessoren, ASICs, FPGAs und GPUs herstellen wird. CXL ist kein Datacenter-Interconnect, der wie InfiniBand oder Ethernet mehrere Knoten untereinander verbindet.

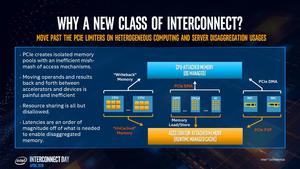

Die Motivation hinter dem CXL ist ganz ähnlich wie die hinter den eben erwähnten Techniken (CCIX, OpenCAPI und Gen-Z) und auch bereits etablierten Interconnects wie NVLink. NVIDIA sieht NVLink als derzeit einzige Möglichkeit, die aktuelle Hardware im Hinblick auf Datenrate, Latenzen und Funktionen wie Speicher-Kohärenz miteinander zu verknüpfen. Im Falle von NVLink gilt dies für die hauseigenen GPUs, von denen sich bis zu 16 zusammenfassen lassen. Intel verfolgt mit CXL einen ähnlichen Ansatz, stellt die Technik aber deutlich breiter auf.

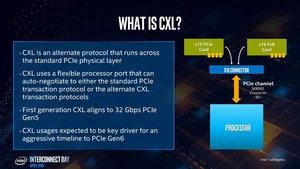

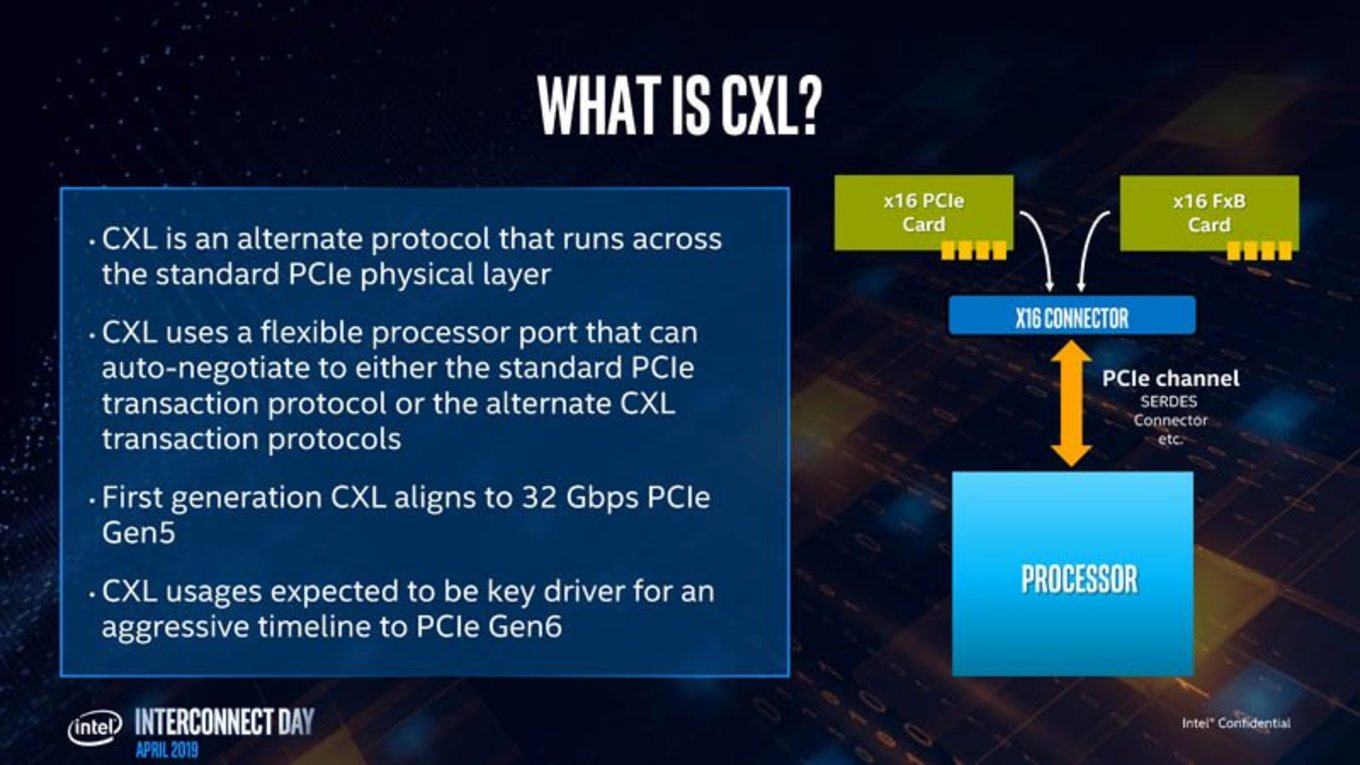

Dies zeigt sich schon durch die Wahl der Übertragungstechnik. Anstatt einer eigenen physikalischen Übertragungstechnik setzt CXL auf PCI-Express. Startpunkt für den Einsatz von CXL soll PCI-Express 5.0 sein. PCI-Express 5.0 wird eine Übertragungsrate von 3,938 GB/s auf einer Lane und 63,01 GB/s auf 16 Lanes ermöglichen. Den Angaben von Intel zufolge wird CXL acht PCI-Express-5.0-Lanes verwenden und kommt damit auf etwa 32 GB/s.

Zum Vergleich: NVLink 2.0 kann 50 GB/s in Sende- und Empfangsrichtung pro Link übertragen und pro GV100-GPU sind bis zu sechs Links möglich.

Intel erwartet allerdings eine schnelle Umsetzung von PCI-Express 6.0 und will damit sicherlich auch der immer höheren Nachfrage hinsichtlich der Datenraten Rechnung tragen.

CXL ist nicht nur ein Interconnect, der auf eine möglichst hohe Datenrate ausgelegt ist, sondern der drei Protokolle in einer Verbindung vereint: CXL.io, CXL.cache und CXL.memory.

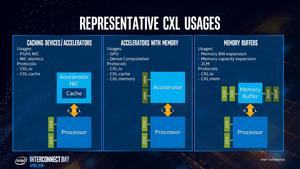

CXL.io stellt die Rückwärtskompatibilität zu PCI-Express her. Damit wird CXL.io das am häufigsten eingesetzte Protokoll sein, weil PCI-Express in Server allgegenwärtig ist und sein wird. CXL.cache ermöglicht den Zugriff auf die Caches eines Xeon-Prozessors. Die Cache-Kohärenz soll zwischen CPUs, FPGAs (beispielweise den neuen Agilex-Chips) und den dann von Intel vorgestellten GPU-Beschleunigern möglich sein. CXL.memory funktioniert in umgekehrter Richtung im Vergleich zu CXL.cache und ermöglicht dem Prozessor Zugriff auf den Speicher der per CXL angebundenen Beschleuniger. CXL.cache und CXL.memory sind auf besonders niedrige Latenzen ausgelegt und arbeiten im CXL-Stack in ihren eigenen Protokollschichten.

Anders als der aktuelle CPU-Interconnect QPI und UPI ist CXL asymmetrisch ausgelegt. Im UPI-Modell sind alle teilnehmenden Prozessoren sozusagen gleichwertig und haben jeweils eigenes Caching und Home Agent. Bei CXL ist dies alles in der CPU vereint und die Gegenstelle muss keine eigenen Caching und Home Agents haben, um im CXL-Netzwerk mitspielen zu können. Dies soll dafür sorgen, dass Intel selbst die teilnehmenden Beschleuniger einfacher gestalten kann, es anderen Herstellern aber auch einfacher gemacht wird einen zu CXL kompatiblen Chip zu entwickeln. Vor allem aber sorgt Intel dafür, das die eigenen Xeon-Prozessoren der zentrale Punkt eines CXL-Netzwerks sind und bleiben.

In einem kohärenten Speichersystem sollen alle Teilnehmer auf einen gemeinsamen Speicher zugreifen können. Dieser Speicher besteht aus der Summe des Speichers, der jedem Teilnehmer zur Verfügung steht. Zwei GPUs mit jeweils 16 GB HBM2 können sich somit 32 GB an Speicher teilen und auf die Speicherbereiche des jeweils anderen zugreifen.

Was auf den ersten Blick einfach klingt, ist aber alles andere als einfach, denn die Zugriffe müssen koordiniert werden und dies sorgt für Verzögerungen in den Speicherzugriffen und erhöht die Latenzen. Selbst wenn die GPU auf den eigenen Speicher zugreifen möchte, ist dies der Fall – nicht nur beim Zugriff auf den Speicher der zweiten GPU. Die Speicherkohärenz bietet also nicht alle denkbaren Freiheiten, sondern ist in gewisser Weise eingeschränkt.

Um dem entgegenzuwirken, sieht Intel verschiedene Zugriffsmethoden vor. So gibt es einen Device Bias, der ohne jegliche Verzögerungen einen Zugriff auf den kohärenten (eigenen) Speicher durch einen Beschleuniger zulässt. Für den Host Bias erfolgt der Zugriff immer über den zentralen Prozessor, was wiederum einige Verzögerungen und nicht die volle Bandbreite in den Zugriffen zur Folge hat. Laut Intel werden Device Bias, also der schnellere Zugriff, aber weitaus häufiger vorkommen, als der Host Bias.

Zusammenfassung

Intel stellt sich mit CXL gegen die Konkurrenzstandards wie CCIX, OpenCAPI und Gen-Z. Allesamt sehen die beteiligten Unternehmen einen Trend zu speicherkohärenten Systemen und dazu sind schnelle und latenzreduzierende Interconnects ein wichtiger Baustein. NVIDIA hat dies mit NVLink bereits vor geraumer Zeit erkannt und sich aufgrund fehlender Technologien einen eigenen Standard geschaffen. Dies tut nun auch Intel mit CXL.

CXL ist für Intel auch ein wichtiger Baustein, um die aktuellen Entwicklungen zusammen zu bringen. Die Xeon-Prozessoren werden CXL als zentrale Instanz in einem Server unterstützten. Per CXL angebunden werden weitere Prozessoren, vor allem aber FPGAs und die dann eigenen GPU-Beschleuniger. Damit CXL in der präsentierten Form funktioniert und umgesetzt werden kann, muss PCI-Express 5.0 umgesetzt sein. Die neuen Xeon-Scalable-Prozessoren der 2. Generation auf Basis der Cascade-Lake-Architektur unterstützen nur PCI-Express 3.0. AMD wird in diesem Sommer mit den EPYC- und Ryzen-Prozessoren der nächsten Generation den Starschuss für PCI-Express 4.0 geben. Intel wird auf diesen Zug erst mit Cooper Lake und Ice Lake irgendwann zum Jahreswechsel 2019/2020 aufspringen. PCI-Express 5.0 wird dann vermutlich erst Ende 2020 oder gar 2021 eingeführt werden und erst dann wird CXL für Intel auch eine Rolle spielen. Die Ankündigung der Agilex-FPGAs mit der Unterstützung für PCI-Express 5.0 zeigt aber, dass Intel sich hier etwas mehr Aggressivität in der Umsetzung wünscht.