Werbung

Mitte Mai des vergangenen Jahres stelle Intel den Neural Network Processor (NNP) Nervana NNP L-1000 alias Spring Crest für 2019 in Aussicht. Nun hat der Chipriese auf der Linley Conference weitere Details zum Design verraten. Bereits bekannt ist, dass der NNP L-1000 ein ASIC-Design mit insgesamt 32 GB an HBM2 ist. Seine Rechenleistung soll die eines Prozessors, aber auch eines GPU-Beschleunigers in bestimmten Bereichen bei weitem überflügeln.

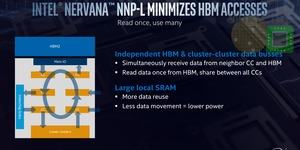

Auf der Linley Conference konnte sich David Schor von Wikichips.org einen weiteren Eindruck verschaffen und ist auch mit weiteren Informationen versorgt worden. Der Nervana NNP L-1000 besteht aus vier Pods zu je sechs Compute Clustern, die alle modernen Matrix-Multiplikationen und Datentypen verarbeiten können. Jeweils ein Pod verfügt über einen Speichercontroller, der wiederum jeweils 8 GB an HBM2 ansteuert. Einen lokalen Cache gibt es nicht, stattdessen verfügt jedes Processing Cluster über vergleichsweise üppige 2 MB an SRAM. Der Speicher ist relativ groß ausgelegt, da die Processing Cluster auf die Berechnung großer Matrizen ausgelegt sind und diese mit 1k x 1k x 1k oder gar 4k x 4k x 4k hinsichtlich ihrer Dimensionen auch viel Speicherplatz benötigen.

Die vier Pods sind über Inter-Chip Links (ICL) miteinander verbunden, die eine bi-direktionale Bandbreite von 100 GB/s erreichen. Es handelt sich dabei um eine Mesh-Topologie für den Interconnect. Zur externen Anbindung mehrerer Chips sieht Intel einen Interconnect mit 300 GB/s vor und will Latenzen von 790 ns und weniger erreichen. Der Nervana NNP L-1000 kann in Nodes zu jeweils vier Chips und dann in Racks zu jeweils zwei Nodes zusammengefasst werden. Ein solches Design sieht also acht dieser Chips auf dem selben PCB vor. Für größere Netzwerke können auch mehrere Racks untereinander verbunden werden. Bis zu 64 Chips sind möglich.

Nervana NNP L-1000? in 16 nm bei TSMC gefertigt

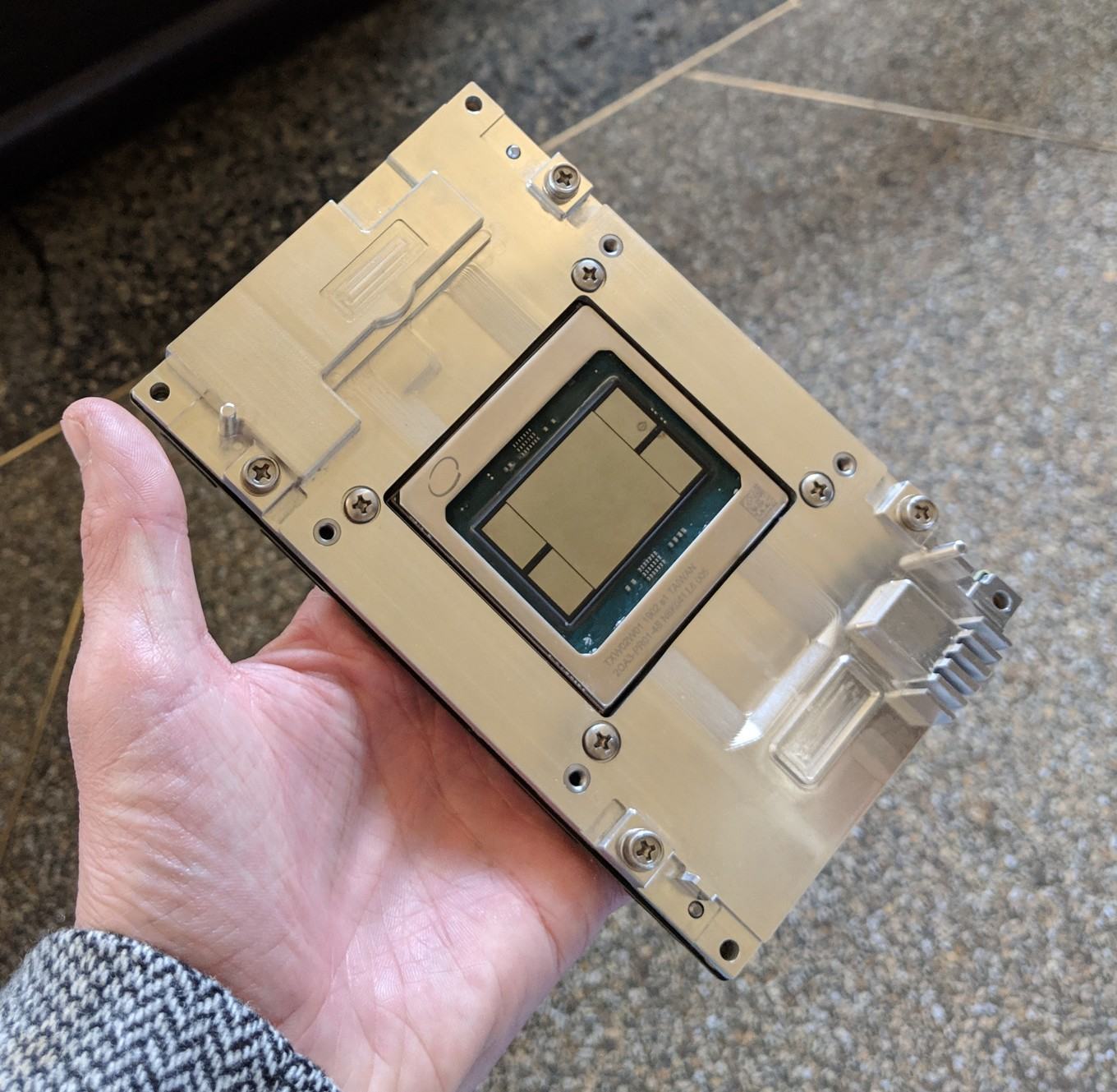

Intel fertigt den Nervana NNP L-1000 nicht selbst, sondern lässt ihn bei TSMC fertigen. Der Chip ist mit 741 mm² relativ groß und wird eigentlich nur noch von NVIDIAs GV100 mit 850 mm² überboten, der auf den Tesla-V100-GPU-Beschleunigern zum Einsatz kommt. Die Thermal Design Power soll bei 210 W liegen, während NVIDIA die TDP auf bis zu 450 W für seine Tesla V100 erhöht hat.

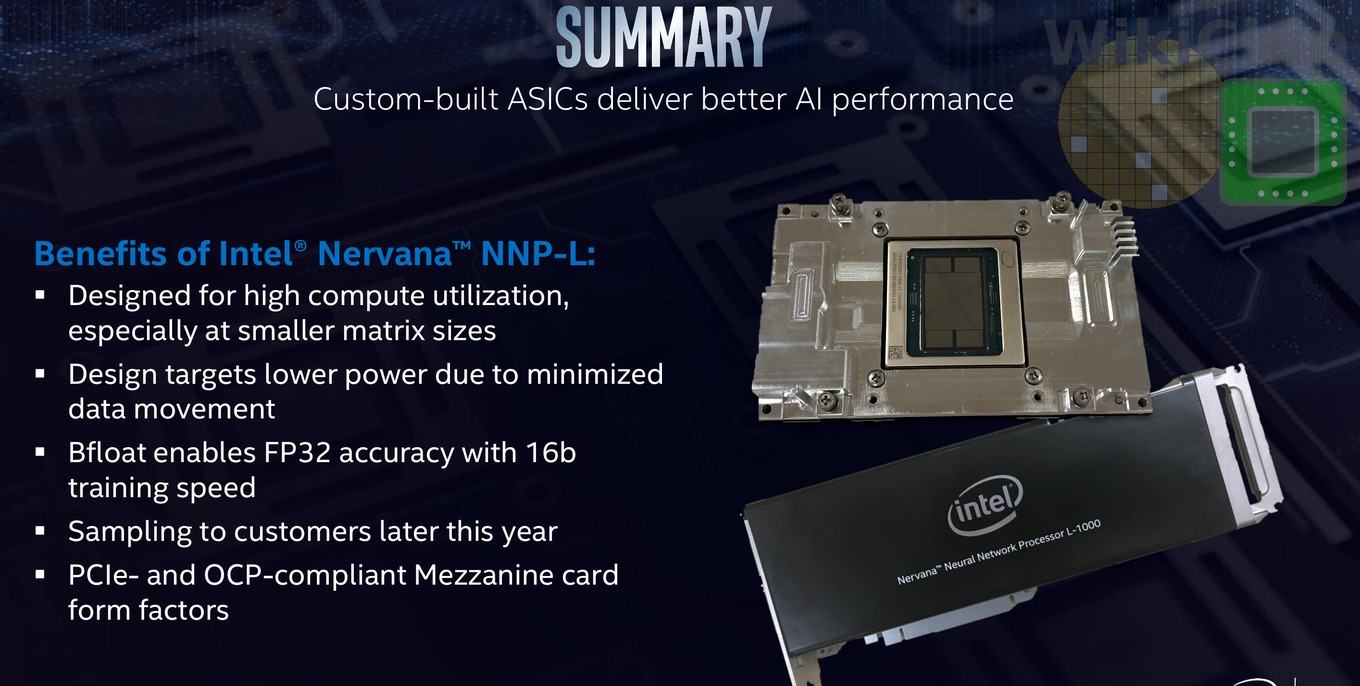

Unter anderem eingesetzt werden soll der Nervana NNP L-1000 in Form des OCP Accelerator Module (OAM). Intel plant aber auch den Chip auf PCI-Express-Karten zu verpflanzen.

Vorteil durch höhere Effektivität und Auslastung

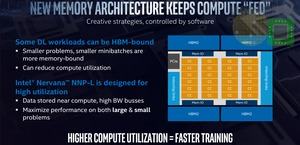

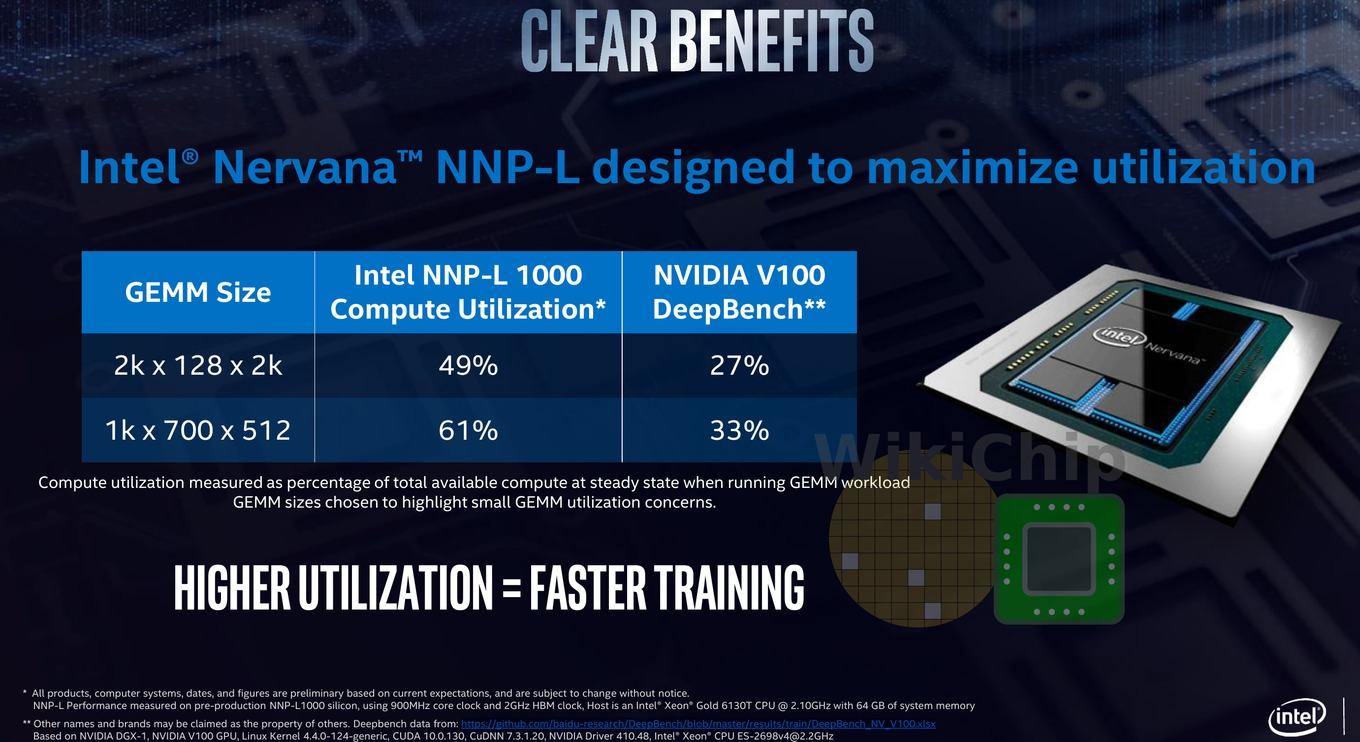

Gerne prahlen die Hersteller mit Angaben zur Rechenleistung. Dies sind aber meist theoretische Werte, die in der Praxis kaum erreicht werden. An diesem Punkt setzt Intel an. Intel sprach Stand Frühjahr 2018 davon mit dem Nervana NNP L-1000 eine Rechenleistung von 36 TFLOPS zu erreichen. Zum Vergleich: NVIDIAs Tesla V100 kommt auf 120 TFLOPS für INT8-Berechnungen, die beim Machine Learning entscheidend sind. Allerdings soll Lake Crest diese 40 TFLOPS bei einer Auslastung von 96 % auch wirklich erreichen, während die Tesla V100 je nach Anwendung auf nur 30 TFOPS und damit eine Auslastung von 25 % kommen soll.

Diese Zahlen hat Intel auf der Linley Conference bestätigt, nennt für andere Größen der General Matrix to Matrix Multiplication (GEMM) nun aber andere Werte. Der Nervana NNP L-1000 soll theoretisch bis zu 120 TFLOPS erreichen, in der Praxis eher im Bereich von 85 TFLOPS liegen, wäre dann aber noch immer schneller als vergleichbare Hardware. Die höhere Auslastung der Hardware schlägt hier also die höhere Grund-Rechenleistung, die ein GPU-Beschleuniger aber nicht in echte Rechenleistung umsetzen kann.

Der Nervana NNP L-1000 wird derzeit in einem B-Stepping evaluiert und soll noch dieses Jahr verfügbar sein.

Nervana NNP I-1000 in 10 nm mit Ice-Lake-Kern

Während der Nervana NNP L-1000 für das Training von Deep-Learning-Netzwerken ausgelegt ist, soll der Nervana NNP I-1000 das Inferencing, also die Auswertung dieser Netzwerke, beschleunigen. Der unter dem Codenamen Spring Hill entwickelte Chip wird dann in 10 nm gefertigt und mit Sunny-Cove-Kern ausgestattet sein. Auch der Nervana NNP I-1000 soll gegen Ende des Jahres ausgeliefert werden.