Werbung

Im Kampf um die nächste offene Interconnect-Technologie hat Compute Express Link (CXL) weiteren prominenten Zuwachs bekommen. ARM ist nun ebenfalls Mitglied und wird CXL für zukünftige Produkte einplanen. Zuletzt traten auch AMD und NVIDIA bei. Neben Intel sind damit die drei größten Prozessoren- und GPU-Hersteller vertreten.

Die Ankündigung von ARM ist vor allem im Hinblick auf die Vorreiterschaft bei den Interconnect-Technologien interessant. Bisher unterstützte ARM vor allem CCIX.

"We expect to maintain CCIX to support inter-package chip-to-chip interface that is currently not in the scope of CXL. We will continue to support customer solutions based on existing CCIX hardware."

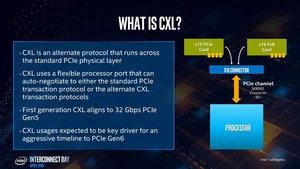

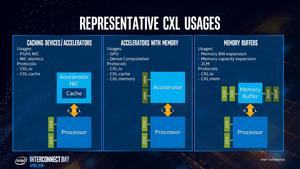

Außerdem gibt Synopsys bekannt, dass man den ersten CXL-Controller, PHY (Physical Layer) und eine Lösung zur Verifikation entsprechender IP auf Basis von CXL 1.1 fertiggestellt hat. Unterstützt werden alle drei Protololle CXL.io, CXL.cache und CXL.mem. Auf physikalischer Ebene verwendet Synopsys die eigene PCI-Express 5.0 IP. Der CXL-Controller besitzt ein 512 Bit breites Interface, welches die 16 Lanes von PCI-Express 5.0 verwendet. Der PHY erreicht die vollen 32 GT/s.

Die Synopsys' 32G PHY IP für CXL steht für 16 nm, 10 nm und 7 nm im FinFET-Prozess zur Verfügung. Die Controller- und Verifikations-IP steht ab sofort zur Verfügung.

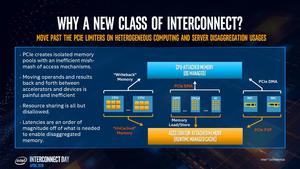

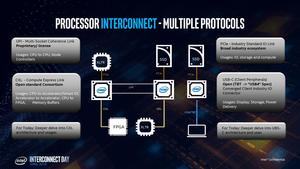

CXL soll den Bedarf an Bandbreite und Speicherkohärenz in zukünftiger Hardware decken können. Diese wird zwischen den Prozessoren, FPGAs, GPUs und anderen an einem High-Performance-Computing beteiligten Systemkomponenten benötigt. CXL wird dabei auf PCI-Express 5.0 basieren. Der Standard ist inzwischen final festgeschrieben und erreicht 32 GT/s bzw. 63 GB/s bei einer Breite von 16 Lanes. PCI-Express 6.0 wird schon 2021 erwartet. Da PCI-Express als physikalische Trägertechnologie von CXL verwendet wird, ist die schnelle Folge der Versionen 5.0 und 6.0 wohl eine Folge des hohen Bedarfs in diesem Bereich.

Die Wahl von PCI-Express als physikalischem Träger von CXL soll die beteiligten Unternehmen in die Lage versetzen, schnell und einfach eine Umsetzung der Technologie zu ermöglichen. Eigene Trägertechnologien für neue Protokolle bauten in dieser Hinsicht unnötige Hürden auf – so Intel. CXL besteht aus drei Protokollebenen: Einem I/O-Protokoll, einem Speicher-Protokoll und einem kohärenten Interface.