Werbung

Von gleich zwei Seiten kamen gestern Meldungen auf, die von weiteren Verzögerungen im 10-nm-Prozess bei Intel sprachen. Bei SemiAccurate war sogar die Rede von einer Verzögerung der kompletten Server-Roadmap – inklusive der noch ausstehenden 14-nm-Produkte. Aber auch ein Analyst von Wells Fargo will entsprechende Quellen aufgetan haben.

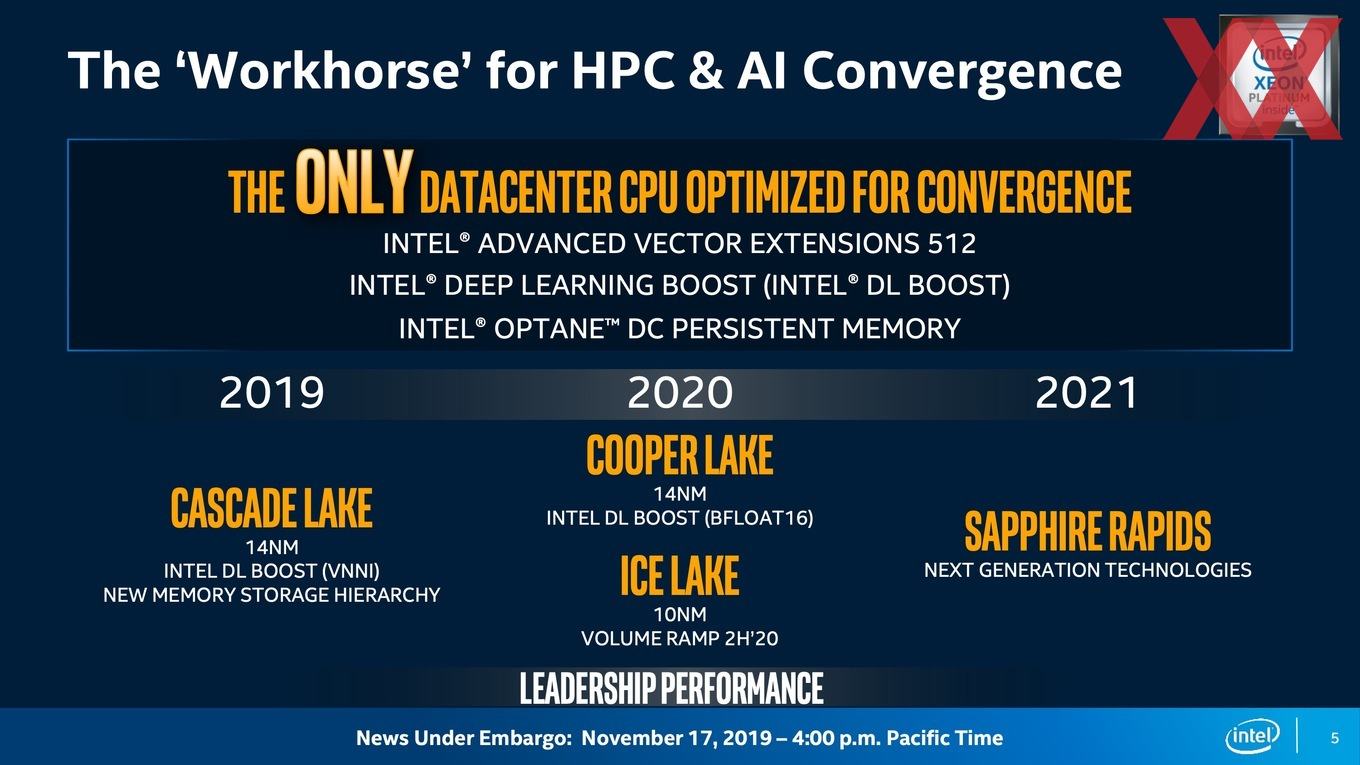

Eigentlich sollen in diesem Frühjahr die Xeon-Prozessoren auf Basis von Cooper Lake auf den Markt kommen. In der zweiten Jahreshälfte sollen dann die ersten 10-nm-Xeons auf Basis von Ice Lake folgen. Für Cooper Lake wird derzeit mit bis zu 56 Kernen pro Sockel ausgegangen. Wie Intel dies umsetzen wird (eventuell analog zu den Cascade-Lake-AP-Prozessoren), ist derzeit nicht bekannt. Die Xeons auf Basis von Ice Lake sollen bis zu 28 Kerne bieten. Es wurden aber auch schon Angaben von bis zu 38 Kernen gesehen. Die Verzögerungen sollen sich sowohl auf Cooper Lake als auch auf Ice Lake beziehen. Während erstgenannte Prozessoren nun erst in der zweiten Jahreshälfte 2020 erscheinen sollen, könnten sich die Ice-Lake-Modelle auf 2021 verschieben - so die Berichte.

Gegenüber Tomshardware hat sich Intel nun zu den Meldungen geäußert:

"Intel remains on track for delivery of the Whitley platform starting with production of Cooper Lake in H1 2020 followed by Ice Lake production in H2 2020. We are also on track to follow Whitley with the delivery of Sapphire Rapids in 2021."

Intel spricht davon, weiterhin im Plan zu sein. Demnach werden die Cooper-Lake-Xeons in der ersten Jahreshälfte in die Produktion gehen und die Ice-Lake-Modelle sollen in der zweiten Jahreshälfte folgen. Intel spricht hier aber vom Start der Produktion und nicht der Verfügbarkeit, was etwas Spielraum offen lässt.

Zuletzt äußerte sich Intel auf der UBS Global TMT Conference in Form ihres Chefs der Technology, Systems Architecture & Client Group Dr. Murty Renduchintala wie folgt:

"And of course by the end of 2020, we'll come out with Ice Lake, our first 10nm server solution that brings important performance-per-core benefits to the surface. So all in all, I think we have an aggressive roadmap that we feel pretty good about to deal with the competitive landscape."

Die Vergangenheit hat allerdings gezeigt, dass sich bei Intel derzeit vieles im Fluss befindet. Noch vor einigen Monaten sollten die Xeon-Prozessoren auf Basis von Cooper Lake bereits Ende 2019 ausgeliefert werden. In diesem Jahr wird dies aber nicht mehr geschehen. Einige OEMs und ODMs arbeiten noch mit Pre Production Samples, also noch vor der Qualification-Sample-Phase. Die Auslieferung Ende 2019 war spätestens seit dem Frühjahr 2019 nicht mehr einzuhalten und dementsprechend änderten sich auch die Angaben von Intel. Anfang 2020 sind das neue Ziel. Nun spricht Intel von der ersten Jahreshälfte 2020.

Bereits 2021 steht der Nachfolger Sapphire Rapids auf der Roadmap. Hier sollen dann die neuen Willow-Cove-Kerne zum Einsatz kommen. Daneben sollen die Xeon-Prozessoren auf Basis von Sapphire Rapids DDR5 und PCI-Express 5.0 unterstützen.

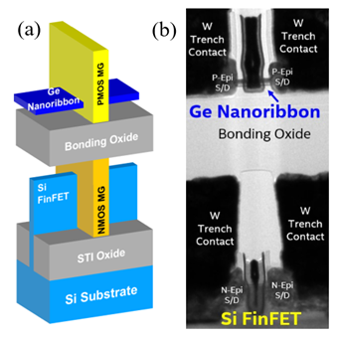

GAAFETs, Nanowires und Nanoribbons

Im Rahmen des IEEE International Electron Devices Meeting (IEDM) veröffentlichte Robert Chau, Intel Senior Fellow und Director, Components Research bei Intel einen Blogpost auf Medium. In diesem Beschreibt er die aktuellen Entwicklungen hinsichtlich der Verwendung neuer Materialien in den Transistoren. Durch ein Monolithic Scaling und gleichzeitiges System Scaling soll Moore’s Law über das nächste Jahrzehnt weiter Bestand haben.

Wie auch TSMC und Samsung arbeitet Intel derzeit an der Umsetzung der Gate-All-Around (GAA) FETs. Bei diesen wird ein ähnliches Konzept wie bei den klassischen FinFETs verwendet, allerdings umschließt das Gate-Material den stromführenden Kanal vollständig. In einem nächsten Schritt sollen die 3D-FinFETs mit Nanowire (Nanodrähten) oder Nanoribbons (Nanobändern) übereinander gestapelt werden, was eine wesentlich höhere Packdichte und Anzahl zulässt. Dabei kommt unter anderem Germanium zum Einsatz. Dies soll höhere Taktraten der Transistoren zulassen, ist aber wohl in der Integration des Materials nicht ganz einfach.

Weitere Details, vor allem zur Skalierung im System über die Verwendung multipler Chips, die per schnellem Interconnect miteinander verbunden sind, gibt es im Blogpost bei Medium.