Werbung

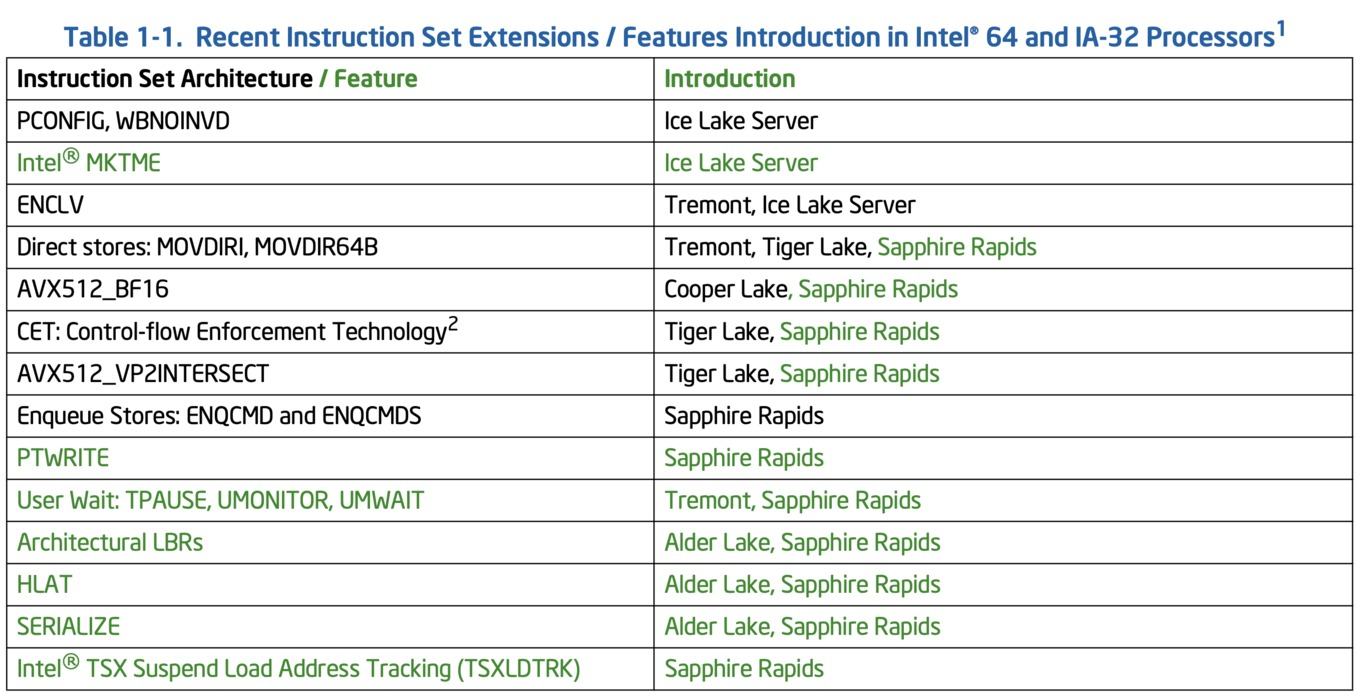

Intel hat ein neues Benutzerhandbuch für die eigene Befehlssatzarchitektur (Instruction Set Architecture oder kurz ISA) veröffentlicht. Dieses kann von Softwareprogrammierern als Anleitung genommen werden, welche Befehlssätze in zukünftigen CPU-Generationen unterstützt werden. Das auf den März 2020 datierte Manual (die 3. Edition) enthält unter anderem Hinweise auf Alder Lake und Sapphire Rapids.

Als Teil der ISA wird Sapphire Rapids BFLOAT16 unterstützen. Neben den eigenen Agilex-FPGAs soll dies vor allen in den in Kürze erwarteten Xeon-Prozessoren auf Basis von Cooper Lake Verwendung finden. Es deutete sich bereits an, dass die Ice-Lake-Xeons BFLOAT16 nicht unterstützen werden. Das ISA von Intel bestätigt dies nun. Cooper Lake wird ausschließlich für 4S- und 8S-Server angeboten werden. Die kleineren 1S- und 2S-Server wird Intel ausschließlich mit Ice Lake bedienen.

BFLOAT16 (Binary Floating Point mit 16 Bit) wird vor allem für das Training von Deep-Learning-Netzwerken verwendet. Das Gleitkommaformat bietet die gleiche Dynamik wie FP32-Berechnungen, kann aber deutlich schneller ausgeführt werden. Google setzt BFLOAT16 in den eigenen TPUs bereits ein.

Wer mit BFLOAT16 plant, wird nach Cooper Lake auf Sapphire Rapids warten müssen. Cooper Lake ist aber wie gesagt auf größere Server mit vier oder acht Sockel ausgelegt. Xeon-Prozessoren auf Basis von Sapphire Rapids sollen 2021 erstmals im Aurora-Supercomputer zum Einsatz kommen. Hinzu werden die HPC-Beschleuniger auf Basis der Xe-HPC-Architektur alias Ponte Vecchio kommen.

Zumindest einmal erwähnt wird auch Alder Lake. Alder Lake wird der Nachfolger von Tiger Lake sein. Für Alder Lake werden allerdings noch keine speziellen Befehlssätze genannt. In Teilen nennt Intel jedoch die Unterstützung von LBR (Last Branch Recording) und HLAT (Hypervisor-managed Linear Address Translation), was auch für Sapphire Rapids Gültigkeit hat.

Alder Lake wird aber nur grob umrissen und zumindest einmal erwähnt. In der nächsten Version des ISA-Manual wird Intel dann sicherlich weitere Details dazu verraten, so dass Softwareentwickler sich genauer darauf vorbereiten können.