Werbung

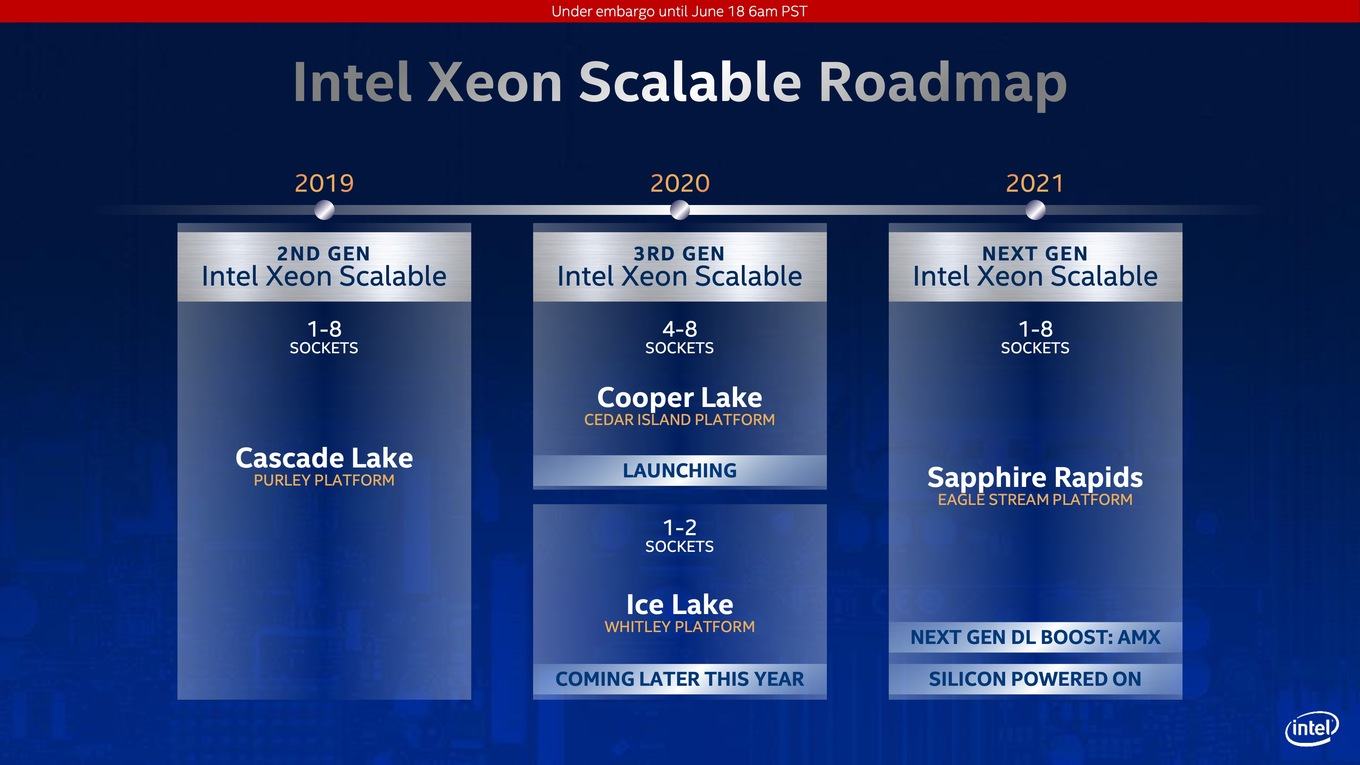

Nach der zweiten Generation der Xeon Scalable Prozessoren auf Basis von Cascade Lake stellt Intel heute die dritte Generation vor. Diese basiert auf dem Cooper-Lake-Design und richtet sich vor allem an Hyperscaler mit AI- und datenintensiven Anwendungen. Cooper Lake-SP wird es ausschließlich für Server mit vier oder acht Sockeln geben. Für kleinere Server sieht Intel in diesem Jahr den Wechsel auf Ice Lake-SP vor.

Die Purley-Plattform für Cascade Lake-SP wird also von gleich zwei Plattformen abgelöst, die aber nicht parallel verlaufen, wie dies ursprünglich geplant war. Vor einigen Wochen verkündete Intel, dass man Cooper Lake-SP auf größere 4S- und 8S-Server beschränken wird (Cedar-Island-Plattform) und im Gegenzug Ice Lake-SP (Whitly-Plattform) auf 1S- und 2S-Servern arbeiten wird. Erst 2021 sollen die beiden Plattformen auf der Eagle-Stream-Plattform zusammengeführt werden.

Die dazugehörigen Xeon-Prozessoren auf Basis von Sapphire Rapids sollen dann wieder Server mit einem bis acht Sockeln bedienen. Mit Sapphire Rapids wird es auch wieder eine neue DL-Boost-Erweiterung geben. Intel AMX steht für Advanced Matrix Extension – analog zu AVX (Advanced Vector Extension). Weitere Details werden sicherlich im kommenden Jahr folgen. Intel hat die ersten Prototypen von Sapphire Rapids aus der Fertigung erhalten und in Betrieb genommen. Man liegt hier also im Zeitplan.

Bisher unbestätigt: Die Prozessoren auf Basis von Sapphire Rapids werden die Willow-Cove-Architektur verwenden und in 10 nm gefertigt werden. Zudem werden sie DDR5 und PCI-Express 5.0 unterstützen. Auch im Bereich der Optane DC DIMMs wird es mit Sapphire Rapids Neuerungen geben. Diese sehen wir nun aber auch mit Cooper Lake und damit wollen wir den Blick auf das konzentrieren, was Intel heute anzukündigen hat.

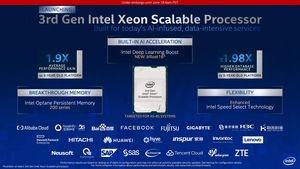

Cooper Lake: 28 Kerne pro CPU

Zunächst einmal sprach Intel immer davon die Anzahl der Kerne pro Sockel mit Cooper Lake erhöhen zu wollen. Die heute vorgestellten Modelle zeigen davon aber nichts mehr, denn wir sehen maximal 28 Kerne pro Prozessor. In einem 4S-Server bedeutet dies bis zu 112 Kerne und in einem 8S-Server entsprechend bis zu 224 Kerne. Ob es auch Cooper-Lake-AP-Prozessoren geben wird, ist nicht bekannt. Mit Cascade Lake-AP setzte Intel zwei Cascade-Lake-SP-Dies zusammen und bot somit ein MCM-Design mit bis zu 56 Kernen pro Sockel an.

Die grundsätzliche Microarchitektur basiert noch immer auf der Skylake-Architektur, die inzwischen aber zahlreiche Anpassungen erhalten hat. Bereits beim Wechsel des ursprünglichen Skylake-Designs zu Cascade Lake gab es einige kleinere Änderungen – hauptsächlich im Bereich des Speichercontrollers, der Mitigation von Sicherheitslücken und bei den speziellen Befehlsätzen für DL-Boost.

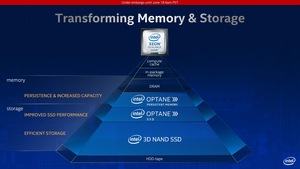

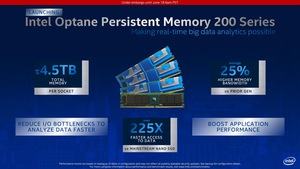

Cooper Lake-SP bietet also bis zu 28 Kerne mit einem 1 MB großen L2-Cache, 32 kB L1D- und 32 L1I-Cache pro Kern. Hinzu kommt ein L3-Cache, der 1,375 MB pro Kern groß ist. Der Speichercontroller bleibt bei sechs Kanälen, die nun aber je nach Modell und Bestückung DDR4-3200 ansprechen können. In diesen Speicherkanälen kann auch eine neue Generation der Optane DC DIMMs eingesetzt werden: Intel Optane Persistant Memory 200 Series. Dazu aber in einer gesonderten Meldung mehr.

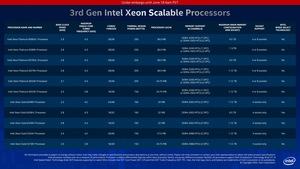

| Modell | Kerne | Basis- / Boost-Takt | Cache | RAM | TDP | Sockel |

| Xeon Platinum 8380HL | 28 | 2,9 / 4,3 GHz | 38,5 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 4,5 TB | 250 W | 4S und 8S |

| Xeon Platinum 8380H | 28 | 2,9 / 4,3 GHz | 38,5 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 1,12 TB | 250 W | 4S und 8S |

| Xeon Platinum 8376HL | 28 | 2,6 / 4,3 GHz | 38,5 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 4,5 TB | 205 W | 4S und 8S |

| Xeon Platinum 8376H | 28 | 2,6 / 4,3 GHz | 38,5 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 1,12 TB | 205 W | 4S und 8S |

| Xeon Platinum 8354H | 18 | 3,1 / 4,3 GHz | 24,75 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 1,12 TB | 205 W | 4S und 8S |

| Xeon Platinum 8353H | 18 | 2,5 / 3,8 GHz | 24,75 MB | DDR4-3200 (1 DPC), DDR4-2933 (2 DPC), bis zu 1,12 TB | 150 W | 4S und 8S |

| Xeon Gold 6348H | 24 | 2,3 / 4,2 GHz | 33 MB | DDR4-2933 (2 DPC), bis zu 1,12 TB | 165 W | 4S |

| Xeon Gold 6328HL | 16 | 2,8 / 4,3 GHz | 22 MB | DDR4-2933 (2 DPC), bis zu 4,5 TB | 165 W | 4S |

| Xeon Gold 6328H | 16 | 2,8 / 4,3 GHz | 22 MB | DDR4-2933 (2 DPC), bis zu 1,12 TB | 165 W | 4S |

| Xeon Gold 5320H | 20 | 2.4 / 4,2 GHz | 27,5 MB | DDR4-2666 (2 DPC), bis zu 1,12 TB | 150 W | 4S |

| Xeon Gold 5318H | 18 | 2,5 / 3,8 GHz | 24,75 MB | DDR4-2666 (2 DPC), bis zu 1,12 TB | 150 W | 4S |

Zunächst einmal ein paar Worte zur Namensgebung der Cooper-Lake-Xeons. Diese verwenden alle eine drei an der zweiten Stelle der Modellnummer und ebenfalls eine H-Erweiterung. Die L-Modelle sind solche mit einer erweiterten Speicherunterstützung. Ob die Speed-Select-Technologie unterstützt wird, ist anhand der Namensgebung aber nicht mehr zu erkennen. Alle Modelle unterstützen Hyperthreading und können damit doppelt so viele Threads verarbeiten, wie Kerne vorhanden sind.

Das Topmodell der Cooper-Lake-Generation ist der Xeon Platinum 8380HL mit 28 Kernen, einem Basis-Takt von 2,9 GHz und einem Single-Core-Turbo von 4,3 GHz. Im Vergleich zum Vorgänger Xeon Platinum 8280L steigert Intel den Basis-Takt um 200 MHz und den Boost-Takt um 300 MHz. Dafür steigt die Thermal Design Power aber auch von 205 auf 250 W an. Über die sechs Kanäle des Speicherinterface können bis zu 4,5 TB an Arbeitsspeicher angesprochen werden. Bei einem Speichermodul pro Kanal kann DDR4-3200 eingesetzt werden, für den Maximalausbau mit zwei Modulen pro Channel aber nur DDR4-2933.

Die unterschiedlichen Anforderungen an 4S- und 8S-Server sorgen auch dafür, dass wir eine recht übersichtliche Produktpalette für Cooper Lake-SP sehen. Intel ersetzt hier einige Cascade-Lake-Modelle, wird andere aber weiterführen bis die Ice-Lake-Xeons vorgestellt werden. Entsprechend sehen wir hier Modelle mit 16 bis 28 Kernen.

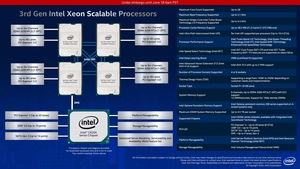

Die Cedar-Island-Plattform bietet die Möglichkeit vier bis acht Prozessoren zusammenzupacken. Jeweils vier Prozessoren werden per UPI untereinander verbunden. Pro Prozessor werden sechs UPI-Links mit bis zu 10,4 GT/s verwendet, so dass jeder Prozessor mit den drei weiteren über jeweils zwei Links verbunden ist.

Pro Prozessor werden 48 PCI-Express-3.0-Lanes zur Verfügung gestellt. Der C620A-Chipsatz ist per DMI 3.0 an einen der Prozessoren angebunden. Der Chipsatz stellt 20 weitere PCI-Express-Lanes bereit. Hinzu kommen bis zu 10x USB 3.0 und 14x SATA III. Über den Chipsatz werden auch viele der Management-Funktionen bereitgestellt.

Cooper Lake legt den Fokus auf BFLOAT16

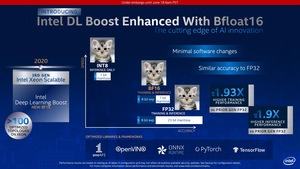

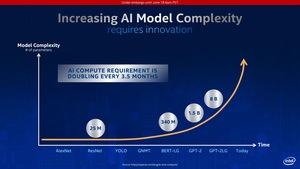

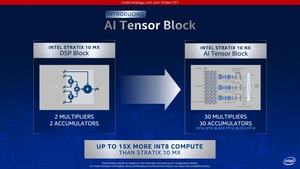

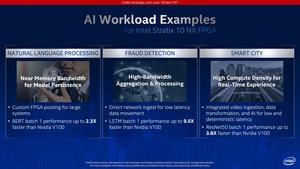

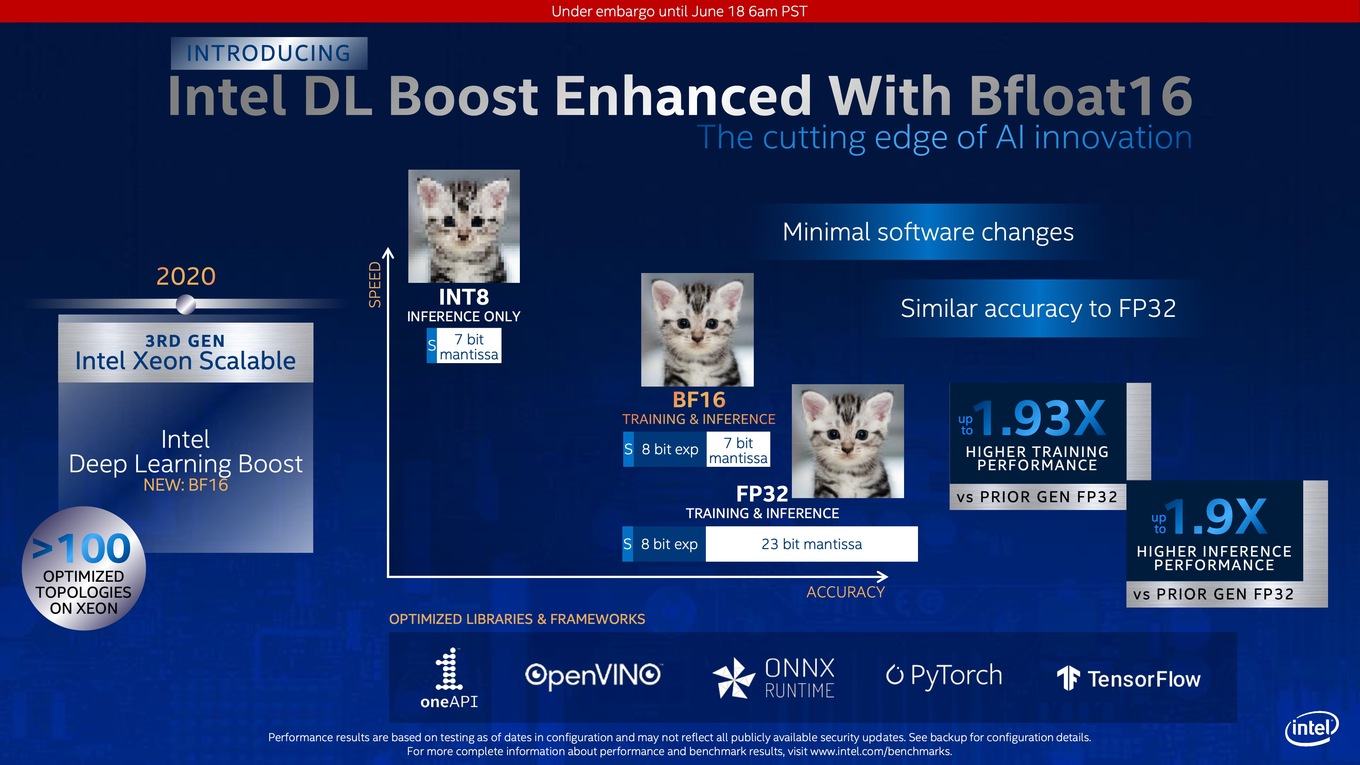

Mit Cooper Lake-SP legt Intel den Fokus auf eine Erweiterung der Instruktion namens AVX-512 Vector Neural Network Instructions (AVX512 VNNI). Die als AVX-512 BF16 bezeichnete Befehlserweiterung unterstützt den bereits bekannten Datentyp BFLOAT16. Intel verweist an der Stelle auf die stetige Weiterentwicklung in diesem Bereich. Mit der ersten Generation der Xeon-Scalable-Prozessoren führte man AVX-512 ein, darauf folgte DL-Boost mit INT8-Beschleunigung in der zweiten Generation der Xeon-Scalable-Prozessoren.

BFLOAT16 hingegen verkürzt die Matisse auf 7 Bit, bei ähnlicher Genauigkeit wie FP32. Die Daten können durch die größeren Recheneinheiten aber deutlich schneller verarbeitet werden. BFLOAT16 soll sich sowohl für das Inferencing als auch das Training von Deep-Learning-Netzwerken eignen. Im Vergleich zum Training und Inferencing auf Basis von FP32 soll sich die Leistung fast verdoppeln.

Zusammen mit den Tensor Cores der dritten Generation führt NVIDIA kürzlich mit der Ampere-Architektur ein neues Gleitkommaformat ein. TF32 oder Tensor Float 32 soll den Wertebereich von FP32 aufweisen, dabei aber nur die Genauigkeit von FP16 verwenden. NVIDIA kombiniert hier also die Vorteile aus FP32 und FP16 und passt diese den Bedürfnissen in bestimmten Bereichen an.

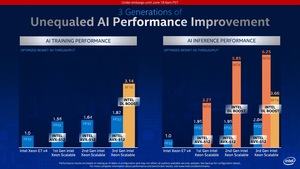

Intel nennt auch noch weitere Leistungsdaten und vergleicht dabei die drei Generationen der Xeon-Scalable-Prozessoren. BFLOAT16 wird vor allem für das Training verwendet werden. Im Inferencing-Bereich wird INT8 weiterhin vorrangig verwendet werden. Ob und in welchen Bereichen es auch Sinn macht, BFLOAT16 für das Inferencing zu verwenden, ist uns nicht bekannt. Intel bietet aber zumindest entsprechende Benchmarks.

Zur Verwendung von BFLOAT16 sagt Intel, dass nur geringe Änderungen an der Software vorgenommen werden müssen, damit der neue Datentyp unterstützt wird. Anwendungen, die schon mit der DL-Boost-API sprechen, sollen auch recht schnell um den neuen Datentyp erweitert werden. Intel stellt mit der OneAPI, OpenVINO und den Select Solutions die entsprechenden Schnittstellen zur Verfügung.

Speed Select Technology (SST)

Drei Modelle der Cooper-Lake-Prozessoren unterstützen die Speed Select Technology. Bei diesen handelt es sich um den Xeon Gold 6328HL, Xeon Gold 6328H und Xeon Gold 5320H. SST erlaubt es einer bestimmten Anzahl an Kernen besonders hoch zu takten. Dafür werden andere heruntergetaktet. Es gibt aber auch bestimmte Workloads, die sich auf einen gewissen Basistakt verlassen müssen, weil die Berechnung der Leistung entsprechend ausgelegt ist. Per Speed Select Technology lässt sich die Hardware auch hier besser steuern.

Die dritte Generation der Xeon-Scalable-Prozessoren werden bereits an die ersten Kunden ausgeliefert. Facebook gilt als einer der wichtigsten Abnehmer für diese Generation. Natürlich aber werden auch OEMs und ODMs Server mit den Cooper-Lake-Prozessoren anbieten und zahlreiche weitere Cloud-Anbieter diese Prozessoren einsetzen.