Werbung

Eine weitere Neuvorstellung von Intel im heutigen Rahmen ist eine neue Serie von FPGAs. Die Stratix 10 NX-Serie richtet sich an AI-Anwendungen, genau wie die Befehlssatzerweiterungen in Cooper Lake oder die neuen SSDs der D7-Serie. Allerdings muss man sich zunächst einmal Intels komplette Produktpalette anschauen, denn diese ist bei den Stratix 10 FPGAs schon recht komplex.

Die FPGAs vom Typ Stratix 10 GX richten sich an Anwendungsbereiche, die eine hohe Rechenleistung im Anforderungsprofil haben. Bis zu 10 TFLOPS liefern die stärksten Ausbaustufen der Stratix 10 GX FPGAs. Bei den Stratix 10 SX SoCs sind bis zu vier Cortex-A53-Kerne vorhanden, die spezielle Aufgaben übernehmen können. Die Stratix 10 TX FPGAs sind für Netzwerkanwendungen vorgesehen. Eine echte Speziallösung sind die Stratix 10 DX FPGAs, die sozusagen ein Bindeglied zwischen Xeon-Prozessorn und speziellen ASICs sein können. Unter anderem unterstützen sie PCI-Express 4.0, etwas was man bei den Xeon-Prozessor noch immer vergebens sucht. Bisher auf AI-Anwendungen ausgelegt sind die Stratix 10 MX FPGAs. Diese werden nun von der neuen Stratix 10 NX Serie abgelöst.

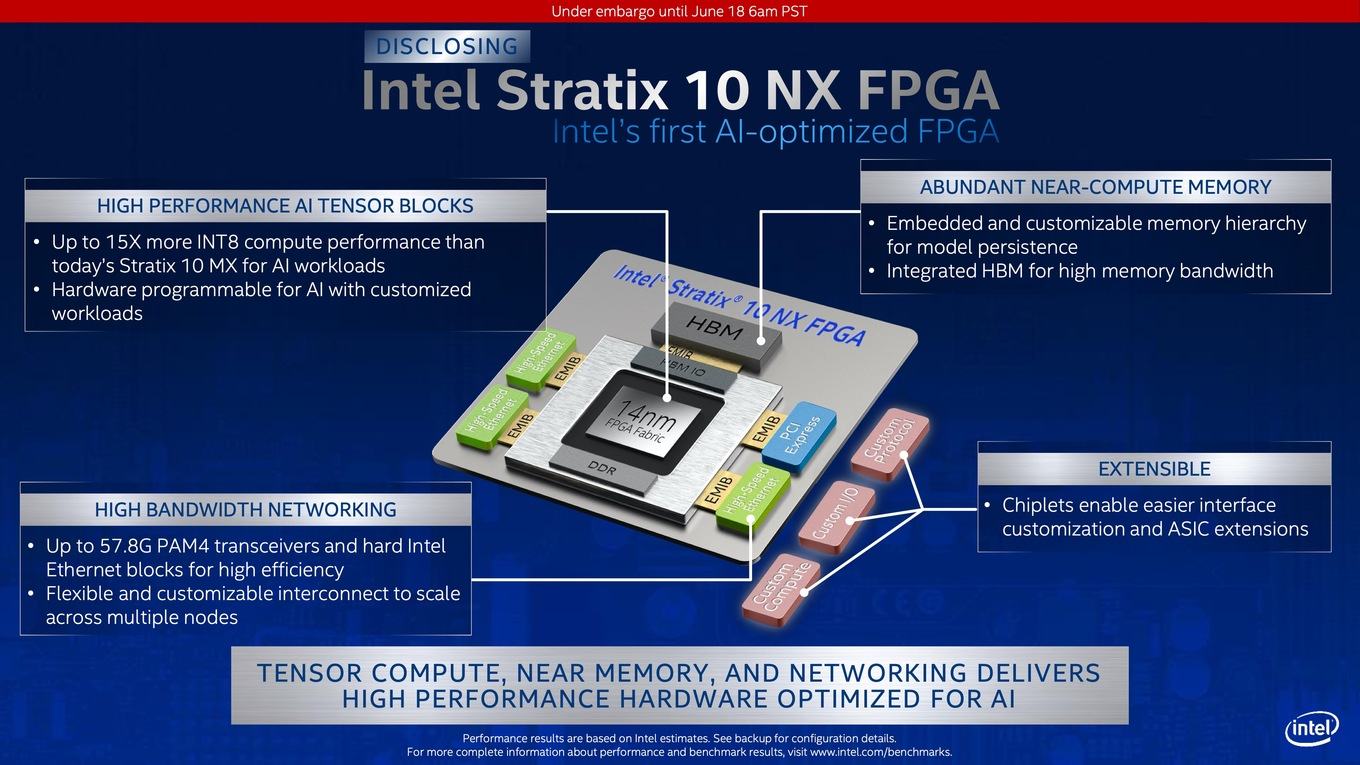

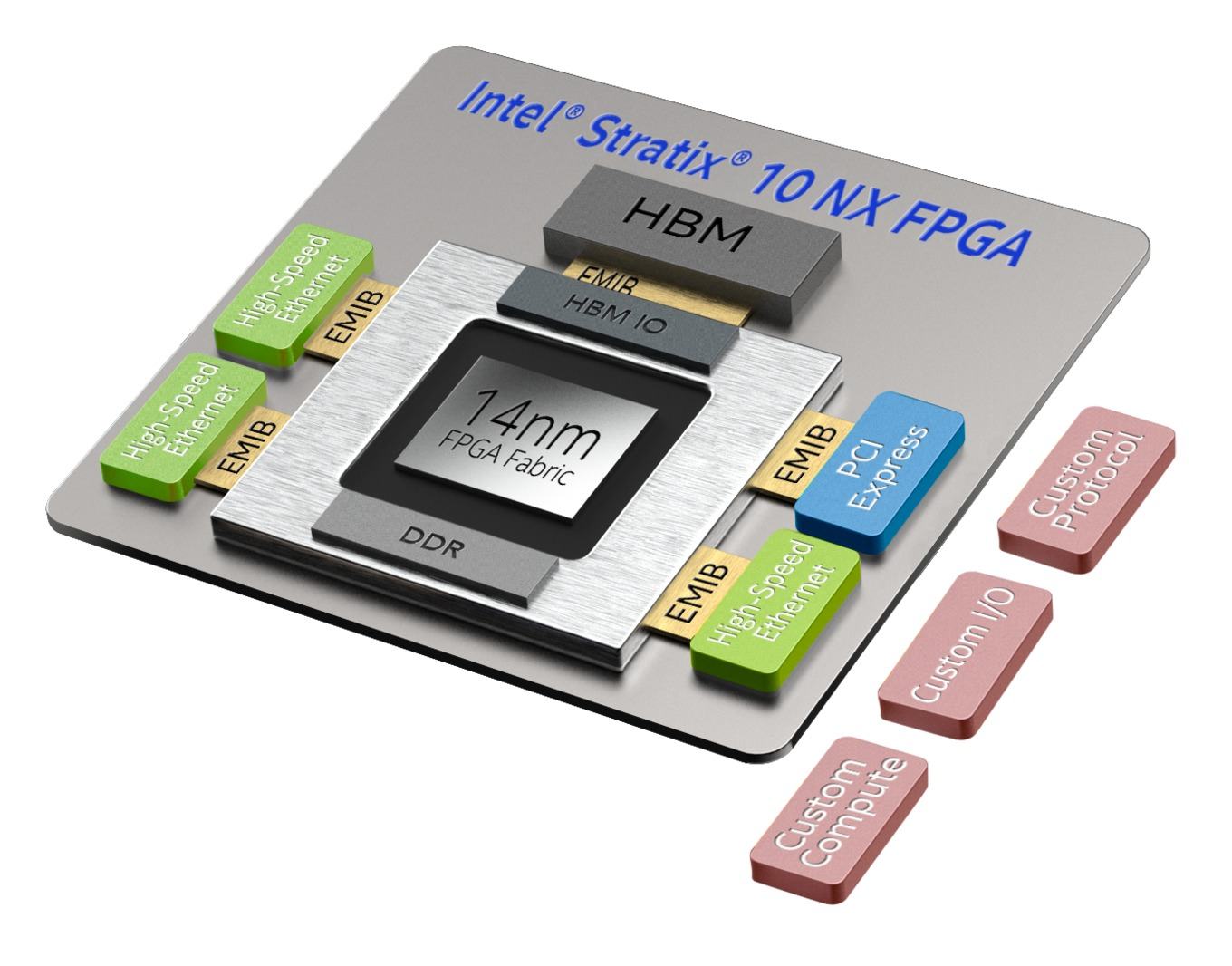

Die nun neuen Stratix 10 NX FPGAs sind klar auf das Inferencing von Deep-Learning-Netzwerken ausgelegt. Dazu verwenden sie spezielle Tensor Blocks, die eine um den Faktor 15 höhere INT8-Rechenleistung gegenüber den Stratix 10 MX FPGAs bieten. In diesem Bereich ebenfalls wichtig ist die schnelle Anbindung von Speicher. Dazu verwendet Intel in der NX-Serie schnellen HBM2-Speicher, der per Embedded Multi-die Interconnect Bridge (EMIB) angebunden ist. Dies gilt auch für schnelle Netzwerkreceiver, die per 57.8G PAM4 eine extrem schnell und latenzarme Netzwerkanbindung ermöglichen.

Wie auch bei den anderen Stratix-Serien wird es die Stratix 10 NX FPGAs in unterschiedlichen Ausführungen geben. Dies betrifft die Anzahl der Logikelemente ebenso wie den Speicherausbau oder IP-Blocks für GXE-, GXT- und GX-Transceiver sowie PCI-Express und Ethernet. Hier wird Intel sicherlich je nach Anforderung entsprechend variieren, um den Markt bestmöglich abzudecken.

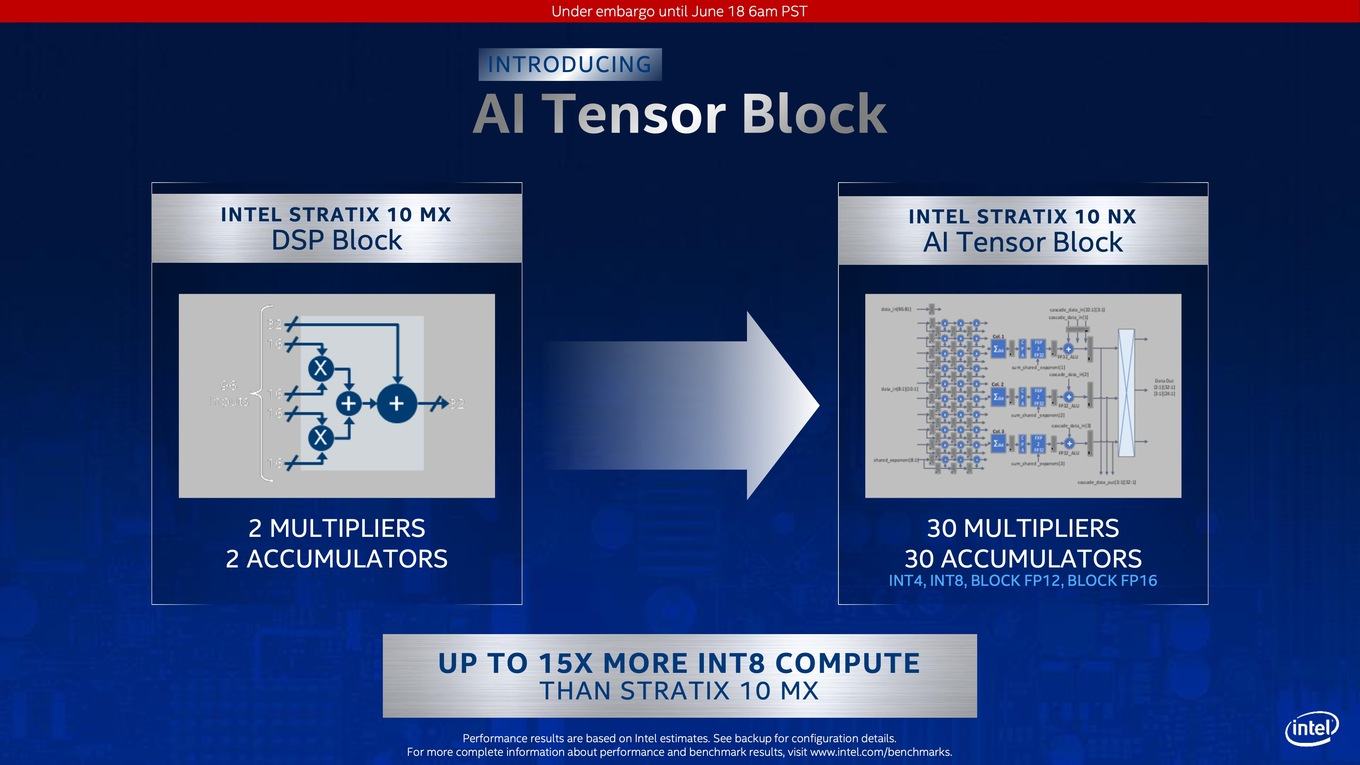

Intels AI Tensor Blocks

Um die hohe Rechenleistung zu erreichen, verwendet Intel neue Tensor Arithmetic Blocks, die eben als AI Tensor Blocks bezeichnet werden. Bei den Stratix 10 MX FPGAs verwendet Intel hier DSP-Blöcke, die jeweils zwei Mulitplikationen und Akkumulationen ausführen können. Die neuen AI Tensor Blocks ermöglichen 30 Multiplikationen und ebenfalls 30 Akkumulatoren – daher die theoretische Leistungssteigerung um den Faktor 15.

Die AI Tensor Blocks haben eine Basisgenauigkeit von INT8 sowie INT4 und unterstützen die numerischen Formate FP16 und FP12. Alle Additionen oder Akkumulationen können mit INT32 oder IEEE754 Single Precision Floating Point (FP32) durchgeführt werden und mehrere AI Tensor Blocks können zur Unterstützung größerer Matrizen kaskadiert, sprich zusammengeschaltet, werden.

Stratix-FPGAs technisch immer interessant

Während die wenigsten Nutzer mit den Stratix-FPGAs in direkten Kontakt kommen dürften, so sind sie aus technischer Sicht immer wieder interessant, da Intel hier auch neue Fertigungstechniken und vor allem Packaging-Technologien ausprobiert bzw. einführt. Mit dem Stratix 10 GX 10M zeigte Intel erstmals die Möglichkeiten von EMIB im Zusammenspiel mit High-End-Compute-Chips. Der Stratix 10 GX 10M verfügt über 10,2 Millionen logische Einheiten und 43,4 Milliarden Transistoren.

Der Stratix 10 TX zeichnet sich wie gesagt durch seine schnellen Netzwerkanbindungen aus, denn fünf der sechs Chiplets können 58G-Tranceiver sein. Der HyperFlex-Chip als zentrales Element wird bei Intel in 14 nm gefertigt, die Transceiver laufen in 16 nm bei TSMC vom Band. Einmal mehr als also zeigen sich hier die Möglichkeiten von EMIB.