Werbung

Graphcore hat die zweite Generation seiner Intelligence Processing Unit (IPU) vorgestellt. Die Colossus Mk2 GC200 IPU ist ein hochspezialisierter Chip, der auf das Training und Inferencing von Deep-Learning-Netzwerken ausgelegt ist. Bei einem Blick auf die technischen Daten wird schnell klar, dass es das britische Unternehmen Graphcore ernst meint.

Der Prozessor, also die Colossus Mk2 GC200 IPU, wird in 7 nm bei TSMC gefertigt. Hier zum Einsatz kommen 59,4 Milliarden Transistoren auf einer Fläche von 823 mm². Zum Vergleich: NVIDIAs Flaggschiff-GPU, die GA100 auf Basis der Ampere-Architektur, kommt auf rund 54 Milliarden Transistoren bei einer Fläche von 826 mm². Hier findet ebenfalls die Fertigung bei TSMC in 7 nm statt. In beiden Fällen bewegt man sich am Limit dessen, was aufgrund der Limitierungen von Masken- und Framegröße aktuell gefertigt werden kann. Laut Graphcore handelt es sich beim GC200 um den komplexesten Prozessor, der jemals gefertigt wurde. Leider nennt man keine TDP des Chips.

Der Prozessor besteht aus 1.472 sogenannten IPU-Cores, die wiederum 8.832 separate Compute-Threads verarbeiten können. Man könnte hier also in gewisser Weise von einem SMT6 (Simultaneous multithreading mit sechs Threads pro Kern) sprechen. Die Recheneinheiten der GC200-IPU sind auf die Berechnungen eines eigenen Datenformats optimiert. Graphcore nennt dies AI-Float und es wird versucht, alle Berechnungen nicht größer als 16 Bit werden zu lassen, um möglichst effektiv zu arbeiten. Die Recheneinheiten unterstützen außerdem FP32, FP16.32 (16 Bit Multiply mit 32 Bit Accumulate) und FP16.16 (16 Bit Multiply und Accumulate). Wie die Recheneinheiten der GA100-GPU von NVIDIA unterstützen die IPU-Cores Sparsity/Sparse Matrix oder die dünnbesetzte/schwachbesetzte Matrizen. Besteht eine Matrix aus sehr vielen mit Nullen besetzten Einträgen, können über verschiedene Techniken diese Bereiche in der Berechnung und Speicherung effizienter genutzt werden.

Möglichst großer und möglichst schneller Speicher spielt für das Training und Inferencing eine wichtige Rolle. Nicht ohne Grund ist der L2-Cache der GA100-GPU inzwischen 40 MB groß und AI-Beschleuniger wie die GC200-IPU setzen auf viel SRAM. Satte 900 MB sogenannter In-Processor Memory sind hier vorhanden. Der SRAM verteilt sich über die IPU-Cores, die in IPU-Tile organisiert sind.

Zudem kann jeder GC200-IPU bis zu 450 GB an Exchange-Memory zur Verfügung gestellt werden, der eine Bandbreite von 180 TB/s erreicht. Hier zeigt sich einmal mehr, dass großer und schneller Speicher ein wichtiger Bestandteil ist und hier reden wir noch von Speicher, der sich direkt auf dem Chip bzw. in direkter Nähe befindet. Diese Maßgabe des schnellen Speichers setzt sich aber auch auf die höhere Ebenen des Speicher-Subsystems, sprich DDR4- und NVMe-Speicher, fort.

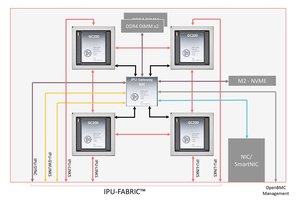

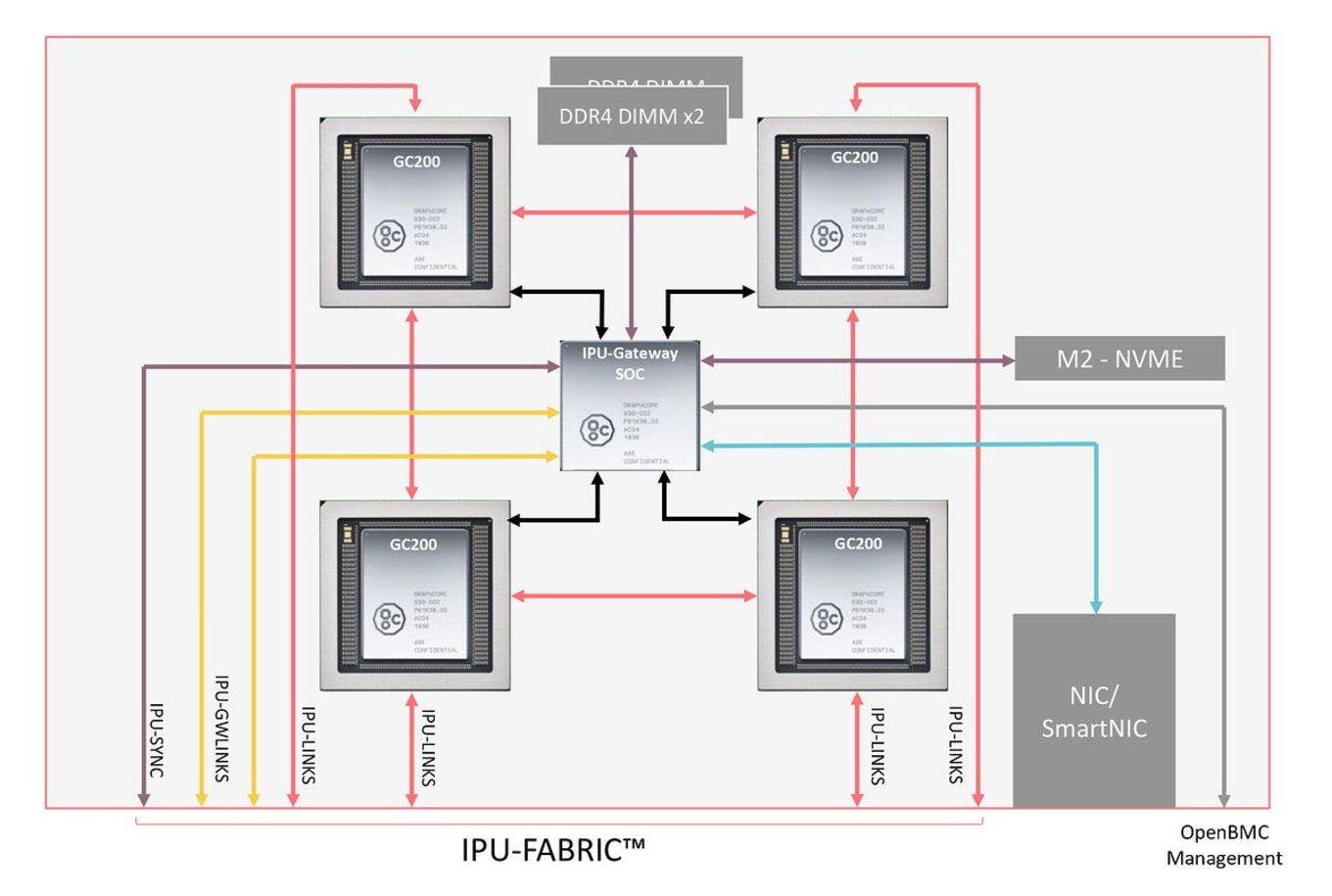

Ein schneller Interconnect spielt ebenfalls eine Rolle, denn eine GC200-IPU kommt selten zum Einsatz. Stattdessen gibt es Knoten mit bis zu vier dieser Chips. Diese wiederum sind über einen IPU-Fabric miteinander verbunden. Ein Graphcore GC4000 IPU-Gateway ist ein separater Chip, der hier zum Einsatz kommt und das Routing innerhalb eines Knotens übernimmt. Der GC4000 IPU-Gateway kommt auf eine kombinierte Datenrate von 2,8 TBit/s. Im Nahbereich kommen für den IPU-Fabric optische OSFP-Verbindungen zum Einsatz. Über größere Abstände hinweg dann QSFP-Verbindungen, die über Ethernet getunnelt werden.

Über den IPU-Fabric wird es möglich, ein Dutzend GC200-IPUs miteinander zu betreiben, das System soll aber auch mit zehntausenden IPUs noch skalieren.

IPU-Machine M2000

Als Basis eines Systems mit den neuen IPUs dient ein M2000 getaufter Knoten mit vier GC200-IPUs. 16 IPU-Maschines mit jeweils vier GC200-Chips können in ein Rack gepackt werden und nennen sich dann IPU-POD64. In größeren IPU-PODs können bis zu 64.000 GC200-IPUs zusammengefasst werden. Graphcore spricht hier von einer Rechenleistung von bis zu 16 EFLOPS.

Die IPU-Maschines arbeiten komplett eigenständig von bestehenden Systemen und können als solche betrieben werden. Einzig zur Speicherung und dem Lesen der Daten der AI-Anwendungen sind noch Standard-Systeme notwendig.

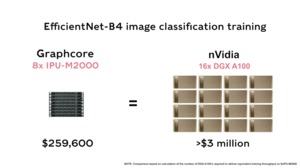

Graphcore liefert zudem ein paar Vergleichswerte zu bestehenden Systemen. Dabei nimmt man eine DGX-A100 mit acht der neuen A100-Beschleuniger von NVIDIA. Ein IPU-POD32, also 8x M2000-Racks mit jeweils vier GC200-IPUs, kommen auf eine FP32-Rechenleistung von 2.000 TFLOPS, während es beim DGX-A100 156 TFLOPS sind. Für das AI-Computing, also Berechnungen mit geringer Genauigkeit (zum Beispiel INT8), spricht Graphcore von 8 PFLOPS, während das DGX-A100-System auf 2,5 PFLOPS kommt. Der Anschaffungspreis des Graphcore-Systems soll bei 259.600 US-Dollar liegen, während ein DGX-A100 199.000 US-Dollar kostet, aber in bestimmten Bereichen deutlich weniger leisten kann – so der Hersteller.

IPU-Machine M2000 und IPU-POD64-Systeme können ab sofort vorbestellt werden und sollen ab dem vierten Quartal 2020 ausgeliefert werden. Per Cloud-Zugriff können Kunden ab sofort die neue Hardware nutzen und die eigenen Anwendungsbereiche darauf testen. Der OEM-Markt soll in den kommenden Monaten ebenfalls in Angriff genommen werden, so dass solche Systeme bald auch von Dell EMC oder HPE geliefert werden könnten.