Werbung

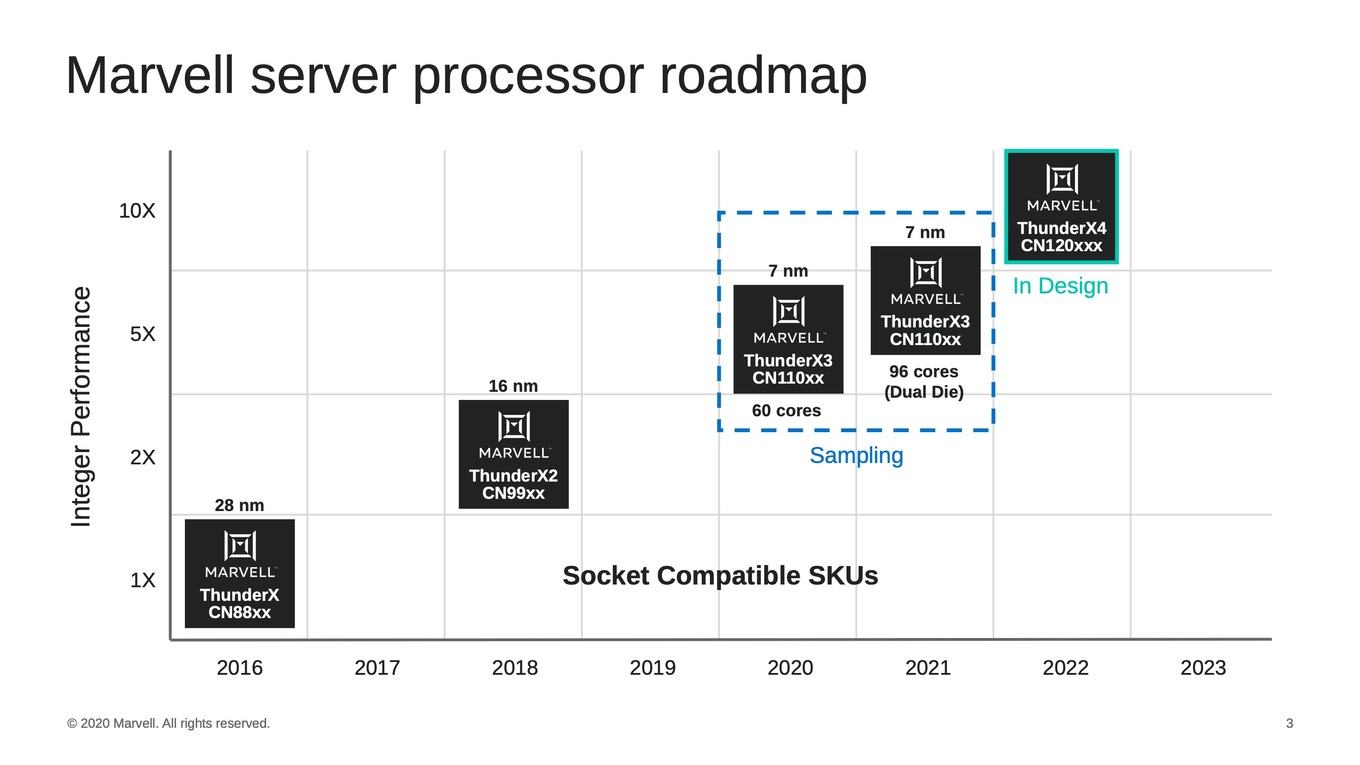

Bereits im Rahmen einer eigenen Vorstellung gab uns Marvell im Frühjahr einen Ausblick auf das, was uns mit dem ThunderX3 erwarten würde. Bekannt war bisher, dass Marvell die Anzahl der Kerne auf bis zu 96 anhebt. Außerdem sollte es acht Speichercontroller für DDR4-3200, 64 PCI-Express-4.0-Lanes im Single-Socket-Betrieb und 128 PCI-Express-4.0-Lanes im Dual-Socket-Betrieb geben.

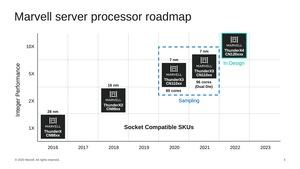

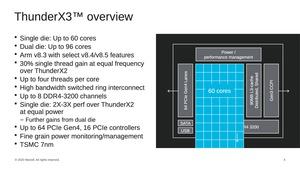

Auf der HotChips 32 hat man nun weitere Details verraten. So gibt es einen Single-Die- und einen Dual-Die-Chip. Beide werden in 7 nm gefertigt. Die Single-Die-Variante bietet bis zu 60 Kerne, als Dual-Die sind es bis zu 96 Kerne – eben wie im Frühjahr angekündet. Dies erinnert nun beispielsweise an die IBM POWER10-Prozessoren, die ebenfalls als Single- und Dual-Die verfügbar sein werden.

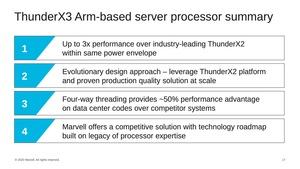

Die Kerne des ThunderX3 basieren auf dem ARM-v8.3-ISA und verwenden schon Funktionen von der Version 8.4 und 8.5. Es handelt sich jedoch nicht um das Neuverse-Referenzdesign von ARM, sondern eine Eigenentwicklung von Marvell. Der Hersteller spricht von einer um 30 % höheren Single-Threaded-Leistung bei gleichem Takt gegenüber den ThunderX2-Kernen.

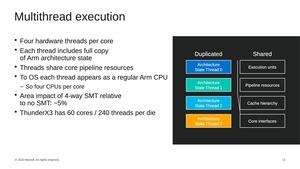

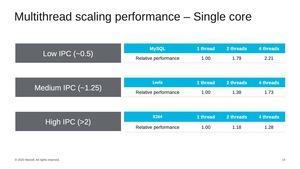

Es bleibt bei der Unterstützung von SMT4, also der Möglichkeit vier Threads pro Kern zu bearbeiten. Ein SMT4 sorgt dafür, dass die Pipelines der einzelnen Kerne besser ausgelastet werden. Auf dem Desktop kennen wir ein Simultaneous Multithreading oder kurz SMT mit zwei Threads pro Kern (SMT2), bzw. die bei Intel als Hyperthreading bezeichnete Funktion. Ein SMT4 ist eher unüblich, selbst im Serversegment. IBMs POWER10-Prozessoren unterstützen beispielsweise ein SMT8.

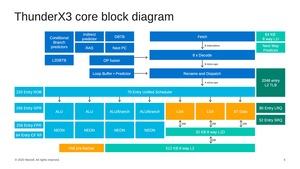

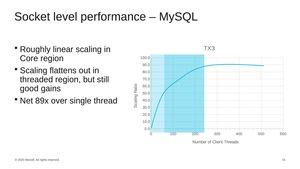

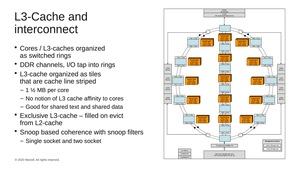

Auch aufgrund eines neuen Switched Ring Interconnects sollen die ThunderX3-Prozessoren besonders effizient und schnell sein. Unter anderem werden darüber die Speichercontroller für acht Kanäle an DDR4-3200 angesprochen. Die 64 PCI-Express-4.0-Lanes und der 90 MB große L3-Cache werden darüber ebenfalls angebunden. Neben der um 30 % höheren IPC-Leistung spricht Marvell von einer um den Faktor zwei bis drei höheren Leistung für den gesamten Sockel. Hier fließen dann natürlich auch die Mehrzahl an Kernen und der höhere Takt mit ein.

Kommt mehr als ein ThunderX3-Prozessor zum Einsatz, verwendet Marvell als Verbindung zwischen den Prozessoren den CCPI (Cavium Cache Coherent Interconnect).

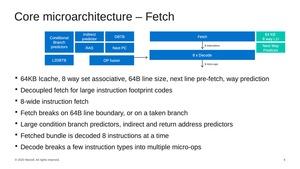

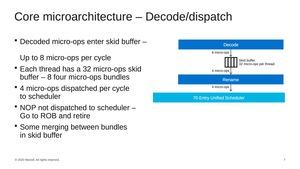

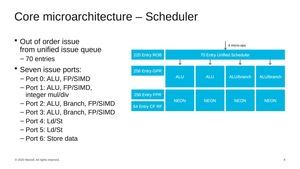

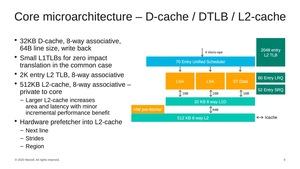

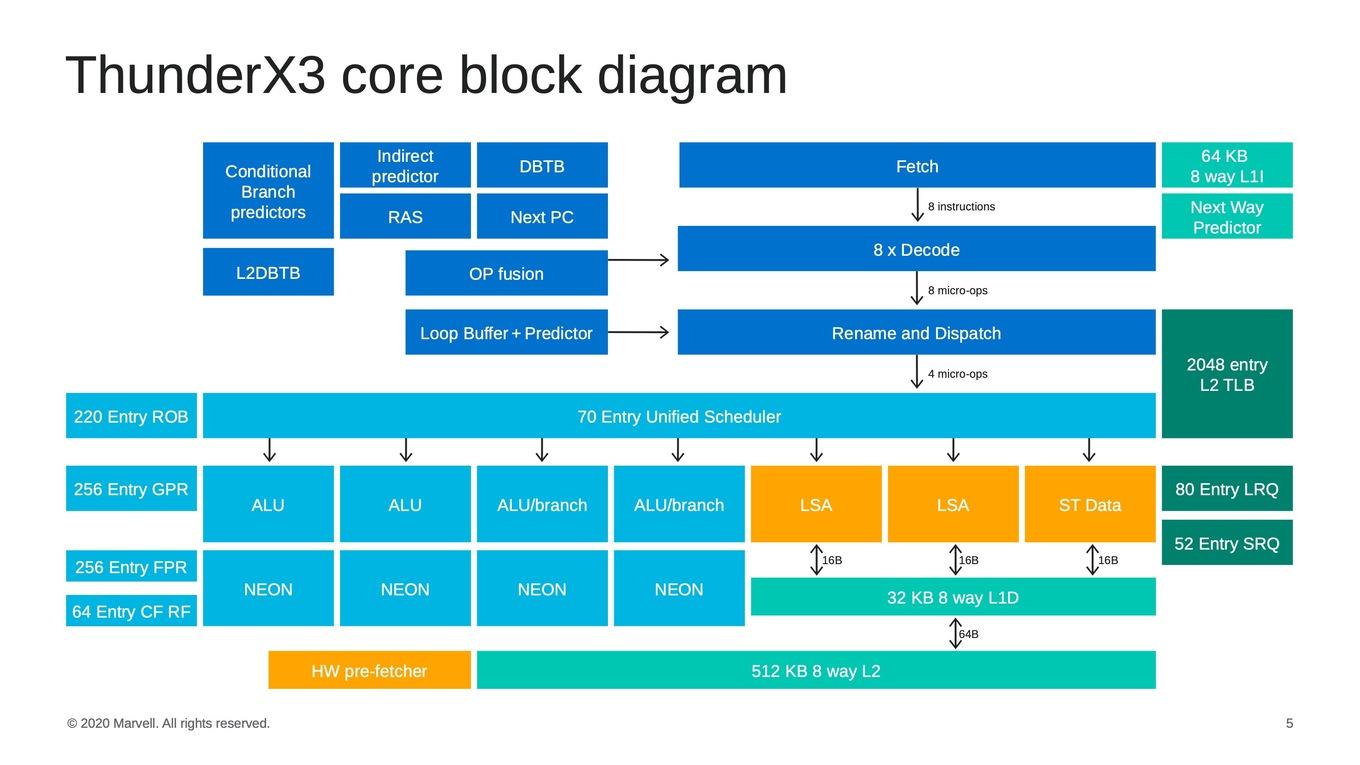

Jedem der Kerne in einem ThunderX3-Prozessor stehen 64 kB an L1-Instruction-Cache und 32 KB an L1-Data-Cache zur Verfügung. Hinzu kommen 512 kB an L2-Cache. Acht Decode-Einheiten verteilen die Aufgaben über einen 70 Einträge fassenden Scheduler auf die acht Recheneinheiten. Dies wären vier ALUs und vier NEON.

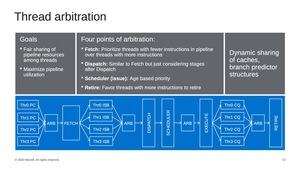

Optimierte Buffer, eine verbesserte Sprungvorhersage – all dies soll dazu beitragen, dass die Kerne oder Threads besser ausgelastet werden. Das SMT4 soll die Auslastung der Kerne verbessern. Der Overhead für ein SMT4 beträgt laut Marvell nur etwa 5 %. Dazu verwenden alle Threads eines Kerns teilweise exklusive Ressourcen und teilweise solche, die man sich mit anderen teilt.

Je nach Anwendung kann ein SMT, egal in welcher Form, aber durchaus Sinn machen. Für solche, wie kein Leistungsgewinn zu erwarten ist, kann das SMT einfach deaktiviert werden.

Der ThunderX3 soll gegen Ende 2020 in die Single-Die-Variante auf den Markt kommen. 2021 folg die Dual-Die-Version. In zwei Jahren, also 2022, soll dann schon der Nachfolger bereitstehen. Dieser befindet sich aktuell in der Design-Phase.