Werbung

Der erst 2019 ins Leben gerufene, offene Interconnect-Standard Compute Express Link oder kurz CXL wurde nun um die ersten Daten zur Spezifikation 2.0 erweitert. Auch wenn CXL mit Intel, NVIDIA, AMD, ARM und vielem mehr bereits große Namen in seinem Konsortium zusammenführen kann, so gibt es bislang erst wenig bis keine Hardware, die CXL konkret umsetzt.

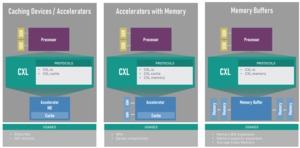

Dies wird sich allerdings 2021 mit der Einführung der ersten PCI-Express-5.0-Hardware ändern, denn CXL verwendet PCIe als physikalische Übertragungstechnik und wird mit PCIe 5.0 erst die Übertragungsgeschwindigkeiten und sonstige Voraussetzungen erreichen, um als Interconnect funktionsfähig zu sein. CXL wurde von Intels ins Leben gerufen und beinhaltet drei Protokolle, die die verschiedenen Nutzungsprofile für einen solchen Interconnect darstellen: CXL.io, CXL.cache und CXL.memory.

Mit CXL 2.0 wird der Funktionsumfang noch einmal deutlich erweitert und an das angepasst, das die teilnehmenden Unternehmen für die kommenden Jahre für wichtig erachten.

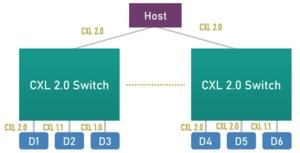

Eine dieser Funktionen ist das Switching, welches es ermöglicht, dass die oftmals nur beschränkte Anbindung des Hosts keinerlei Einfluss auf die Verbindung einzelner per CXL verbundener Geräte hat. Stellen wir uns eine PCIe-5.0-Verbindung mit 16 Lanes vor, an die vier Clients angebunden werden sollen. Jedem Client stünden hier nur jeweils vier Lanes zur Verfügung. CXL-Switches stellen in diesem Beispiel jedoch allen Clients die vollen 16 Lanes zur Verfügung und der Host ist an diesen Switch ebenfalls mit 16 Lanes angebunden. Der Flaschenhals in der Host-Switch-Anbindung ist aber häufig gar nicht so problematisch, da es wichtiger ist, dass die einzelnen Geräte untereinander mit der vollen Bandbreite arbeiten können.

Zudem ist es hier möglich, dass verschiedene CXL-Standards (1.0, 1.1, 2.0) zusammenarbeiten und dennoch der CXL-2.0-Hardware der volle Funktionsumfang zur Verfügung steht, auch wenn andere Hardware nur CXL 1.0 oder 1.1 unterstützt. Für einen CXL-Switch ist es zudem möglich, dass es mehrere Hosts gibts (Root Ports).

CXL 2.0 unterstützt Persistent Memory

Eine weitere Neuerung ist die Unterstützung für Persistent Memory (PMEM). Als Optane DC Persistent Memory hat Intel als größter Anbieter bereits eine, bzw. mehrere Produkte am Markt, die als Zwischenlösung von DRAM und NAND dienen. Bisher wird dieser Speicher aber direkt an das Speicherinterface des Prozessors angebunden.

CXL.memory wird also um die Unterstützung von PMEM erweitert und bietet damit die Möglichkeit, einen solchen Speicher Systemweit zu verwenden und nicht nur als Erweiterung des Arbeitsspeichers.

Dritter wichtigster Punkt unter den Neuerungen von CXL 2.0 ist die Sicherheit. Die Kommunikation innerhalb der Switches und auf den CXL.io-, CXL.cache- und CXL.memory-Schichten verläuft komplett verschlüsselt. Die Verschlüsselung hat allerdings einen Einfluss auf die Latenzen auf dem Interconnect.

Mit Sapphire Rapids wird Intel die übernächste Xeon-Generation mit CXL 1.1 ausstatten. Darüber hinaus fehlt es an konkreten Ankündigungen. Bis wir also erste Produkte sehen, die CXL in der Praxis einsetzen, werden noch etwa zwölf Monate vergehen.