Werbung

Im Rahmen der Supercomputing 2020 stellte AMD bereits gestern die Instinct MI100 mit CDNA-Architektur und NVIDIA die A100 GPU mit 80 GB HBM2e vor. Heute nun trug Intel seinen Beitrag der Konferenz bei und sprach über die eigenen Ambitionen im HPC- und Supercomputing-Umfeld.

Eigentlich wollte man die Xeons auf Basis von Ice Lake bereits 2017 auf den Markt werfen. Diese Pläne sind allerdings schon längt überholt und wurden mehrfach geändert. Als dritte Xeon-Scalable-Generation sollten sie dann noch in diesem Jahr erscheinen, aber auch diesen Zeitplan musste man kürzlich aufgeben. Auch wenn man bereits einige Samples an Partner ausliefert, von einer generellen Verfügbarkeit kann jedoch keine Rede sein.

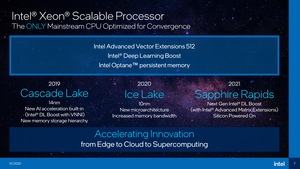

Auch wenn noch keine Produktvorstellung zu den Ice-Lake-Xeons erfolgt ist, so konkretisiert Intel einige Details. Über die aktuelle Xeon-Generation (Cascade Lake) sowie die beiden zukünftigen (Ice Lake und Sapphire Rapids) hinweg wird Intel die Unterstützung der Advanced Vector Extensions 512, Deep Learning Boost und für den Optane DC Persistent Memory bieten.

Für Sapphire Rapids spricht Intel von der Verwendung der verbesserten 10nm-SuperFin-Fertigung. Die Ice-Lake-Xeons werden ebenfalls in 10 nm gefertigt, basieren jedoch auf den Sunny-Cove-Kernen, während Sapphire Rapids bereits einige Architektur-Generationen weiter sein wird.

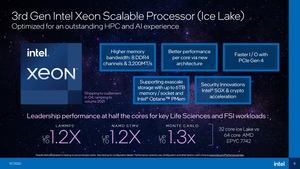

Erstmals nennt Intel außerdem eigene Leistungsdaten zu den Ice-Lake-Xeons. So soll ein Modell mit 32 Kernen in drei ausgewählten Anwendungen um 20 bis 30 % schneller sein, als ein AMD EPYC 7742 mit 64 Kernen. Die neuen Xeons dürften eine höhere IPC-Leistung für sich verbuchen können und höher takten, als die EPYC-Modelle, was ihnen in bestimmten Szenarien hilft. In der Multi-GPU-Leistung werden 32 Ice-Lake-Kerne jedoch kaum mit 64 Zen-2-Kernen mithalten können. Hier kommt es also einmal mehr darauf an, welche Anwendungen man betrachtet. Hinzu kommt die Verwendung optimierter Compiler, die je nach Plattform einen großen Einfluss auf die Leistung haben.

Vor allem beim Speicherinterface legt Intel nach und stattet die Ice-Lake-Xeons mit acht Speicherkanälen aus, die DDR4-3200 aufnehmen können. Endlich wird Intel eine Plattform anbieten können, die PCI-Express 4.0 unterstützt.

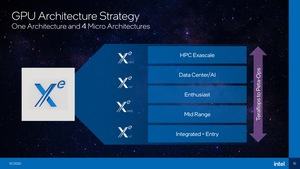

Xe-HP als Entwicklerkit für Ponte Vecchio

Zur Xe-Strategie äußerte sich Intel bereits in der vergangenen Woche. Die Xe-LP-Architektur liefert man als integrierte Grafikeinheit der Tiger-Lake-Prozessoren und die dedizierte Iris-Xe-Max-GPU bereits aus. Diese kommt ebenfalls für die Server-GPU H3C XG310 zum Einsatz. Darüber positioniert Intel die Xe-HPG- und Xe-HP-Architektur, die für Spieler und Datacenter-Anwendungen gedacht sind.

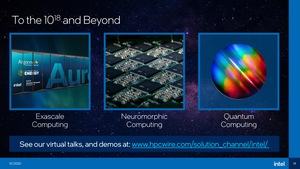

An Ponte Vecchio auf Basis der Xe-HPC-Architektur arbeitet man noch, hat jedoch bereits die erste Revision aller Chiplets für Ponte Vecchio aus der Fertigung erhalten. In Vorbereitung auf Ponte Vecchio arbeiten Intel und das Argonne National Laboratory aktuell mit GPUs auf Basis der Xe-HP-Architektur und nutzen diese als Development?Vehicle für Xe-HPC. Noch 2021 soll daraus eines der ersten Exascale-Systeme mit Sapphire-Rapids-CPUs und eben den Xe-HPC-GPUs werden.