Werbung

In der Berichterstattung und der äußeren Wahrnehmung konzentriert sich vieles im IT-Umfeld auf Prozessoren, GPU-Beschleuniger und allenfalls noch einige Speziallösungen im AI-Bereich. Häufig sprechen wir dabei von zentralen Lösungen (nicht in Form großer Rechenzentren oder Supercomputern), in denen enorme Datenmengen verarbeitet werden. Ein anderes Feld der Anwendungen wird durch Intel in Form der FPGAs beackert. Auf dem Intel FPGA Technology Day 2021 wurden einige Ankündigungen gemacht, die wir einmal beleuchten wollen.

Doch diese hohen Datenmengen, die jeder Nutzer selbst produziert oder die durch eine Interaktion mit dem Umfeld erstellt werden, machen das Edge-Computing immer wichtiger. Die Berechnungen und damit die Filterung der Daten wird beim Edge-Computing dort vorgenommen, wo sie entstehen. Bereits heute werden so pro Jahr weltweit über 50 Zettabyte an Daten produziert. Dies entspricht einer Datenmenge, die auf fünf Milliarden HDDs mit jeweils 10 TB abgespeichert werden müsste. 2025 sollen es laut Intel 175 Zettabyte sein.

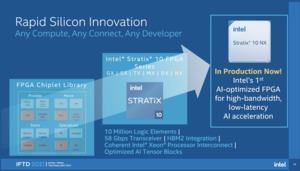

Um diese Daten nutzbar verarbeiten zu können, bedarf es spezieller Hardware. NVIDIA stellte beispielsweise den HGX-Beschleuniger vor, bei dem die A100-GPU direkt mit Mellanox ConnectX-6 Lx SmartNICs verknüpft wird. Hohe Rechenleistung gepaart mit schneller Netzwerkanbindung also. Intel bietet mit den Stratix-FPGAs ähnliche Lösungen.

Das Chiplet-Design der FPGAs von Intel kann auf die notwendigen Anforderungen angepasst werden. Ein Compute-Tile wird mit einem DDR-Speichercontroller und schnellem HBM-Speicher zusammengebracht. In R-, F-, P-, H- und E-Tiles können beispielsweise PCI-Express-Controller verschiedener Generationen oder Ausbaustufen von Ethernet-Controllern untergebracht werden. Details dazu findet man in der Ankündigung zum Stratix 10 NX FPGA. Für eben diese kündigt Intel zum FPGA Technology Day 2021 an, dass man mit der Massenproduktion begonnen hat.

Das Chiplet-Design der FPGAs bietet aber nicht nur eine Flexibilität im eigentlichen Design, sondern auch in der Fertigung. So können die einzelnen Tiles in dem Fertigungsprozess hergestellt werden, in dies gerade möglich oder wirtschaftlich sinnvoll ist. Per EMIB und Foveros werden die Chiplets dann auf einem Package untergebracht.

Die nächste FPGA-Generation wird das Chiplet-Design fortführen. Aus aktuell sechs Serien (GX, SX, TX, MX, DX und NX) wird Intel dann drei Serie machen (F-, I- und M-Series). Diese ursprünglich mal für 2019 geplanten FPGAs sollen in den kommenden Monaten verfügbar sein und verwenden eine speziell für FPGAs angepasste Fertigung in 10nm SuperFin. Die 10nm SuperFin Technologie stellt Intels Rettungsanker für die problembehaftete Fertigung in 10 nm dar und kommt unter anderem für die Tiger-Lake-Prozessoren zum Einsatz. Für die Agilex-FPGAs plant Intel mit DDR5 und PCI-Express 5.0 sowie dem CXL-Interconnect – die allesamt als Chiplet-Zusatz möglich sein werden.

Diese eher schwergewichtigen FPGAs kombiniert Intel mit den Max- und Cyclone-Serien, die kosteneffektiver sind, die aber auch noch dichter am Endpunkt der Entstehung der Daten eingesetzt werden können.

Als komplett neue Serie wird zudem der Direct RF FPGA vorgestellt. Dieser ist explizit für eine schnelle Analyse von Radio-Frequenzdaten ausgelegt und soll fünfmal schneller sein, als alles andere bisher am Markt verfügbare. 64 Gigasamples pro Sekunde soll der Chip erfassen können. Diese Leistungsdaten basieren allerdings auf Hochrechnungen seitens Intel, denn wirklich testen konnte man den Direct RF FPGA noch nicht. Eingesetzt werden soll der Direct RF FPGA im Umfeld von RF- und Wireless-Test-Equipment, aber auch dem Militär. Ab wann die neue FPGA-Serie ausgeliefert wird, gibt Intel nicht an.

Intels FPGAs können über einen kohärenten Interconnect mit Xeon-Prozessoren zusammenarbeiten. Aber auch an anderer Stelle bringt Intel eigene Produkte mit den FPGAs zusammen. So ist es möglich, diese mit Optane DC Persistent Memory (anstatt DDR-Speicher) auszustatten.