Werbung

In Asien (Bilibili) sind Bilder eines Engineering Samples der übernächsten Xeon-Generation alias Sapphire Rapids aufgetaucht. Diese soll auf Ice Lake-SP folgen, die im Frühjahr erwartete Xeon-Generation. Mit Sapphire Rapids wird Intel einen größeren Plattform- und Ökosystemwechsel vollziehen. So wird Sapphire Rapids PCI-Express 5.0, DDR5 und auf Basis dessen Compute Express Link unterstützen. Außerdem war schon mehrfach die Rede von HBM-Speicher, der sich auf dem Package befinden soll.

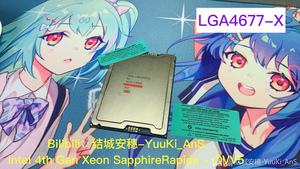

Den Sockel LGA 4677 haben wir bereits mehrfach gesehen, ebenso das riesige Package. Auf den Bildern zu sehen ist ein Engineering Sample – genauer gesagt ein Qualification Sample. Diese vergibt Intel an seine Partner, damit diese ihre Mainboards oder gesamtem Serverplattformen testen können. Der angegebene Takt auf dem Package beträgt vergleichsweise niedrige 1,3 GHz. Dies ist für Engineering Samples von Intel allerdings nicht unüblich.

Aktuell gibt es noch nicht allzu viele Informationen zu Sapphire Rapids. Gefertigt werden sollen die Prozessoren in 10 nm (vermutlich Enhanced 10nm SuperFin). Die CPU-Kerne sollen auf Willow Cove basieren. Diese Architektur kommt auch bei den aktuellen Tiger-Lake-Prozessoren zum Einsatz. Ice Lake-SP hingegen wird zunächst Sunny-Cove-Kerne verwenden und ebenfalls in 10 nm gefertigt.

Die Quelle der Bilder hat offenbar den Heatspreader entfernt, so dass wir einen Blick auf die eigentlichen Chips werfen können. Zu sehen gibt es ein Chiplet-Design mit vier Dies, die eng gepackt im 2x2-Layout auf dem Package sitzen. Einen HBM gibt es in dieser Version von Sapphire Rapids offenbar nicht. Es ist aber durchaus denkbar, dass Intel verschiedene Varianten und eben auch solche mit HBM on Package auf den Markt bringen wird. Dafür sehen wir einen On-Package FPGA, was allerdings auch keine Neuerung ist, denn Intel hat solche FPGAs für spezielle Xeon-Modelle bereits häufiger verwendet.

Die Xeon-Prozessoren auf Basis von Sapphire Rapids sollen bereits Ende 2021 vorgestellt werden. Dies bedeutet aber auch, dass Ice Lake-SP eine extrem geringe Lebensdauer haben wird.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Da die Größe des Sockels und damit die Größe des Package bekannt ist, kann die Größe der Chiplets abgeschätzt werden. Dieser Schätzung zufolge kommt das einzelne Chiplet auf eine Fläche von 418,8 mm². Ein aktueller Extreme Core Count Die (XCC) mit 28 Kernen kommt aktuell auf 694 mm².

Update:

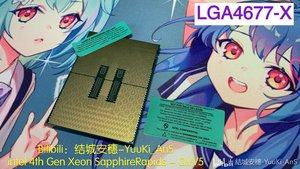

YuuKi-AnS hat nachgelegt und nicht nur den Heatspreader entfernt, sondern den Chip auch abgeschliffen und Die-Shots erstellt.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Leider liegen die Bilder in keiner hohen Qualität vor uns sind mit den Wasserzeichen auch etwas überladen. Zu sehen aber gibt es den kompletten Chip bestehend aus vier Chiplets, aber auch Detailaufnahmen eines einzigen Kerns. Neue Erkenntnisse ergeben sich daraus nicht. Allerdings wird einmal mehr bestätigt, dass jedes Compute Tile 15 Kerne besitzt, die aber wohl nicht allesamt aktiv sein werden.