Werbung

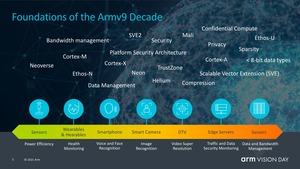

Auf dem ARM Vision Day 2021 hat der britische CPU-Entwickler mit Armv9 eine neue Erweiterung des AArch64 Instruction Sets vorgestellt. Diese ist natürlich vollständig zu Armv8 kompatibel, bietet im Bereich der Sicherheit, den Machine Learning und vor allem im Hinblick auf die Vektor-Erweiterungen einige fundamentale Verbesserungen, welche den aktuellen und zukünftigen Anforderungen gerecht werden sollen.

Die Scalable Vector Extensions oder kurz SVE wurden 2019 eingeführt. Die A64FX-Prozessoren von Fujitsu, die im aktuell schnellsten Supercomputer der Welt eingesetzt werden, nutzen diese ebenfalls und hier wurde die ARM-Architektur bereits um spezielle Hardwareeinheiten erweitert. Als Armv9 sind SVE und SVE2 nun jedoch Bestandteil der Befehlssätze und können von Entwicklern überall dort verwendet werden, wo Prozessoren die Armv9-ISA anwenden. Die Vektor-Größe kann von 128 bis 2.048 Bit gewählt werden. Die kleinste Einheit ist also ein Vektor mit einer Größe von 128 Bit.

Besitzt ein Prozessor nun Hardwareeinheiten, die Vektoren mit einer Größe von 128 Bit verarbeiten können, müssen Rechenaufgaben, die beispielsweise Vektoren mit einer Länge von 512 Bit beinhalten, in vier Einzelaufgaben aufgeteilt werden. Dies geschieht aber in der Laufzeit der Programme und muss nicht vom Entwickler beachtet werden. Auf der anderen Seiten können Hardware-Vektor-Einheiten, die 1.024 Bit verarbeiten können, gleich mehrere 128-Bit-Vektoren gleichzeitig verarbeiten. Dies alles geschieht allerdings ohne, dass der Entwickler des Codes darauf Einfluss nehmen muss.

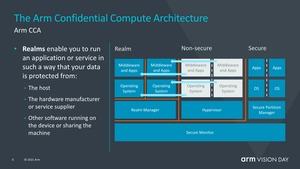

Mit der Confidential Compute Architecture (CCA) will ARM die Sicherheit seiner Architektur weiter verbessern. Die Sicherheit vieler Systeme ist darauf ausgelegt, dass Software der Integrität des Betriebssystems und Hypervisor vertraut. Ist einer dieser Komponenten allerdings kompromittiert, fällt damit die Sicherheit der darüberliegendenden Software-Schicht.

Mit der CCA führt ARM nun sogenannte Realms ein, die abgesicherte Bereiche darstellen. Realms sind abgesicherte Umgebungen, die für das Betriebssystem oder den Hypervisor völlig undurchsichtig sind. Der Hypervisor existiert zwar auch im Konzept der Realms, wäre jedoch ausschließlich für das Scheduling und die Ressourcenzuweisung zuständig. Verwaltet werden die Realms vom Realm Manager. Ein Vorteil dieses Systems soll die Reduzierung der Chain of Trust sein, was einerseits Auswirkungen auf die Leistung hat, auf der anderen Seite aber auch die Angriffsoberfläche reduziert.

Die ersten Designs auf Basis von Armv9 werden womöglich noch in diesem Jahr vorgestellt werden. Erste konkrete Produkte in Form erster Chips werden dann 2022 erwartet.

ARM bekräftigt seine Roadmap

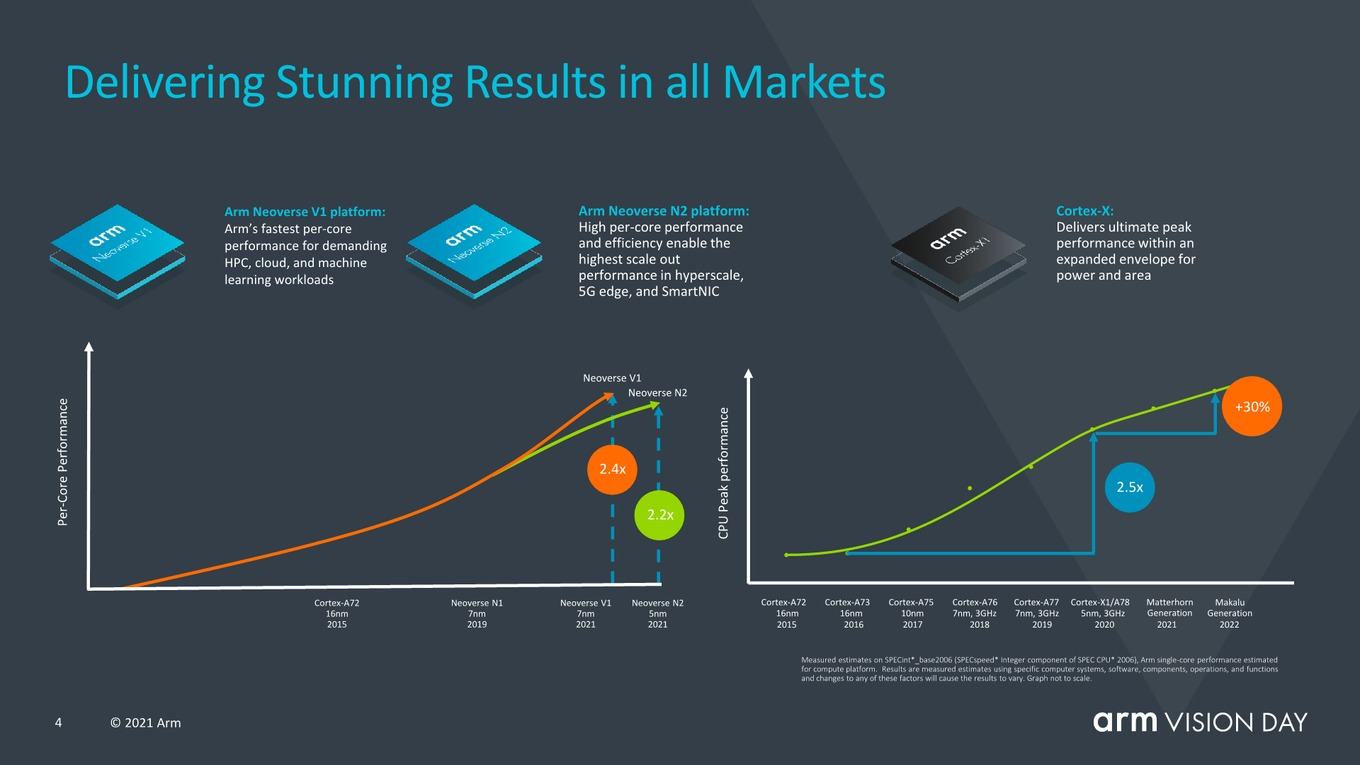

Schlussendlich bekräftigt ARM seine Datacenter- und Cortex-Roadmap. Noch in diesem Jahren sollen die ersten Chips auf Basis des Neoverse V1- und N2-Designs vorgestellt werden. Für die N2-Plattform waren bereits die Scalable Vector Extensions angekündigt worden, die pro Kern 2x 128 Bit weite Vektoreinheiten besitzen sollen. Die Single-Threaded-Leistung soll mit den nächsten Kernen um 40 bis 50 % gegenüber den aktuellen Kernen steigen. ARM verfolgt hier konsequent den Weg, solche Designs für den Serverbereich weiterzuentwickeln.

Über die beiden nächsten Cortex-Generationen sollen die Matterhorn- und Makalu-Designs um 30 % schneller werden. Hier spricht ARM von IPC-Leistung bei gleicher ISO-Frequenz. Davon profitieren werden vor allem die SoCs für Smartphones, die auf eben ein solches Cortex-Design setzen.