Werbung

Bereits im Herbst des vergangenen Jahres gab ARM erste Leistungsziele seiner nächsten beiden Datacenter-Designs Neoverse V1 und N2 vor. Die schon damals genannten +50, bzw. +40 % an Single-Threaded-Leistung bekräftigt man nun, nennt jedoch weitere Details.

Einmal mehr möchte ARM die Vorteile und den aktuellen Schwung bei den Serverprozessoren auf Basis seiner ARM-Architektur unterstreichen. So sieht man die aktuelle Entwicklung nur als Spitze eines Eisbergs. Mit Zahlen belegen will man dies über die Auslieferungen neuer Prozessoren an Amazon, die für ihren AWS-Dienst bereits auf ein Neoverse-Design (Graviton2) setzen. In 2020 sollen bereits 49 % aller neu angebotenen Instanzen auf Basis eines Graviton-Prozessors funktionieren. Zwischen Mitte 2020 und jetzt stieg der Anteil der Auslieferungen mit dem eigenen Prozessor stark an, wohingegen der Einsatz von Xeon- und EPYC-Prozessoren bei den Neuanschaffungen zurückgegangen ist.

ARM sieht das Momentum eindeutig auf seiner Seite. Auch NVIDIA kündigte mit Grace erst kürzlich einen Datacenter-Prozessor an, der ein zukünftiges Neoverse-Design verwenden soll.

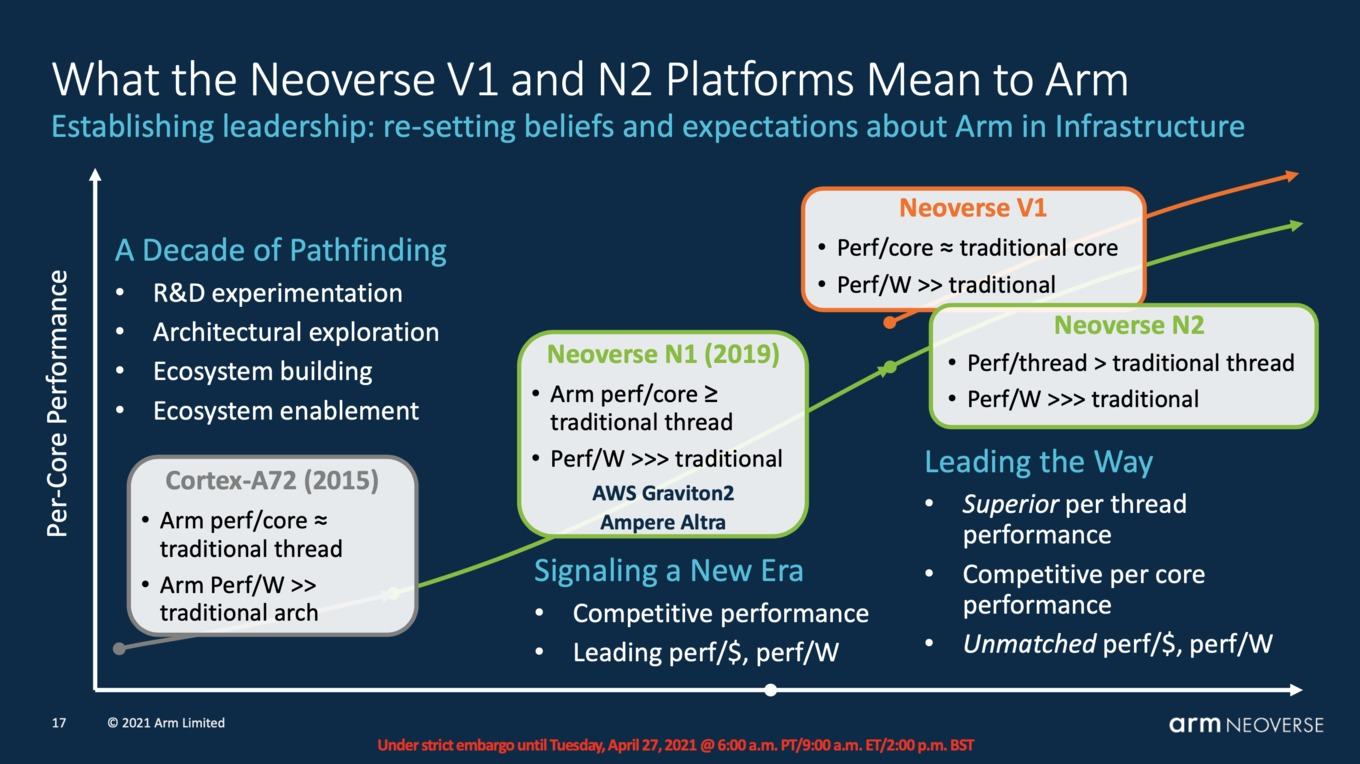

Mit dem nun neuen Nerverse-V1- und -N2-Design will ARM die zwei wichtigsten Anwendungsbereiche für solche Prozessoren abdecken. Neoverse V1 bietet dazu eine mit aktuellen Mikroarchitekturen ähnliche Leistung pro Kern, arbeitet jedoch mit einer wesentlich geringeren Leistungsaufnahme. Ausgelegt ist das Design für HPC-Anwendungen, wo es maßgeblich um die Leistung geht.

Das Neoverse-N2-Design hingegen soll breiter aufgestellt werden. Die Leistung pro Thread soll leicht über der Konkurrenten liegen, die Effizienz aber deutlich besser sein. Von sogenannten Edge-Anwendungen bis zur Cloud sieht ARM den Einsatz des N2-Designs.

Für die V1-Kerne, bzw. das Design gibt es bereits erste konkrete Ankündigungen. So hat SiPearl das Design für den europäischen HPC-Chip Rhea lizensiert. In Indien soll ein Exescale-System mit Neoverse-V1-Design aufgebaut werden und in Korea plant ETRI spezielle Beschleuniger mit Neoverse V1, HBM2E und DDR5.

Um ein Leistungsplus von 40 bis 50 % im Single-Threaded-Bereich zu erreichen, muss ARM die Kerne natürlich deutlich überarbeiten. Entsprach ein Kern des N1-Designs noch weitestgehend einem Cortex A76, sind die V1- und N2-Kerne komplett neu entwickelt worden.

| Neoverse N1 | Neoverse V1 | |

| Fetch | 4-Wide | 8-Wide |

| Decode | 4-Wide | 5-8 Wide |

| Dispatch/Issue | 8-Wide | 15-Wide |

| Back-End | 2x ALU 2X NEON | 2x SVE 4x NEON 4x ALU |

Das Front- und Back-End werden deutlich breiter aufgestellt. Die Fetch-Einheit wird verdoppelt, das Decoding breiter und flexibler. Ebenfalls verdoppelt wird die Breite der Dispatch- und Issue-Einheiten. All dies ist notwendig, um die eigentlichen Recheneinheiten füttern zu können. Für das Neoverse-N1-Design sah ARM zwei ALUs, eine Complex ALU für Multiplikationen und Divisionen und zwei 128 Bit breite SIMD-Pipelines (NEON) vor, die Vektor- und Fließkommaoperationen übernehmen konnten.

Beim Neoverse-V1-Design kommen gleich vier NEON-Einheiten zum Einsatz. Hinzu kommen ebenfalls vier ALUs und zwei Scalable Vector Extension (SVE) mit einer Breite von jeweils 256 Bit. Die Vektor-Größe für solche Berechnungen kann von 128 bis 2.048 Bit gewählt werden. Die kleinste Einheit ist also ein Vektor mit einer Größe von 128 Bit. Besitzt ein Prozessor nun Hardwareeinheiten, die Vektoren mit einer Größe von 256 Bit verarbeiten können, müssen Rechenaufgaben, die beispielsweise Vektoren mit einer Länge von 512 Bit beinhalten, in zwei Einzelaufgaben aufgeteilt werden. Dies geschieht in der Laufzeit der Programme und muss nicht vom Entwickler beachtet werden. Auf der anderen Seiten können Hardware-Vektor-Einheiten, die 1.024 Bit verarbeiten können, gleich mehrere 128-Bit-Vektoren gleichzeitig verarbeiten. Dies alles geschieht allerdings ohne, dass der Entwickler des Codes darauf Einfluss nehmen kann oder muss.

Das Front- und Back-End des Neoverse-V1-Designs werden also in allen Bereichen aufgebohrt, um eine höhere Rechenleistung zu ermöglichen.

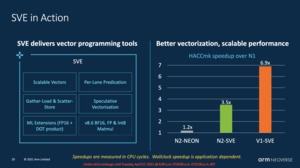

Für das V1-Design besonders im Fokus liegen die SVE-Einheiten. Die dazugehörigen Vektorerweiterungen werden immer wichtiger. Mit Armv9 stellte ARM erst kürzlich eine neue Erweiterung des AArch64 Instruction Sets vor, die SVE- und SVE2-Befehlssatzerweiterungen vorsieht. Neoverse N2 wird als erste Architektur auf Armv9 setzen, während das V1-Design die letzte Umsetzung von Armv8.4 sein wird. Die SVE-Einheiten werden über ein Custom-Design hinzugefügt, wie bei den A64FX-Prozessoren von Fujitsu, die im aktuell schnellsten Supercomputer der Welt eingesetzt werden.

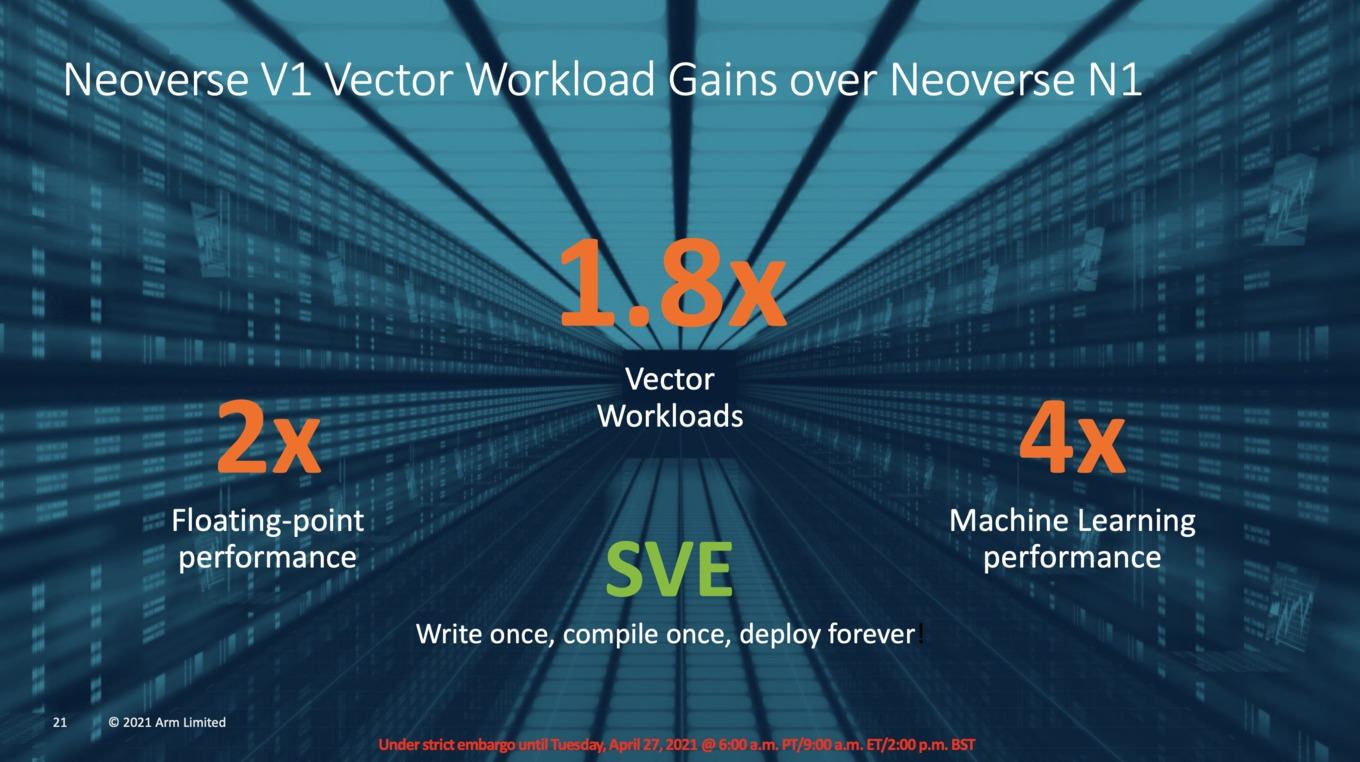

Zusammenfassend soll das Neoverse-V1-Design bei gleicher Anzahl an Kernen doppelt so schnell in der Fließkommaberechnung sein. Für Vektor-Berechnungen geht ARM von 1,8x aus und für ML-Anwendungen vom Faktor vier.

Neoverse N2 setzt den Fokus anders

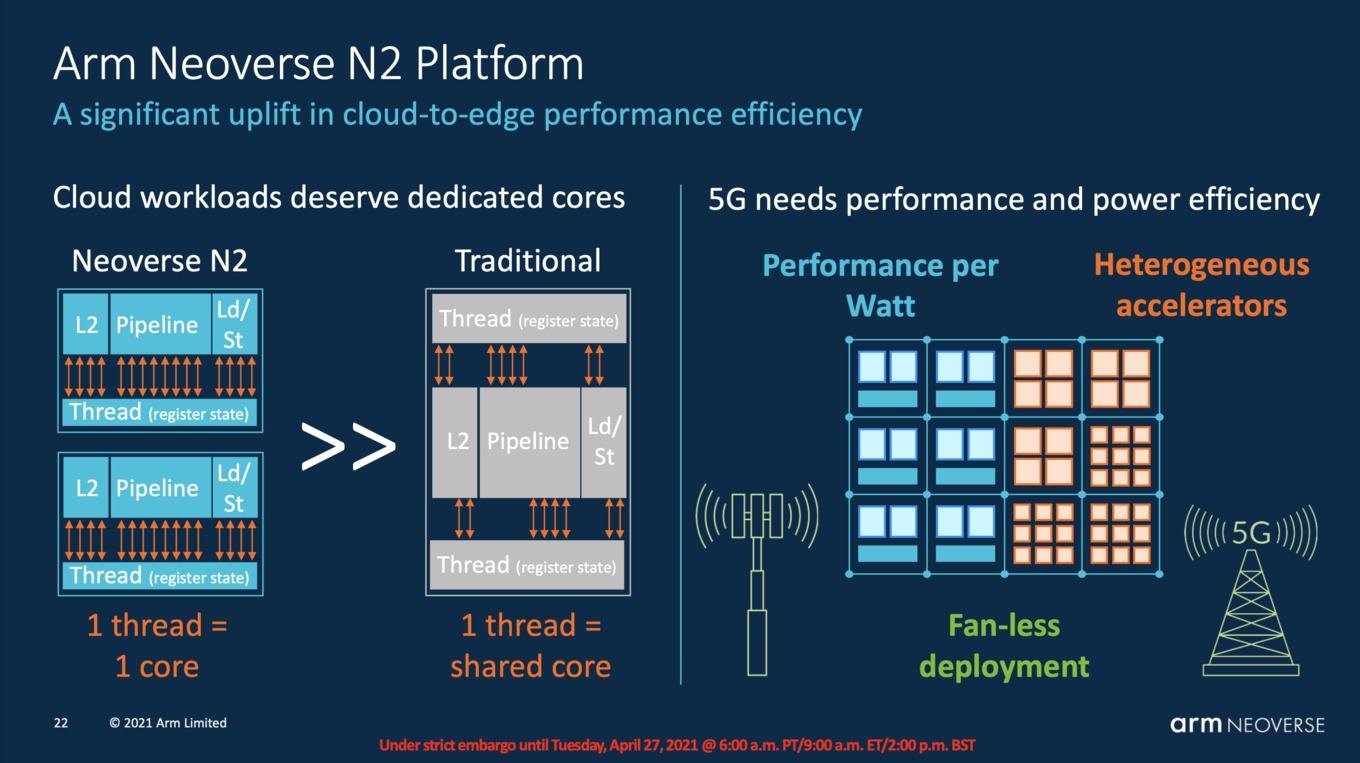

Während beim Neoverse-V1-Design klar die Leistung im Fokus steht, soll das Neoverse-N2-Design einen leicht anders ausgerichteten Markt bedienen. Die Leistung pro Watt ist hier aufgrund des Anwendungsprofil wichtig, denn die Prozessoren sollen nicht nur im Datacenter eingesetzt werden, sondern näher am eigentlichen Anwender, bzw. dort, wie die Rechenleistung zwar benötigt wird, es aber auch Einschränkungen hinsichtlich der Kühlung und Leistungsaufnahme gibt.

Genau wie für die V1-Kerne sieht ARM nur einen Thread pro Kern vor. Das Front- und Back-End müssen bei zwei oder mehr Threads pro Kern nicht aufgeteilt werden, so dass jedem Prozess alle Ressourcen zur Verfügung stehen.

Zudem wird das Neoverse-N2-Design das erste sein, welches auf SVE2 setzt. SVE2 ist ein Superset von SVE und NEON.

Durch die Nutzung der Armv9-Instruktionen sollen die Prozessoren im N2-Design flexibler, aber auch sicherer werden. Zudem verspricht ARM eine um 20 bis 40 % höhere Leistung im Vergleich zum N1-Design.

Einschätzung der Leistung auf Basis von Projektionen

Die bisher genannten Leistungsdaten sind genau wie die nun folgenden noch reine Projektion durch ARM. Zwar hat man in der Vergangenheit damit die reellen Werte oft sehr gut getroffen, es sollte allerdings nicht unerwähnt bleiben, dass ARM noch keine belastbaren Zahlen auf Basis echter Hardware präsentieren kann.

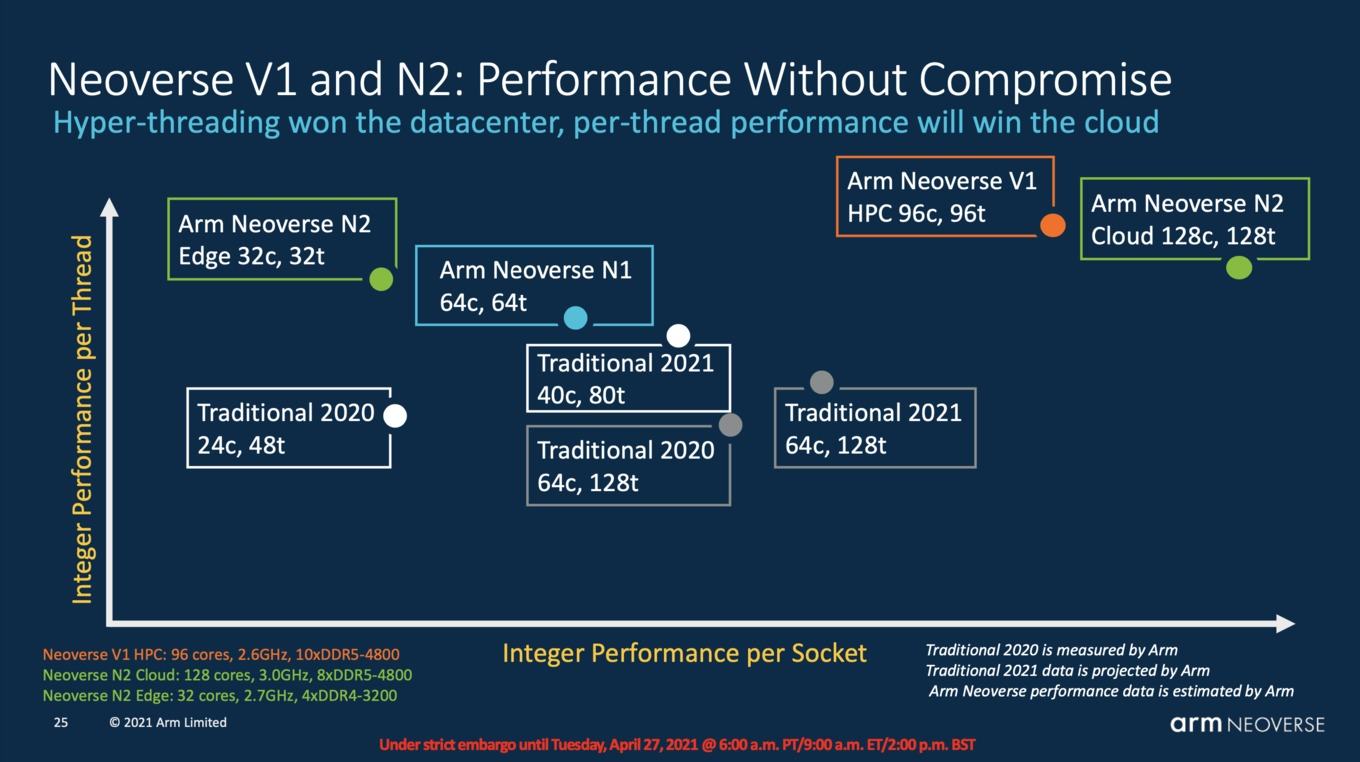

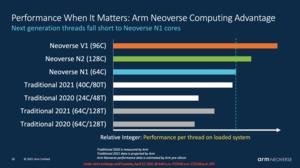

Als Basiswerte zieht ARM die eines Neoverse-N1-Designs mit 64 Kernen sowie die aktuellen und vorherigen Prozessoren von Intel (Ice Lake-SP) und AMD (EPYC 7003) heran. Für die Ausstattung mit den jeweils meisten Kernen geriet ARM mit Neoverse N1 so langsam ins Hintertreffen wenn es um den gesamten Sockel geht, kann aber laut eigener Aussage in der Leistung pro Thread weiterhin bestehen. Mit dem Neoverse-N2-Design soll der frühere Vorsprung wiederhergestellt werden – sowohl auf die Leistung pro Thread, wie auch auf die Leistung pro Sockel bezogen. Die Architektur spielt hier eine Rolle, aber auch das Ausbau mit bis zu 128 Kernen pro Prozessor. Im Edge-Segment sieht sich ARM mit dem Neoverse-N2-Design mit 32 Kernen klar der Konkurrenz überlegen.

Für das HPC-Segment zieht das Neoverse-V1-Design an allem vorbei, was aktuell am Markt verfügbar ist – so zumindest ARMs eigene Projektionen. Derzeit scheint man ein Design mit 96 Kernen als ausgewogen anzusehen. Wie wir noch sehen werden, sind aber auch deutlich mehr als 96 Kerne möglich – auch mehr als 128 als beim Neoverse-V1-Design. ARM bezieht hier Modellrechnungen ein, die von einer ähnlichen Leistungsaufnahme ausgehen.

Hinsichtlich der Taktraten legt ARM das Neoverse-N2-Design mit 2,7 GHz (Edge) und 3.0 GHz (Cloud) aus. das Neoverse-V1-Design wird mit 2,6 GHz angegeben. Ein Ampere Altra mit 80 auf Basis des Neoverse-N1-Designs kommt auf 3,3 GHz und wird in 7 nm gefertigt. Ein AWS Graviton2 mit 64 Kernen taktet mit 2,5 GHz.

Die oberen beiden Diagramme zeigen die Daten des XY-Diagramms noch einmal etwas anders aufbereitet.

Schnelle Kerne und aufgebohrte Plattform

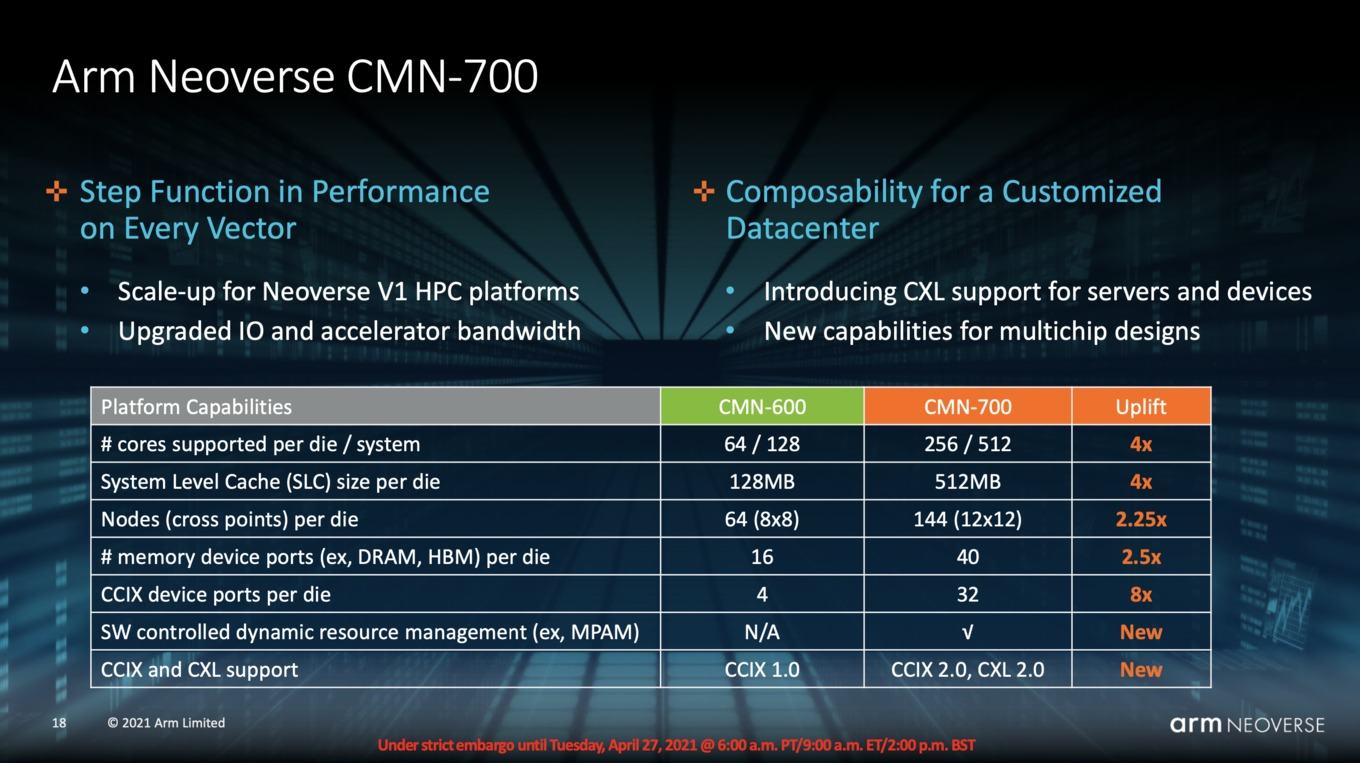

Zusammen mit dem Neoverse-V1- und N2-Design präsentierte ARM ein neues kohärentes Mesh-Netzwerk. Das Neoverse CMN-700 wird den Anforderungen angepasst.

Die maximale Anzahl an Kernen, die im CMN-700 verwaltet werden können, vervierfacht sich im Vergleich zum Vorgänger. Bisher hat ARM nur von Neoverse-V1- und N2-Designs mit 32, 96 oder 128 Kernen gesprochen. Theoretisch möglich sind jedoch 256 pro Sockel und 512 für ein 2S-System. Der dazugehörige System Level Cache (SLC) wird ebenfalls von 128 auf 512 MB um den Faktor vier vergrößert.

Neben der höheren Anzahl an Kernen kann das CMN-700 Mesh-Netzwerk 40 anstatt wie bisher nur 16 Speicherblöcke (wie DRAM-Interfaces oder HBM-PHYs) verwalten. Mit der Steigerung der Komplexität des Meshs steigt außerdem die Anzahl der Knoten, die verwendet werden können, um alle verbauten Komponenten schnellstmöglich über das Mesh zu verbinden.

Als Plattform ebenfalls relevant ist die Steigerung der CCIX-Ports für den gleichnamigen Interconnect. Bis zu 32 anstatt wie bisher nur vier Ports stehen zur Verfügung, die zur Anbindung weiterer Chips verwendet werden können. Schlussendlich soll das CMN-700 Mesh-Netzwerk CXL 2.0 unterstützen und darüber beispielsweise Beschleuniger-Karten oder sonstige Hardware anbinden.

Noch in diesem Jahr sollen die ersten Prozessoren auf Basis des Neoverse-V1-Designs vorgestellt werden. Die Fertigung wird in 7 oder 5 nm erfolgen – je nachdem was der Kunde beim Auftragsfertiger bestellt hat, bzw. ergattern konnte. Prozessoren mit Neoverse-N2-Designs werden etwas später erwartet und in jedem Fall in 5 nm gefertigt, bzw. sind schon darauf optimiert ausgelegt.