Werbung

Data Processing Units (DPUs) oder auch Infrastructure Processing Units (IPUs) sind aktuell in aller Munde. NVIDIA hat durch den Kauf von Mellanox die Entwicklung in Form der Bluefield-DPUs vorangetrieben und will in 2022 mit dem Bluefield-3 satte 16 ARM-Kerne, 400-GBit/s-Ethernet und ein 18 Millionen IOPs großen Blockstorage anbieten. Bis zu 300 x86-Kerne soll ein solcher Chip ersetzen und damit andere Ressourcen freimachen können.

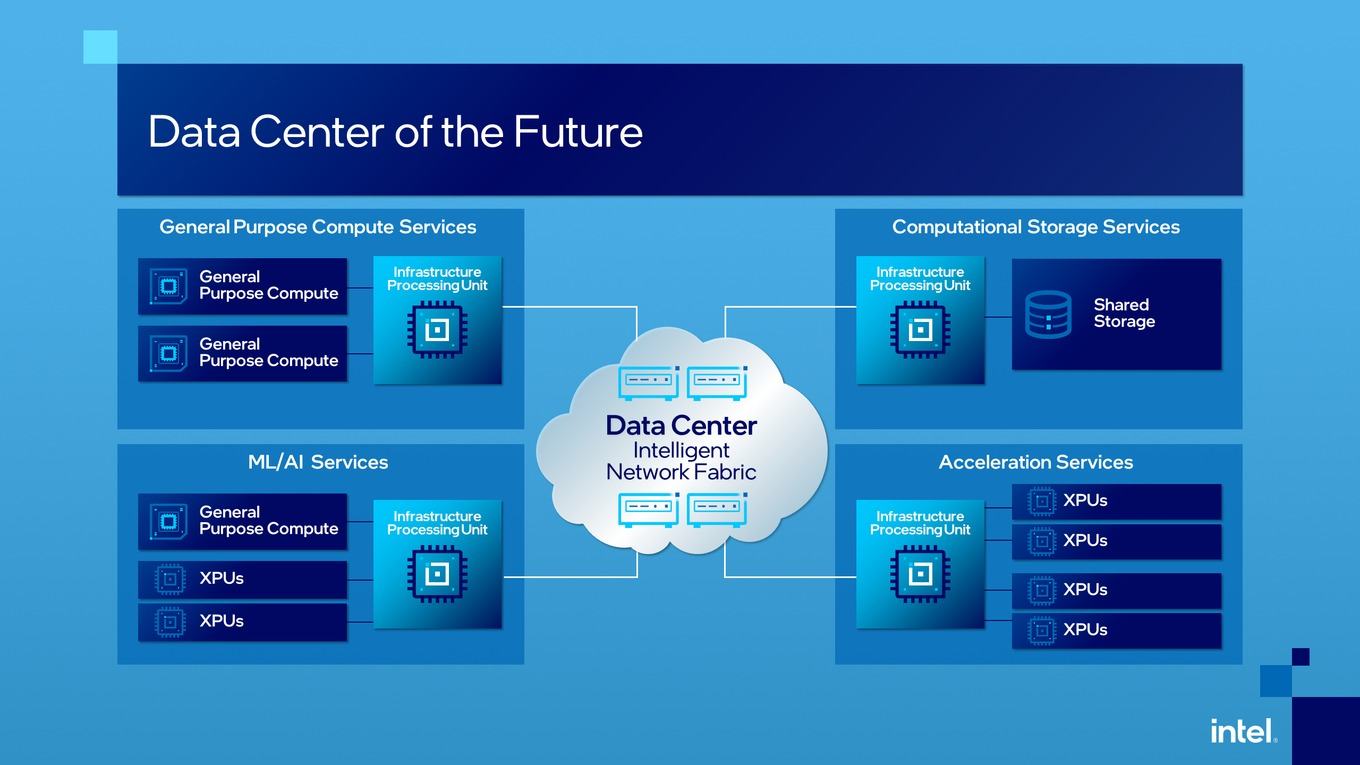

Aber die Begriffe IPU, DPU und Smart NICs werden häufig durcheinandergeworfen. Intel nennt seine Hardware als Schnittstellen im Rechenzentrum Infrastructure Processing Unit und verweist damit in gewisser Weise darauf, dass solche Chips nicht nur im Hinblick auf eine Optimierung des Speichers eine Rolle spielen können, sondern als intelligente Schnittstelle auch zwischen Compute-Hardware im Allgemeinen und Spezialbeschleunigern eingesetzt werden können.

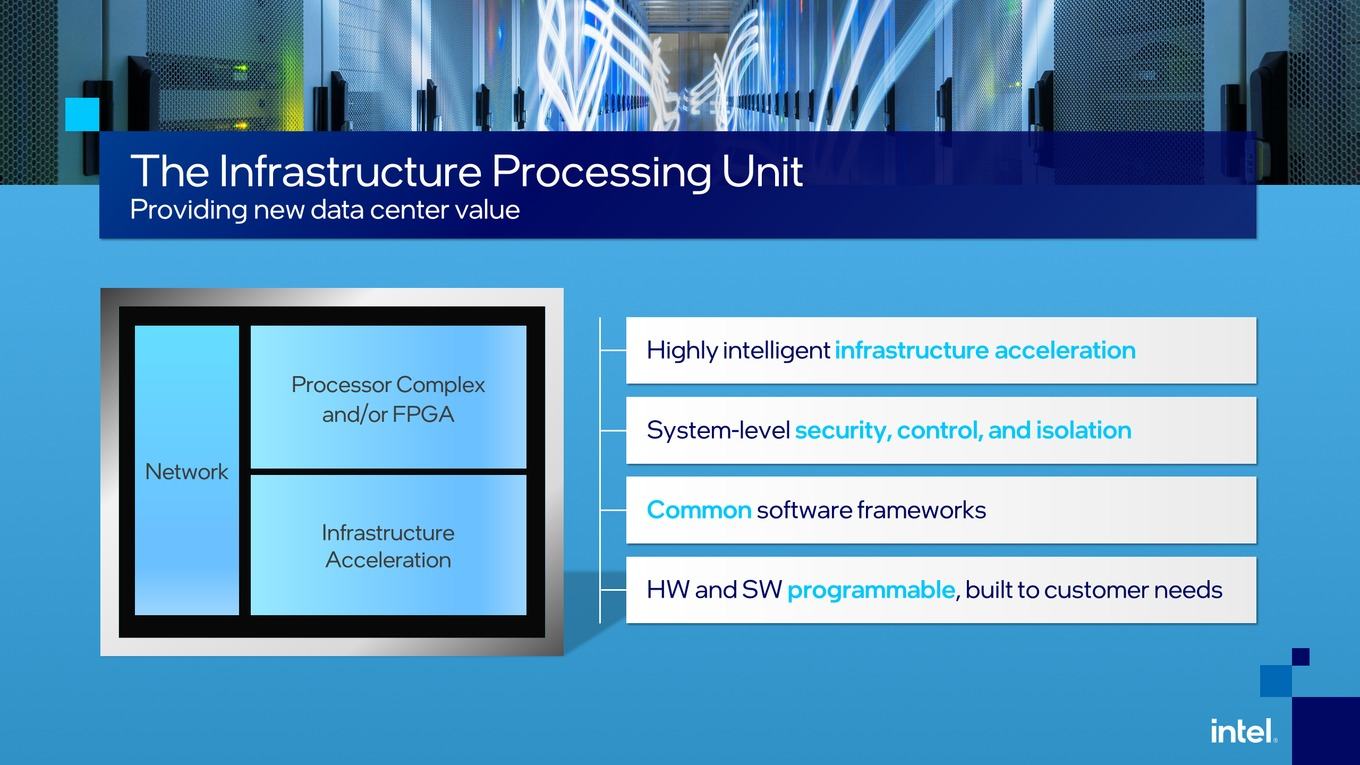

Grundsätzliches Ziel einer IPU (oder anders bezeichneten Hardware, wir bleiben für den folgenden Absatz bei IPU) ist es, die Applikationsebene und Infratrukturebene voneinander zu trennen. Dies soll einerseits Ressourcen besser planbar und an anderer Stelle freimachen, aber auch für eine höhere Sicherheit sorgen. Dazu ist die Hardware auf eben diesen Anwendungsbereich ausgelegt. Es gibt High-Speed-Networking (25 GBit/s, 50 GBit/s, 100 GBit/s, 200 GBit/s und zukünftig dann eben auch 400 GBit/s). Eine programmierbare Logik hilft dabei die Netztwerkpakete schnellstmöglich, also mit dem höchsten Durchsatz und geringer Latenz, zu verteilen. Unterstützt wird dies durch Hardwareeinheiten, die die Ver- und Entschlüsselung übernehmen. Neben den Spezialbeschleunigern sind auf den IPUs auch noch Rechenkerne vorhanden, die vom Arbeitsspeicher unterstützt werden. Die Anbindung der IPUs erfolgt meist über PCI-Express 4.0, später dann in PCI-Express 5.0.

Die Rechenaufgaben wären ansonsten größtenteils auf die Prozessorkerne des Serverprozessers ausgelagert worden. In großen VM-Umgebungen können bis zu acht CPU-Kerne verwendet werden, die dann nicht mehr den VMs zur Verfügung stehen. Ein Zwischenschritt zum IPU sind Smart NICs. Diese können einige Aufgaben in der Netzwerkschnittstelle bereits übernehmen, sind aber bei weitem nicht so flexibel.

Neben der Verwaltung des Netzwerktraffics kann eine IPU auch Speicher ans Netzwerk anbinden. Anstatt das NVMe-Laufwerke über einen Storageserver mit Xeon- oder EPYC-Prozessor angebunden werden, geschieht dies über eine IPU. Auch hier ist es das Ziel das Processing des Speichers vom Serverprozessor auszulagern. Die Verwaltung von mehrere NVMe-Laufwerken kann durchaus signifikant Ressourcen in Anspruch nehmen.

Eine IPU kann aber auch schon AI/ML-Aufgaben übernehmen, da hier bereits ein Inferencing stattfindet und damit nur Daten prozessiert und weitergegeben werden, die wirklich relevant sind. NVIDIA will DPUs (so bezeichnet NVIDIA diese Hardware) direkt mit GPU-Beschleunigern koppeln, die dann im Edge-Computing zum Einsatz kommen.

Aktuell arbeiten zahlreiche Unternehmen an IPUs/DPUs. Erwähnt haben wir bereits NVIDIA, aber auch Broadcom, Marvell, Pensando, Funglible und Xilinx bieten solche Hardware an bzw. haben entsprechende Hardware angekündigt. An dieser Stelle sei auch gesagt, dass zahlreiche Hyperscaler an eigener Hardware arbeiten. Dazu gehören unter anderem Microsoft, aber auch Facebook, Google und andere könnten daran interessiert sein und da diese ihren eigenen Anwendungsbereich sehr gut kennen, können sie die Hardware auch entsprechend auslegen.

Mit einigen Produkten auf Basis von Xeon-D-Prozessoren, FPGAs und Ethernet-Chips ist Intel in gewisser Weise schon auf dem Markt für IPUs vertreten. In Form des von Inventec angebotenen FPGA SmartNIC C5020X hat man bereits damit begonnen, eine IPU mit Stratix-10-FPGA und Xeon-D-Prozessor an Kunden zu Testzwecken auszuliefern. 4 GB an DDR4 stehen dem FPGA zur Verfügung und weitere 16 GB stehen dem Xeon-D zur Seite. Die Anbindung an das Host-System erfolgt per PCIe 3.0 x8. Bei den Netzwerkverbindungen ist man allerdings noch auf 25 oder 50 GBit/s beschränkt.

Intel bleibt noch recht vage

Aber nachdem die Begrifflichkeit geklärt ist, kommen wir nun zur eigentlichen Vorstellung von Intel. Die IPUs sollen dazu beitragen das Rechenzentrum effektiver und sicherer zu machen. Anstatt die CPU-Kerne mit den Aufgaben zu belasten, sollen die IPUs diese übernehmen.

Im Vorfeld hat uns Intel einige Neuigkeiten im Bereich der IPUs angekündigt. Bis auf wenige Zitate, wie das von Guido Appenzeller, CTO der Data Platforms Group, gibt es aber noch wenig konkretes zu verkünden:

"At Intel, we are dedicated to creating solutions and innovating alongside our customer and partners — the IPU exemplifies this collaboration."

Schon etwas konkreter wird Patty Kummrow, Vizepräsident der Data Platforms Group und General Manager der Ethernet Products Group bei Intel:

"As a result of Intel’s collaboration with a majority of hyperscalers, Intel is already the volume leader in the IPU market with our Xeon-D, FPGA and Ethernet components. The first of Intel’s FPGA-based IPU platforms are deployed at multiple cloud service providers and our first ASIC IPU is under test."

Eine FPGA-Plattform der IPUs haben wir im ersten Abschnitt bereits erwähnt. ASIC-Lösungen sollen in Kürze folgen. Laut Microsoft werden hier auch schon SmartNICs im Azure-Netzwerk verwendet, die auf Intel-Chips setzen.

Im Rahmen des "The Six Five Summit" spricht Intel womöglich noch über seine konkreten Pläne bei den IPUs. Der Talk von Navin Shenoy, General Manager der Data Platforms Group, läuft aktuell noch. Sollte sich Intel noch konkreter zu Produkten äußern, werden wir diese Meldung entsprechend ergänzen.