Werbung

Während IBM auf der HotChips Mitte August in diesem Jahr den Z Telum, einen z15-Nachfolger mit viel, teilweise virtuellem Cache, vorstellte, sprach man im vergangenen Jahr über die Power10-Architektur und die dazugehörigen Prozessoren, die es nun auch in die ersten Server geschafft haben.

Der E1080 ist nun der erste Server, der Prozessoren auf Basis von Power10 verwendet. Es handelt sich um ein System mit acht Sockeln und dementsprechend mit der gleichen Anzahl an Prozessoren. Gegenüber einem Power9-System soll der E1080 um den Faktor x2,5 schneller in AES und um den Faktor x4 schneller in anderen Kryptoanwendungen sein. Das Inferencing im AI-Bereich erledigt ein E1080 laut IBM fünfmal schneller als der Vorgänger E980.

IBM wagt außerdem Vergleiche zur x86-Konkurrenz. Im SAPs SD-2-Tier-Benchmark soll das Power10-System 6 % schneller als zwei 8S-Systeme mit Intels Xeon Platinum 8280L sein – wohlgemerkt mit nur der Hälfte an Prozessoren im Vergleich zu Intel. Für den SpecInt2017 nennt IBM eine um den Faktor x2,5 höhere Single-Threaded-Leistung gegenüber einem Xeon Platinum 8380H.

IBM macht noch keinerlei Angaben zu den einzelnen Konfigurationen, die erhältlich sein werden. Auch einen Preis nennt man nicht. Noch im September sollen die ersten Konfigurationen mit acht Prozessoren und bis zu 8 TB an Arbeitsspeicher verfügbar sein. Im Dezember sollen dann weitere Varianten folgen.

Hintergrund zu den Power10-Prozessoren

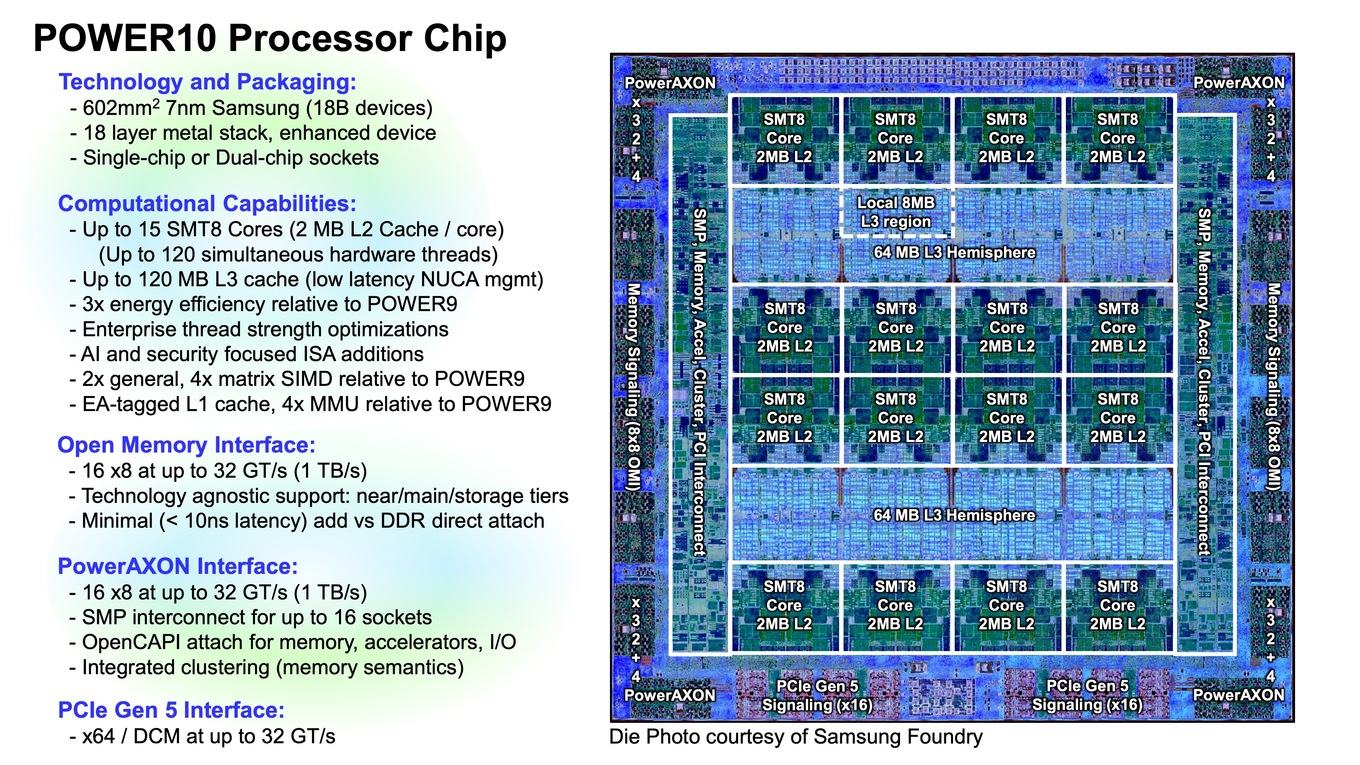

Ein Power10 wird bei Samsung in 7 nm gefertigt und kommt auf eine Chipfläche von 602 mm². Die Anzahl der Transistoren eines Power10-Prozessors liegt bei 18 Milliarden. Den Prozessor gibt es in zwei Varianten: Einmal als Single Chip Module (SCM) und einmal als Dual Chip Module (DCM).

Der Power10-Chip besitzt eigentlich 16 der Kerne, allerdings werden nur 15 dieser aktiv verwendet. Jeder Kern kann per Simultaneous Multithreading (SMT) bis zu acht Threads gleichzeitig bearbeiten und dazu stehen ihm exklusiv 2 MB an L2-Cache zur Verfügung. Chipübergreifend sind zudem 120 MB an L3-Cache vorhanden.

Die Aufteilung in ein Single Chip Module (SCM) und ein Dual Chip Module (DCM) begründet IBM mit den unterschiedlichen Bedürfnissen an die entsprechenden Anwendungen. Das SCM bietet alle Interface-Optionen mit der vollen Bandbreite an und eignet sich daher für Anwendungen, bei denen eben diese hohe Bandbreiten zusammen mit der entsprechenden Compute-Leistung gefragt sind. Die 15 Kerne erreichen in der SCM-Konfiguration einen Takt von 4 GHz und mehr. Bis zu 16 Sockets in der SCM-Konfiguration können zu einem Verbund zusammengeschaltet werden.

Wenn es um die Energieeffizienz geht, sieht IBM das DCM im Vorteil. Man kann hier zwei Power10-Chips in einem Package anbieten, wo zuvor nur ein Power9-Prozessor seinen Platz gefunden hat. Als Multi-Chip-Module arbeitet hier sozusagen ein Chip von 1.204 mm². Die Anzahl der miteinander verbundenen Sockets wird allerdings auf vier reduziert und hinzu kommt, dass die einzelnen Prozessoren mit einem reduzierten Takt von 3,5 GHz arbeiten.

Im DCM verdoppelt sich die Anzahl der PCI-Express-Lanes. Insgesamt vorhanden sind 64 PCI-Express-5.0-Lanes, die zusammengenommen auf eine Datenrate von 1 TB/s kommen. Das Speicher-Interface bleibt mit 16 x 8 Links identisch. Das PowerAXON-Interface wird von 16 x 8 auf 16 x 12 Links vergrößert.

Details zur Power10-Architektur finden sich in unserem Artikel zum IBM-Vortrag auf der HotChips im vergangenen Jahr.