Werbung

Noch vor dem offiziellen Start der Alder-Lake-Prozessoren hat Intel den dazugehörigen Developer Guide veröffentlicht, der weitere Einblicke in das Hybrid-Design gibt. Zum Architecture Day Mitte August sprach Intel bereits über die grundsätzlichen Details, hielt sich zur Topologie und dem Aufbau der verschiedenen Modelle aber noch zurück.

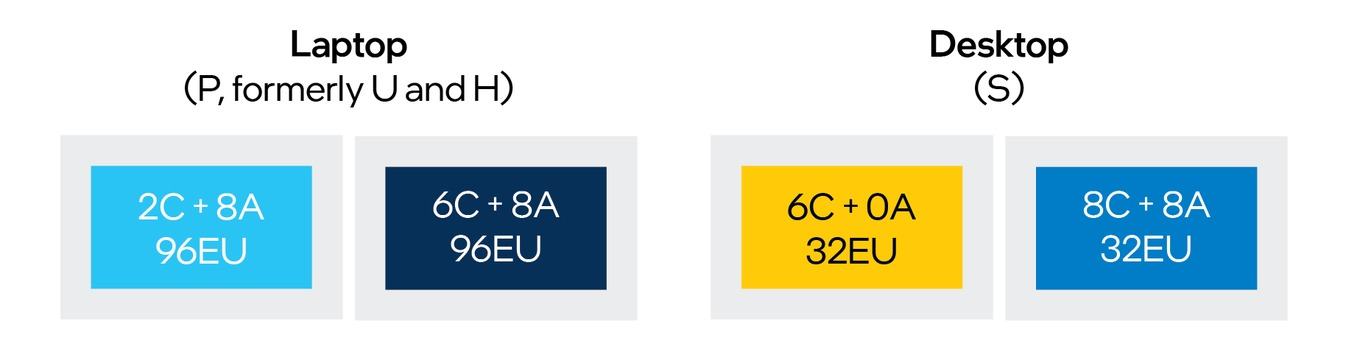

So konnte man bisher davon ausgehen, dass Intel drei verschiedene Designs vorsieht: Für den Desktop mit jeweils bis zu acht P- und E-Cores, für das Notebook-Segment mit bis zu sechs P-Cores (Golden Cove) und acht E-Cores (Gracemont) und für Ultra-Mobile mit bis zu zwei P-Cores und ebenfalls acht E-Cores. Beim Chip für Desktop und Notebooks kann man davon ausgehen, dass es auch Modelle mit teilweise deaktivieren Kernen geben wird.

Für Alder Lake-S zeigt der Developer Guide nun aber eine zweite Desktop-Variante:

Die bereits bekannte 8+8-Konfiguration wird offenbar noch um eine 6+0-Konfiguration ergänzt. Damit hätten wir vier unterschiedliche Chips, die bei Intel aus der Fertigung rollen. Wie genau Intel die Modellpalette aufbauen wird, erfahren wir Ende Oktober zum offiziellen Start von Alder Lake-S.

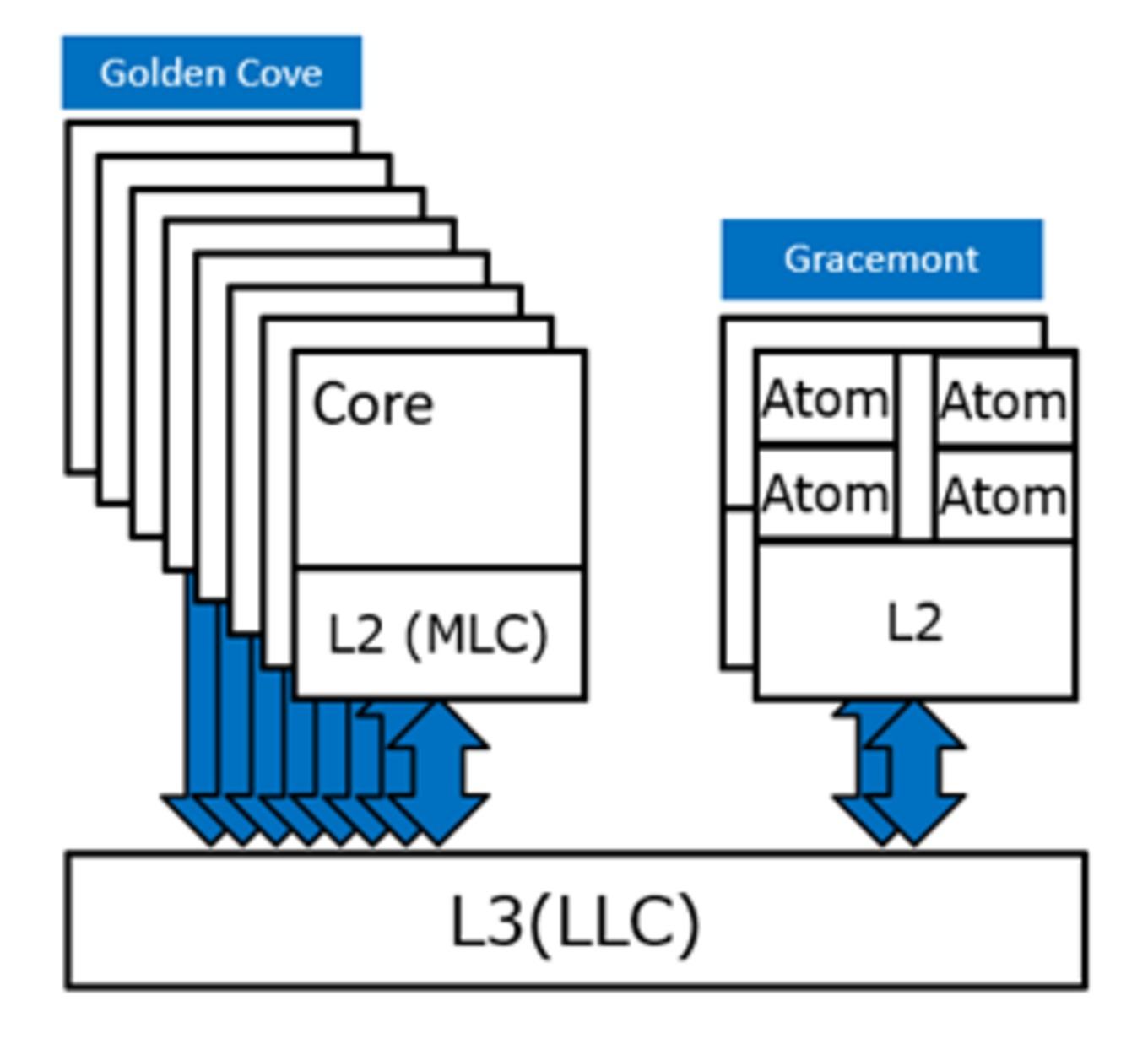

In diesem Zusammenhang interessant, ist zudem ein Blick auf die Topologie von Alder Lake-S, auf die im Rahmen des Developer Guides ebenfalls eingegangen wird. Intel hat bereits bestätigt, dass für Alder Lake bis zu 30 MB an L3-Cache zur Verfügung stehen – natürlich abhängig vom jeweiligen Modell. Im Falle einer 6+0-Konfiguration steht den P-Cores der volle L3-Cache zur Verfügung, da sie sich diesen nicht mit den E-Cores teilen müssen. Wie groß der L3-Cache für solche Prozessoren ausfällt, wird sich noch zeigen müssen.

Vier E-Cores (Atom-Kerne auf Basis von Gracemont) teilen sich einen geneinsamen L2-Cache, während dieser bei den P-Cores exklusive ist. Die P-Cores können im Grunde einzeln umgesetzt werden, während die E-Cores immer in Clustern von jeweils vier Kernen vorhanden sind.

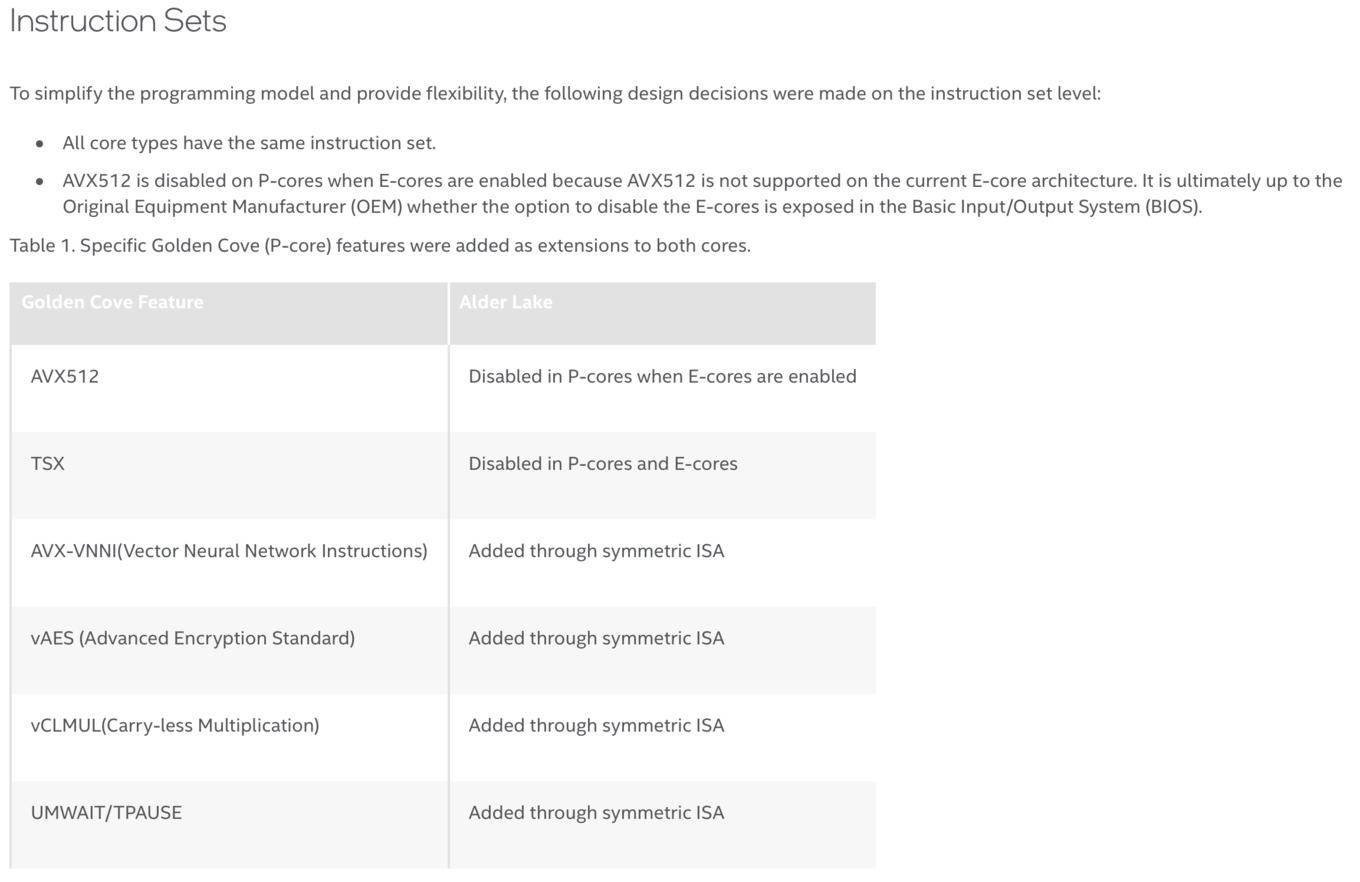

AVX512 war geplant, wurde aber wieder entfernt

Interessanterweise plante Intel offenbar die Umsetzung von AVX512-Befehlssätzen mit Alder Lake-S. Für die aktuellen Rocket-Lake-Prozessoren ermöglicht Intel den Einsatz von AVX512, was besonders im wissenschaftlichen Umfeld und für bestimmte Anwendungen zu einem deutlichen Leistungsplus führen kann. Da die Instructions Sets zwischen den Kernen aber identisch sein müssen und die E-Cores kein AVX512 unterstützen, ist dies auch auf den P-Cores deaktiviert:

"AVX512 is disabled on P-cores when E-cores are enabled because AVX512 is not supported on the current E-core architecture."

Offenbar aber ist es möglich, AVX512 zu aktivieren, wenn keine E-Cores vorhanden oder diese deaktiviert sind:

"It is ultimately up to the (OEM) whether the option to disable the E-cores is exposed in the BIOS"

Einzelne Kerne sollen sich im BIOS deaktivieren lassen, so die bisherige Informationslage und damit wäre es auch möglich die E-Cores zu deaktivieren, um AVX512 ermöglichen zu können.

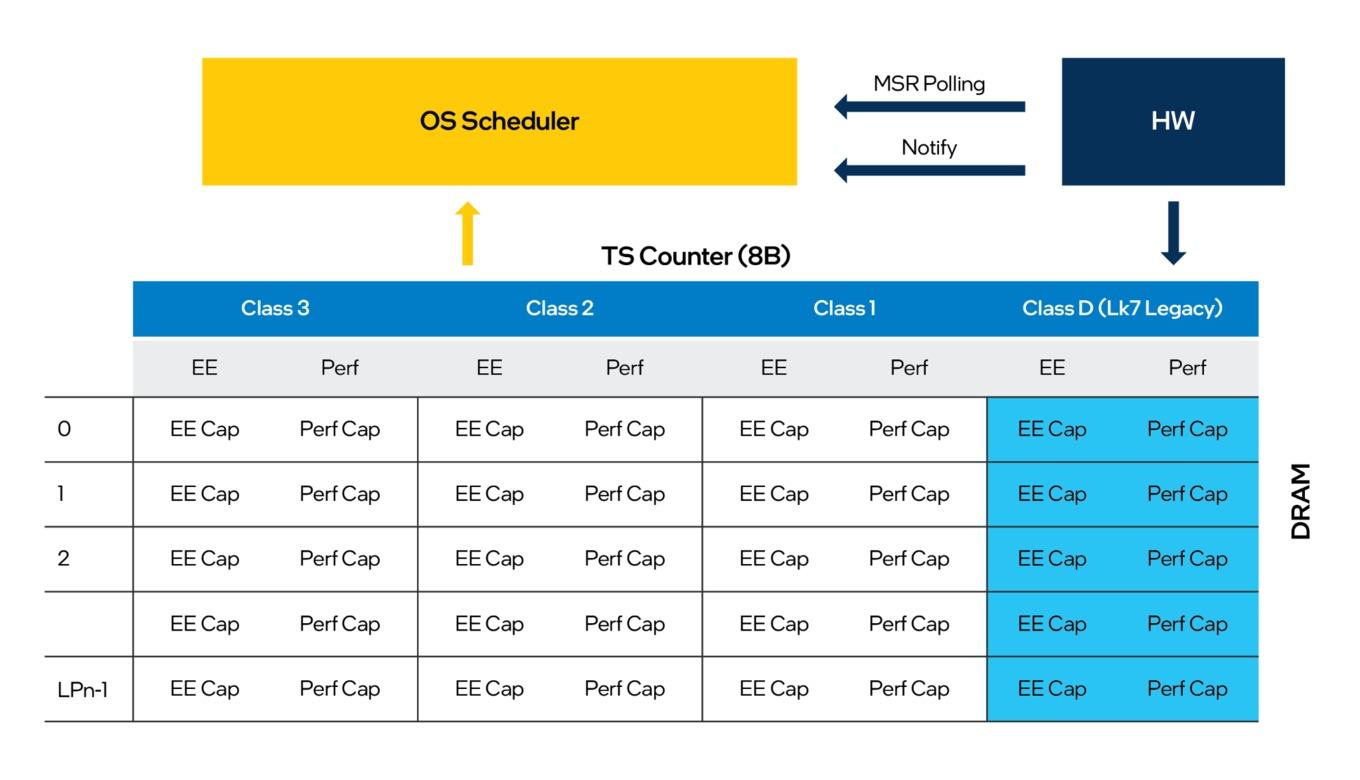

Im Developer Guide viel Zeit wird auf den Intel Thread Director (ITD) aufgewendet. Dieser wurde auf Basis des Lakefield Hardware Guided Scheduling (HGS) entwickelt und schafft die Verbindung zwischen der Hybrid-Hardware und dem Betriebssystem, sodass die zur Verfügung stehenden Ressourcen möglichst optimal genutzt werden. Einige Details zum ITD hat das Unternehmen bereits veröffentlicht.

Eine gute Telemetrie ist entscheidend, damit der Thread Director möglichst effizient arbeiten kann. Die laufenden Anwendungen werden in vier Prioritätsklassen eingeteilt. Alle 30 ms gibt der Thread Director die Arbeitslast und Gruppeneinteilung an den Scheduler des Betriebssystems weiter. Die IPC-Leistung der einzelnen Kerne ist entscheidend für die Beurteilung, ob ein Thread einem P- oder einem E-Core zugeteilt bzw. ob ein Wechsel vollzogen wird. Unter Umständen kann es sein, dass ein Verbleiben auf dem P-Core sinnvoller ist, als ein Wechsel auf die E-Cores – genauso gilt dies umgekehrt.

Im Rahmen unseres Launch-Reviews zu Alder Lake-S werden wir auf alle eben erwähnten Techniken noch einmal genauer eingehen. Die Veröffentlichung des Developer Guides zu diesem Zeitpunkt zeigt allerdings sehr schön, dass das Hybrid-Design eine Zäsur in Intels Verständnis zum Aufbau eines Prozessors darstellt, was auch entsprechende Änderungen auf Softwareebene notwendig macht.

Am 19. bzw. 21. Oktober wollen AMD und Microsoft die Patches bzw. Treiber veröffentlichen, die dann auch die Probleme im Zusammenhang mit dem L3-Cache und der Zuteilung der besten Kerne bei den Ryzen-Prozessoren beheben sollen. Der Windows 11 Build 22000.282 mit dem L3-Cache-Fix befindet sich schon im Dev-Channel.