Werbung

Lichtwellenleiter haben bereits zahlreiche Anwendungsbereiche. Meist geht es dabei aber um eine Langstreckenkommunikation über mehrere Kilometer bis hinunter auf wenige Meter. Bereits seit Jahren wird als "Silicon Photonics" an Technologien gearbeitet, die Lichtwellenleiter in Bereiche bringen sollen, die von wenigen Zentimetern bis auf wenige Millimeter reichen.

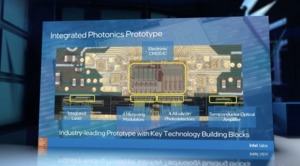

Da man dieser Technik in Zukunft viel zutraut, hat Intel jetzt ein Integrated Photonics Research Center eröffnet. Hier sollen die schon angeworfenen Entwicklungen zentral weitergeführt werden. Intel spricht hier vor allem von einer Integration von Tranceiver und Transmitter in Halbleierbauelemente, eine Integration in Packaging-Technologien und Kopplungen der Lichtwellenleiter.

Konkret spricht Intel auch einen ersten Anwendungsbereich dieser Technik an, der allerdings wenig überraschend ist: "Research Center for Integrated Photonics for Data Center Interconnects" – natürlich werden die Serverprodukte als erstes mit dieser Technologie ausgestattet werden, denn hier sieht Intel das größte Potenzial in der Skalierung seiner Produkte.

Verschiedene Universitäten sind Teil des Integrated Photonics Research Center und tragen in den unterschiedlichen Bereichen dazu bei, dass eine Weiterentwicklung stattfindet.

Darunter sind Projekte, die fotoelektrische Modulatoren und Resonanz-Detektoren entwickeln, die effiziente Übertragungen mit 40 TBit/s bei gerade einmal 150 fJ/Bit ermöglichen. Als Packaging-Technologie für einen Interconnect soll eine Dichte von 16 TB/s/mm I/O erreicht werden.

Dazu ein paar Vergleichswerte:

| Energieeffizienz | Dichte | |

| University of California (Silicon Photonics) | 0,15 pJ/Bit | 10.000 Bumps/mm² |

| TSMC (CoWoS) | 0,56 pJ/Bit | 625 Bumps/mm² |

| Intel Foveros Die Interface (FDI) | 0,2 pJ/Bit | 828 Bumps/mm² |

| Intel Foveros Omni | - | 1.600 Bumps/mm² |

| Intel Foveros Direct | - | 10.000+ Bumps/mm² |

| Intel EMIB | 0,3 pJ/Bit | 560 Bumps/mm² |

| OpenFive D2D-Interface | 0,5 pJ/Bit | - |

| AMD (MCM-Interface per IF) | 2 pJ/Bit | 60 Bumps/mm² |

| AMD 3D-Stacking (3D V-Cache) | - | 10.000+ Bumps/mm² |

Direkt miteinander vergleichen lassen sich die verschiedenen Techniken natürlich nicht immer. Hier muss man immer unterscheiden, ob eine Anbindung eines Chips auf einem Interposer stattfindet, ob zwei Chips miteinander verbunden werden sollen oder ob ein Stacking mehrere Chips stattfindet. Es zeigen sich hier aber recht eindeutig die verschiedenen Generationen und Fortschritte, die schon gemacht wurden. Von wenigen Kontakten pro Quadratmillimeter, ging es auf einige hundert und nun auf bis 10.000 und mehr.

Die Abstände der Micro-Bumps betragen in einem BGA so etwas wie 150 µm, wenn ein Chip mit einem Trägersubstrat kontaktiert werden soll. Für die aktuell verwendeten Interfaces ging es auf etwa 50 µm. Mit dem 3D V-Cache und zukünftigen Technologien sollen dann 10 µm und weniger erreicht werden.

Die Energieeffizienz besitzt ebenfalls zahlreiche Abhängigkeiten, sodass ein direkter Vergleich auch hier schwierig ist.