Werbung

Neben technischen Details zum Aufbau der ersten BonanzaMine-Generation sprach Intel auch über den Aufbau der nächsten Xeon-Generation Sapphire Rapids. Ziel war es hier, einen Prozessor bestehend aus zwei unterschiedlichen Dies so zu gestalten und miteinander zu verbinden, dass dieser wie ein monolithischer Chip arbeitet und ähnliche Leistungsdaten erreicht. Viermal 400 mm² (die tatsächliche Größe liegt leicht unter 400 mm²) sitzen auf dem Package und wären entsprechend als 1.600-mm²-Chip nicht zu fertigen. Jeder dieser Chips hat laut Intel zwischen 11 und 12 Milliarden Transistoren.

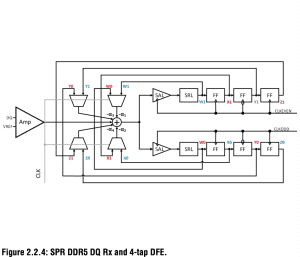

Zunächst aber verloren die Vortragenden ein paar Worte zur Fertigung der Chips selbst. Gefertigt werden diese in Intel 7 (10 nm) mit Dual-Poly-Pitch SuperFin (SF) Transistoren, einer um mehr als 25 % größeren MIM-Dichte (Metal-Insulator-Metal) im Vergleich zu SuperMIM sowie einem Metal Stack mit einer optimierten Routing-Schicht mit 400 nm Abstand. Letztgenannte Maßnahme ist essentiell, da die Latenzen für den Interconnect reduziert werden sollten.

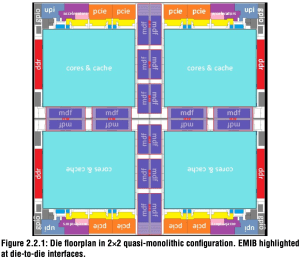

Spätestens seit der HotChips 33 ist bekannt, dass Intel für Sapphire Rapids zwei gespiegelte Dies mit jeweils 400 mm² verwendet, die in einer 2x2-Matrix auf einem Trägersubstrat untergebracht sind. Zehn EMIB-Verbindungen sorgen dafür, dass die vier Chips sich nach Außen hin wie einer darstellen.

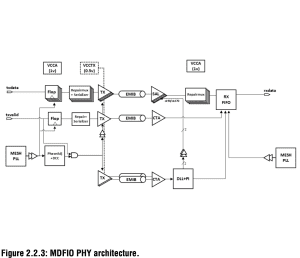

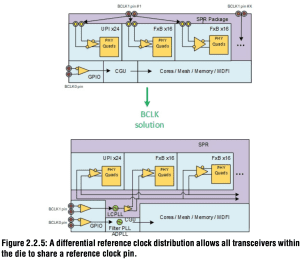

Auf der ISSCC 2022 legte Intel das interne Layout erstmals offen. Jeder Chip wird über zwei bzw. drei Multi-Die Fabric IO (MDFIO) getaufte Interconnects miteinander verbunden. Hier sehen wir also eine gewisse Asymetrie, deren Auswirkungen wir aktuell noch nicht kennen. Die Effizienz einer solchen Verbindung ist neben der Bandbreite aber entscheidend, denn es hilft wenig, wenn der Interconnect einen Großteil der Energie aufnimmt und somit weniger für die eigentlichen Kerne und weiteren Komponenten übrig bleibt. Laut Intel kommt der MDFIO auf 0,5 pJ/B. Per dynamischer Frequnzanpassung kann der Fabric IO sich aber auch der Last anpassen und arbeitet mit einem Dynamic Voltage Frequency Scaling (DVFS) mit einem Takt zwischen 800 MHz und 2,5 GHz.

Die kumulierte Bandbreite des Fabric liegt bei 10 TB/s (20 Crossings mit je 500 GB/s). Die Round-Trip-Latenz im MDFIO soll bei weniger als 10 ns liegen.

Viel Redundanz um Ausbeute zu verbessern

Aber auch wenn die für Sapphire Rapids verwendeten Chips mit 400 mm² vergleichsweise klein sind, so hat Intel sich wohl aufgrund der bisherigen Erfahrungen mit der Fertigung in 10 nm dazu entschlossen viele Maßnahmen zu ergreifen, um eventuelle Defekte ausgleichen zu können. Diese gehen über das hinaus, was Intel bisher an Reparatur- und Wiederherstellungsmethoden angewendet hat und betrifft die Bereiche Core (die eigentlichen Performance-Kerne) ebenso wie die Caches, Uncore und I/O-Blöcke.

Redundante Schaltkreise in gefährdeten Bereichen sind eine Maßnahme, um bei einem eventuellen Defekt auszugleichen. Für den MDFIO können einzelne Verbindungen wiederhergestellt werden, um Fehler vor und nach der Montage des gesamten Packages zu beheben.

Ungenutzte PCIe-Blöcke im "südlichen" Bereich des Chips ermöglichen die Wiederherstellung einiger I/O-Blöcke durch eine Umwidmung. Insgesamt sind laut Intel 74 % des Chips wiederherstellbar. Einmal aus vier Chip zusammengesetzter Prozessor lässt sich in seinen einzelnen Funktionen und Verbindungen aber gar nicht mehr so einfach testen. Intel musste sich auch hier Mittel und Wege einfallen lassen, um beispielsweise direkt an der EMIB-Verbindung Tests durchführen zu können oder sieht GPIO-Pins und sieht auch die Verwendung von JTAG vor.

Intel scheint viel Aufwand zu betreiben, um ein Design wie Sapphire Rapids als Zwitter zwischen einem Chiplet-Design und einem monolithischen Chip auf den Weg zu bringen. Angaben wie die 74 % des Chip, die theoretisch wiederherstellbar sind, können wir an dieser Stelle nicht vergleichen. Was aber vergleichbar sein wird, sind die Angaben zur Latenz und der Interconnect-Leistung. Dazu wird man aber die Tests der nächsten Xeon-Generation abwarten müssen.

Auf Sapphire Rapids wird Emeralds Rapids als nächstes Design folgen, welches wohl die gleichen Prinzipien im Package-Design verwenden wird. Granite Rapids und Sierra Forest werden im Rahmen der P-Core und E-Core-Aufspaltung ein Tile-Design verwenden.