Werbung

Das Intels nächste Xeon-Generation alias Sapphire Rapids mit größeren Verzögerungen zu kämpfen hat, ist keine wirkliche Neuigkeit. Bereits vor 18 Monaten war die Markteinführung geplant, geschehen ist bis heute wenig – zumindest nach Außen hin.

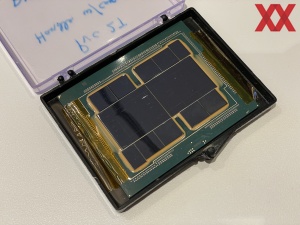

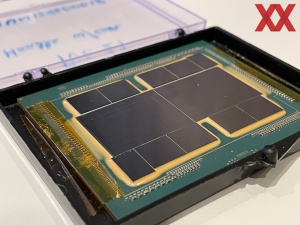

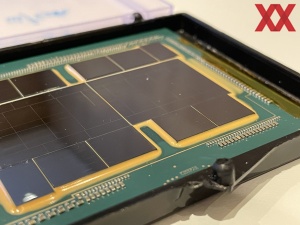

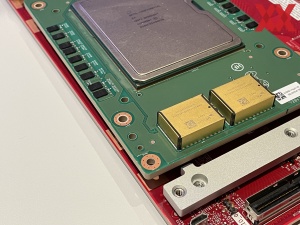

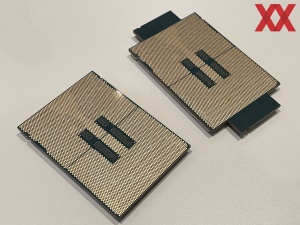

Bereits seit Monaten tüfteln Intel und die Partner an der dazugehörigen Plattform. Zur ISC 2022 sprachen wir mit einigen dieser Partnern und unisono war von einer komplizierten und aufwendigen Validierung der Plattform zu hören, was vor allem in der Komplexität durch DDR5 und PCI-Express 5.0 begründet sein soll. Immerhin: Sapphire Rapids mit und ohne HBM2e setzen auf den gleichen Sockel.

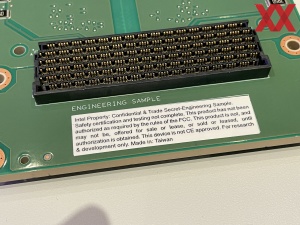

Der aktuelle, offizielle Zeitplan sieht größere Stückzahlen für Ende 2022 vor. 2023 soll dann der Höhepunkt erreicht werden. Damit rückt Sapphire Rapids aber auch sehr nahe an den plattformkompatiblen Nachfolger Emerald Rapids. Gerüchten zufolge, hat Intel das Zeitfenster für Sapphire Rapids aber abermals verschoben. Zwischen dem 6. Februar und dem 3 März 2023 soll es nun soweit sein.

Was ist los bei Intel?

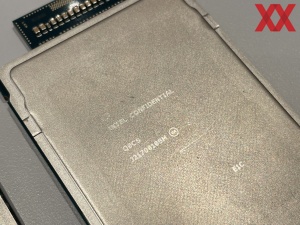

Aber die Frage ist, warum sich Sapphire Rapids derart verzögert. Nur die Plattform bzw. deren Validierung bei und durch die Partner kann es ja nicht sein. In den vergangenen Monaten tauchten auch immer wieder neue Steppings auf, was auch nicht weiter unüblich ist. So gab es ein A0, A1, B0, C0, C1, C2, D0, E0, E2, E3, E4 und nun aktuell ein E5 Stepping. Zwölf Steppings sind aber deutlich mehr, als das, was wir sonst zu Gesicht bekommen. Wie kommt es dazu?

Ist ein Prozessor-Design mit mehreren Milliarden Transistoren fertiggestellt, geht es in die Fertigung und kommt in einer ersten Version zurück. Nur sehr selten sind hier keinerlei Fehler mehr vorhanden. Einige lassen sich per Firmware beheben, andere wiederum verlangen nach Änderungen auf Ebene der Transistoren. Dann muss ein neues Stepping her. Diesen Zyklus scheint Intel für Sapphire Rapids nun aber extrem häufig durchlaufen zu haben.

Nach außen hin kommunizieren die Hersteller immer gerne ihr Tape Out. Dies beschreibt den Zeitpunkt, wenn das erste Design aus der Fertigung zurückkommt und in den Laboren getestet wird. So hat Intel bereits vor Monaten das Tape Out für den Compute Tile von Meteor Lake verkündet. Auch der Nachfolger von Sapphire Rapids, Emerald Rapids, soll bereits das Tape Out geschafft haben.

Doch die Post-Silicon-Phase (Post Silicon Bringup), also das Testing und die Validierung der Prozessoren nach der initialen Fertigung scheinen aktuell das große Problem zu sein. Üblicherweise dauert diese Phase 12 bis 18 Monate. Bei Intel sind es in den vergangenen Design-Wechseln aber häufig deutlich mehr gewesen. Sapphire Rapids bewegt sich inzwischen in einem Zeitraum von mehr als 24 Monaten.

Gröbere Fehler sollen bereits durch Verifikations-Tests in der Pre-Silicon-Phase (Pre Silicon Bringup) vorhergesehen, sodass diese gar nicht erst mit in die Fertigung übernommen werden. Pre und Post Silicon Bringup scheinen bei Intel nicht Hand in Hand zu laufen und so kommt es zu den größeren Verzögerungen, die wir aktuell bei Sapphire Rapids sehen. Doch auch auf Seiten der Werkzeuge in der Unterstützung der Fertigung gibt es offenbar Probleme. So sollen die Custom Verification EDA Tools fehlerhaft und Process Design Kits (PDK) ungenau sein, was sich letztendlich auf die Post- und Pre-Silicon-Phase negativ auswirkt.

Der einstige Weltmarktführer in der Herstellung von Halbleiterbauelementen, sprich Chips, kämpft also in seiner einstigen Kernkompetenz darum den Anschluss nicht zu verlieren. Die Auswirkungen zeigen sich nicht erst kürzlich durch immer wieder verschobene Produkte.