Werbung

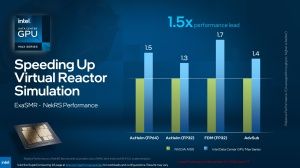

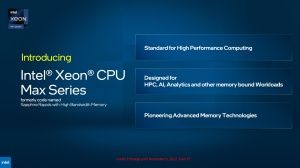

Bereits in mehreren Stufen hat Intel über die Xeon-Prozessoren sowie die GPU-Beschleuniger Ponte Vecchio gesprochen. Eine finale Vorstellung der entsprechenden Produkte steht nach wie vor aus. Heute allerdings gibt Intel einige weitere Details bekannt, darunter neue Kennzahlen zu den Xeon-Prozessoren der vierten Generation alias Sapphire Rapids mit HBM und die konkreten Produktnamen sowie Ausbaustufen der Ponte-Vecchio-GPU-Beschleuniger.

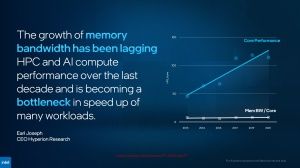

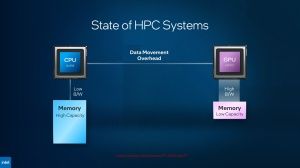

Dabei legt Intel den Fokus bei den Xeon-Prozessoren vor allem auf die Speicherbandbreite, die dank des HBM2e deutlich gesteigert werden kann. Für die GPU-Beschleuniger spielen sowohl die Kapazität der Caches, als auch die schnelle Anbindung des externen Speichers eine entscheidende Rolle.

SPR HBM: 56 P-Cores und viele Beschleuniger

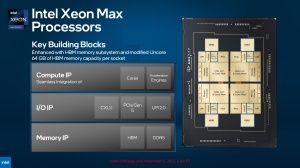

Die Xeon-Prozessoren der vierten Generation alias Sapphire Rapids mit HBM2e sollen die Speerspitze in Intels Datacenter-CPU-Strategie darstellen. Einzelne Produkte stellt man heute nicht vor, nennt jedoch einmal mehr die Anzahl der CPU-Kerne. Maximal 56 der Performance-Kerne sollen es sein. Mehrere Modelle dieser Max-Serie wird es geben, die allesamt mit 64 GB an HBM2e ausgestattet sind. Die Speicherbandbreite der vier Stacks liegt bei mehr als 256 GB/s pro Stack und dementsprechend bei mehr als 1 TB/s. Bei acht DDR4-Speicherkanälen kamen wir bisher auf 204,8 GB/s – nur um die Anbindung des HBM2e in ein Verhältnis setzen zu können.

Die Prozessoren mit HBM können nur mit diesem Speicher arbeiten (HBM only). Anwendungen müssen nicht angepasst werden und laufen mit diesem Speichermodell wie zuvor – nur eben mit deutlich höherer Bandbreite und auf 128 GB in einem 2S-System limitiert. Ebenfalls möglich ist es, Serverboards mit DDR5-DIMMs einzusetzen. Im "HBM Flat"-Mode gibt es zwei Speicherregionen (HBM und DDR5) und die Software muss darauf angepasst sein, um davon zu profitieren. Der HBM kann im "HBM Caching"-Mode aber auch als Cache genutzt werden – Anpassungen sind hier nicht notwendig.

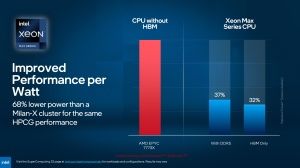

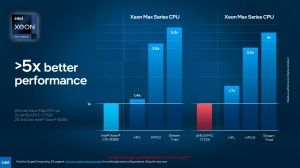

Auch AMD bietet mit den EPYC-Prozessoren mit 3D V-Cache (Milan-X) Modelle mit größerem Cache an. Beim Leistung-pro-Watt-Verhältnis sieht sich Intel mit Sapphire Rapids dennoch deutlich besser aufgestellt – sowohl mit DDR5-Speicher als auch im "HBM only"-Mode. Dies betrifft Benchmarks wie HPL, HPCG und Stream Triad und gegenüber den eigenen Vorgänger Ice Lake-SP.

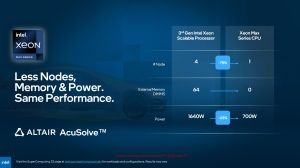

Die Xeon-Max-CPUs sollen die Kunden in die Lage versetzen, anstatt eines großen Servers mit vier Sockeln, 64 RAM-DIMMs und einer Leistungsaufnahme von 1.640 W gegen ein solches Modell mit nur zwei Xeon-Prozessoren mit HBM2e, ohne die Anschaffungskosten für DDR5-Speicher und mit einer Leistungsaufnahme von nur noch 700 W auszutauschen.

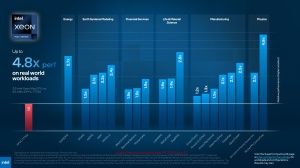

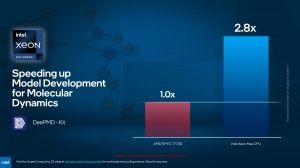

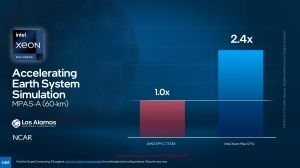

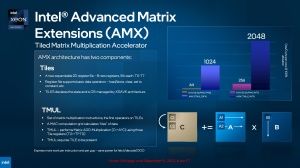

Die Xeon-Prozessoren bieten zudem Advanced Matrix Extensions (AMX). In jedem Performance-Kern hat Intel einen AMX-Beschleuniger verbaut. Die QuickAssist Technology (Komprimierungs- und Verschlüsselung-Beschleuniger) ist nun Bestandteil des SoCs. Zudem besitzt die 4. Generation der Xeon-Prozessoren einen DSA (Data Streaming Accelerator), DLB (Dynamic Load Balancer) und den IMAA (In-Memory Analytics Analyzer). Allesamt sollen diese Funktionseinheiten dazu beitragen, dass die Xeon-Prozessoren deutlich schneller als die Vorgänger und vor allem die Konkurrenz sind.

UMA Clustering für niedrigere Latenzen

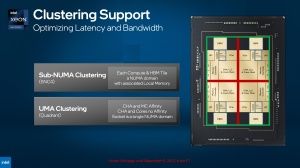

Für Server-Prozessoren auf Basis mehrere Chiplets zunehmend wichtig werden die Latenzen und Bandbreiten zwischen den einzelnen Chips. Per Clustering können einzelne Knoten voneinander getrennt werden, so dass die Speicherzugriffe nicht über andere Chiplets laufen müssen, was die Latenzen erhöht.

Für Sapphire Rapids macht Intel ein Sub-NUMA Clustering zugänglich, welches als SNC4 bereits bekannt ist. Hier werden die vier Chiplets mit ihrem HBM und den dazugehörigen Speichercontrollern als einzelne Knoten betrachtet. Je nach Anwendung kann dies Sinn machen.

Mit dem UMA Clustering bietet Intel nun aber auch eine Möglichkeit, die CPU-Chiplets samt des dazugehörigen HBM als einzelne NUMA-Node festzulegen. Die Caching Agents und Speichercontroller wurden so optimiert, dass es keinerlei Nachteile hinsichtlich der Latenz geben sollte.

Intel hat bereits angekündigt, dass man die vierte Generation der Xeon-Prozessoren am 10. Januar 2023 offiziell vorstellen wird. Dann werden wir die Taktraten und weiteren Modelle von Sapphire Rapids kennen.

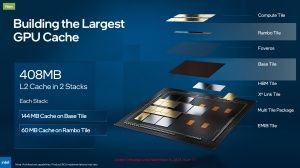

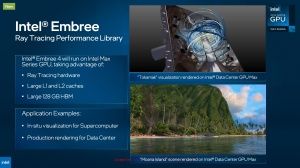

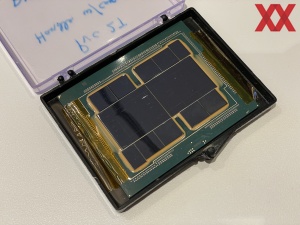

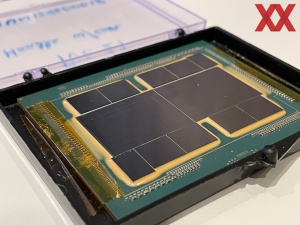

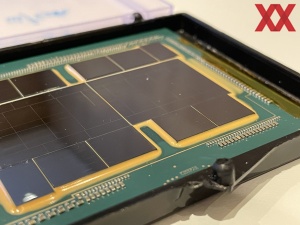

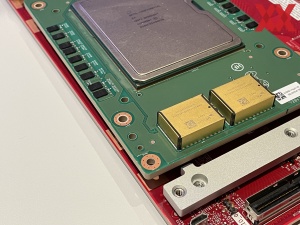

Ponte Vecchio: Intel Datacenter Max Series

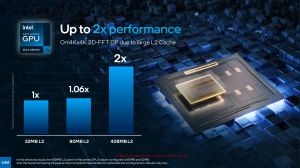

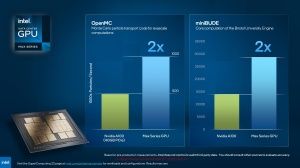

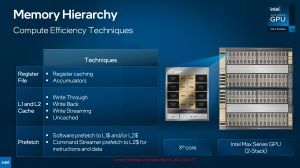

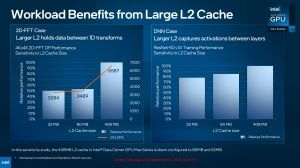

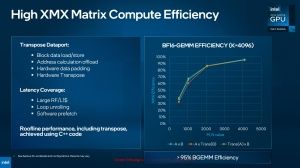

Von den Ponte-Vecchio-GPUs sind bereits ebenfalls einige Details bekannt. Auch hier spielen eine schnelle Anbindung des Speichers, vielmehr aber die Cache-Hierarchie eine entscheidende Rolle. Intel verzichtet auf einen großen L3-Cache, nach dem L2-Cache mit bis zu 408 MB folgt auf der nächsten Speicherebene ein 128 GB großer HBM2e. Es gibt aber auch einen insgesamt 64 MB großen L1-Cache.

Die Cache-Hierarchie sieht wie folgt aus: 64 MB an Register File in den Xe-Kernen. Der L1-Cache ist mit 64 MB ebenso groß dimensioniert. Die Bandbreite für den L1-Cache sinkt von 419 auf 105 TB/s über das gesamte Package hinweg. Der L2-Cache bemisst sich mit 408 MB und ist damit im Verhältnis 6:1 größer als der L1-Cache. Dafür gibt es laut Intel gute Gründe, denn einige Anwendungen profitieren deutlich von einem derart großen L2-Cache – andere wiederum nicht. Die Bandbreite für Lesezugriffe sinkt abermals von 105 TB/s im L1-Cache auf 13 TB/s auf den L2-Cache. Von hier geht es dann mit 3,2 TB/s zum HBM2E.

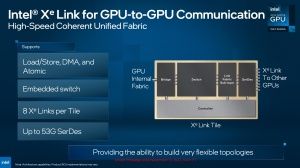

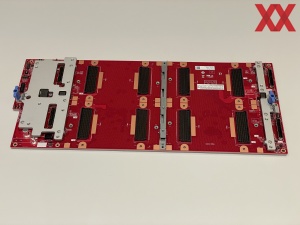

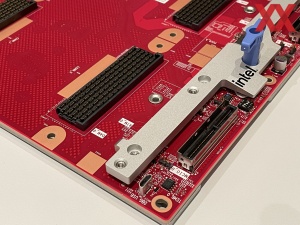

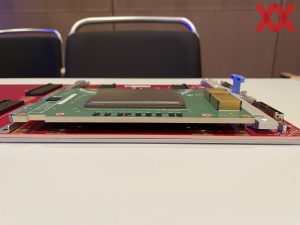

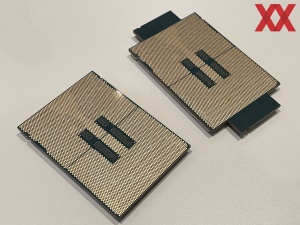

Was wir soeben beschrieben haben, ist die 2-Stack-Version von Ponte Vecchio. Den Einstieg macht Intel allerdings mit der Max Series GPU 1100 und dabei handelt es sich um eine PCI-Express-Karte mit der nur halb so großen 1-Stack-Version von Ponte Vecchio. Dementsprechend bietet die Karte 56 Xe-Kerne, 48 GB an HBM2e und zudem "nur" 32 MB an L1- sowie 204 MB an L2-Cache. Die TDP der Max Series GPU 1100 liegt bei 300 W. Über eine Xe-Link-Bridge können vier dieser Karten zusammengefasst werden.

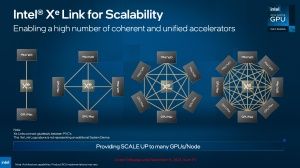

Für größere Systeme sieht Intel die OAM-Versionen von Ponte Vecchio vor. Die Max Series GPU 1550 bildet das Flaggschiff und kommt im Vollausbau von 128 Xe-Kernen und 128 GB an HBM2e daher. Die TDP liegt bei 600 W und per 53G Slides können acht dieser Module miteinander verbunden werden. Außerdem wird es noch eine im Ausbau reduzierte Variante, die Max Series GPU 1350 geben. Diese kommt auf 112 Xe-Kerne, 96 MB an HBM2e und eine TDP von 450 W.

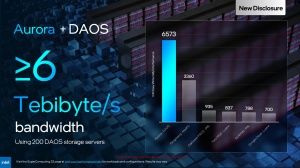

Das Datacenter GPU Max Subsystem wird es auch mit vier OAM-Modulen geben. Entsprechend der Max Series GPU liegt die TDP bei 1.800 oder 2.400 W und der HBM2e kann bis zu 512 GB groß sein – vier Module per Xe-Link zusammengefasst.

Schlussendlich gab Intel einen Ausblick auf das, was noch kommen wird – sprich eine aktuelle Roadmap. Aus dieser geht hervor, dass Sapphire Rapids mit Emerald Rapids zwar einen bereits bekannten Nachfolger bekommen wird, dieser aber offenbar keine Max-Series-Ableger mit HBM bekommen wird.

Sapphire Rapids läuft an diesem Punkt parallel zu Emerald Rapids. Wie wir aus vorherigen Veröffentlichungen von Intel wissen, wird auch Emerald Rapids noch in Intel 7 gefertigt und soll bereits 2023 auf den Markt kommen. 2024 wird dann Granite Rapids folgen. Diese Prozessoren sollen dann in Intel 3 gefertigt werden. Parallel dazu wird es mit Sierra Forrest die ersten Xeon-Prozessoren geben, die ausschließlich auf die Efficiency-Kerne setzen.

Bei den GPU-Beschleunigern hat Intel bereits den Codenamen sowie einige Details des Nachfolgers Rialto Bridge verraten. Die Chips sollen in bestehende OAM-Boards passen, bzw. zu diesen kompatibel sein. Allerdings sieht Intel mit Rialto Bridge eine höhere Leistungsaufnahme von bis zu 800 W vor. Dies muss dann natürlich bei einem Wechsel des Chips bedacht werden. Die volle Leistung wird Rialto Bridge also nur im OAM-V2-Format erreichen. Die Anzahl der Xe-Kerne wird auf 160 erhöht.

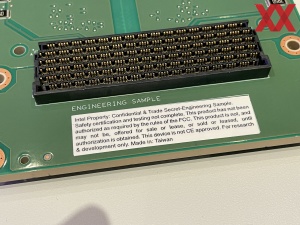

Die Datacenter-Max-Series-Beschleuniger sollen 2023 auf den Markt kommen. Wie auch bei den Sapphire-Rapids-Prozessoren testet Intel die Hardware schon seit geraumer Zeit mit einigen Partnern zusammen, so dass die Markteinführung eher als fließender Übergang zu einer breiteren Verfügbarkeit zu verstehen ist.

CPUs und GPUs werden zusammengeführt

In einem nächsten Schritt will Intel die x86-CPUs und Xe-GPUs zusammenführen. Die Falcon-Shores-XPUs können dabei nicht nur Intels x86-Kerne und Xe-GPUs verwenden, sondern per UCI ist es auch möglich andere Chiplets zu integrieren. Anfang des Jahres äußerte sich Intel erstmals zu dieser XPU-Strategie.