Werbung

Gemeinsam mit einigen Partnern (Dell, Fujitsu, IONOS, VMWare und einigen mehr) hat Intel in München auf einem Event die Einführung der vierten Xeon-Generation alias Sapphire Rapids gefeiert. Dies war zugleich auch für uns die Gelegenheit, mit Lisa Spelman zu sprechen, die Vizepräsidentin und GM der Xeon- und Speichergruppe bei Intel ist. Wir haben also ein Interview geführt, geben die Antworten an dieser Stelle aber nur inhaltlich wieder.

Bei Sapphire Rapids liegt der Fokus eindeutig auf den integrierten Beschleunigern - einerseits, weil sie bestimmte Workloads schneller verarbeiten können, andererseits aber auch, um die CPU-Kerne zu entlasten und sie für andere Aufgaben freizuhalten. Ist das eine Richtung, die sich in den nächsten Generationen fortsetzen und dann zu Falcon Shores führen wird?

Die Beschleuniger werden laut Lisa Spelman in ihrer Anwendung immer breiter angewendet, aber die Integration in den Prozessor selbst ist bei Sapphire Rapids ein großer Schritt, der vor einiger Zeit für Intel noch unvorstellbar war. Die Beschleuniger wie QAT hatten anfangs nur einen ganz spezifischen Anwendungsfall, aber inzwischen hat Intel in Zusammenarbeit mit seinen Partnern und Nutzern gesehen, dass man damit noch viel mehr machen kann. Die AI-Beschleunigung per AVX-512 (AVX-512_VNNI) war nur der Anfang und bildete die Basis. Es wird nun von Generation zu Generation bei den Xeon-Prozessoren Verbesserungen bei den Beschleunigern geben – sowohl in deren speziellen Unterstützung bestimmter Anwendungen, aber auch im Hinblick auf deren Anzahl.

Wie bestimmen Intel, welche Art von Beschleunigern für einen zukünftigen Xeon-Generationen benötigt werden?

Dazu wird Intel mit seinen Kunden sprechen und hier versuchen, eine Projektion zu erstellen. Es gibt hier natürlich das Henne-Ei-Problem, welches aber nun von einer Seite gelöst werden muss. Das Feedback der Kunden ist Intel an dieser Stelle sehr wichtig, um für die nächsten Generationen entsprechend auszulegen. AVX-512 ist an dieser Stelle ein gutes Beispiel: Anfangs verschrien und mit viel Kritik versehen, hat es sich nun zu einem Standard durchgesetzt, der immer häufiger Verwendung findet. Inzwischen baut auch AMD eine AVX-512-Pipeline in seine Architektur ein. Per VNNI wurde AVX-512 schon deutlich ausgeweitet und dies setzt sich mit AVX-512_vRAN auch fort.

Auf einem vorherigen Xeon-Event in Hillsboro bei Intel sprach Lisa Spelman über ein erweitertes Test- und Validierungsverfahren für Sapphire Rapids. Wie sehr hat sich das im Vergleich zu früheren Generationen geändert?

Natürlich wurde auch bei den vorherigen Generationen schon ausgiebig getestet und validiert. Aber die Hyperscaler sind genau wie der Gesamtmarkt in den vergangenen Jahren ebenfalls immer größer geworden und verwenden entsprechend größere und komplexere Systeme. Defects per Million (DPM) spielen mehr und mehr eine Rolle und wenn eben hunderttausende Prozessoren mit jeweils dutzenden Kernen bei Facebook, Microsoft und Co arbeiten, fallen diese Defektraten auch vermehrt auf. Vor zwei Jahren tauchten dazu erste Forschungsdaten auf, die unter anderem von Google erhoben wurden (Cores that don't count).

Eben dies wollte man mit Sapphire Rapids besser abdecken und hat dies auch getan. In Hillsboro arbeitet man daher mit vielen großen Partnern zusammen, die ihre spezifischen Workloads bereits im Vorfeld testen können. Ein Beispiel ist das Borealis-System, welches ein Testbed für das Exascale-System Aurora ist. Wir konnten das HPC-Lab von Intel besuchen und das Borealis-System begutachten. Hier wurden die Sapphire-Rapids-Prozessoren im großen Maßstab im Hinblick auf ihren Einsatz im Aurora-Supercomputer getestet. Gleiches gilt für die Ponte-Vecchio GPU-Beschleuniger. In einem nächsten Schritt sollen hier dann die Sapphire-Rapids-Prozessoren mit HBM-Speicher getestet werden, die dann auch in einer finalen Ausbaustufe im Supercomputer eingesetzt werden sollen.

Lisa Spelman war eine große Befürworterin von Optane DC Persistent Memory. Der Speicher spielte für Cascade Lake und Ice Lake eine große Rolle, jetzt wurde mit Sapphire Rapids die PMem-300-Serie eingeführt und obwohl wir wissen, dass dies die letzte Generation sein wird (Intel hat die entsprechende Sparte verkauft), könnte dies für zwei CPU-Generationen immer noch eine nützliche Ergänzung sein. Wie steht es bei der aktuellen Generation um den Optane DC Persistent Memory fragten wir uns?

Der Optane DC Persistent Memory hat seine Kunden gefunden. Diese werden ihn auch für Sapphire Rapids und Emerald Rapids in der von Intel vorgegebenen Form verwenden können. Damit ist das Thema für Intel auch abgeschlossen.

Unterstützten die Xeon-Max-Prozessoren mit HBM2e auch die PMem-300-Serie? Denn wäre die Speicherhierarchie um eine weitere Ebene (Caches, HBM2e, DDR5 und eben PMem) erweitert worden.

Nein, die Xeon-Max-CPUs unterstützen den PMem-300-Series nicht. Dies hießt aber nicht zwangsläufig auch, dass PMem mit den Speichercontrollern der Xeon Max CPUs nicht zusammenarbeitet. Intel hat dies womöglich nur nicht entsprechend validiert.

Intel hat bereits einige Einheiten an Sapphire-Rapids-Prozessoren ausgeliefert (vor dem offiziellen Start am 10. Januar), Ice Lake und Cascade Lake sind noch immer ein großer Bestandteil des Marktes - werden diese fließenden Übergänge von einer Generation zur nächsten in Zukunft häufiger vorkommen?

Alleine schon aufgrund der schieren Masse an CPUs, die durch die großen Kunden verwendet werden, wird es einen solchen fließenden Übergang auch in Zukunft weiterhin verstärkt geben. Die kurzen Produktzyklen hin zu Emerald Rapids (2023) und Granite Rapids (2024) verstärken dies natürlich auch. Die anwesenden Partner wie IONOS, die Bare-Metal-Server anbieten, bestätigen diese Ansicht.

Soweit die Erkenntnisse aus dem Gespräch mit Lisa Spelman. Intel hat uns aber auch noch weitere Informationen zur Verfügung gestellt, da auch wir nach der Vorstellung noch einige Fragen hatten.

Weitere Details zu Sapphire Rapids

Zu Sapphire Rapids haben wir von Intel auch noch weitere Details erhalten. Diese betreffen zunächst die Integration der Beschleuniger auf Hardware-Ebene. So sind die QAT, IAA, DSA und DLB als Bestandteil des Beschleuniger-Komplex in den Mesh-Interconnect eingebunden. Gegenüber der Software tauchen sie als PCI-Express- bzw. CXL-Hardware auf. Es sind allerdings Kernel-Level-Treiber notwendig, um diese anzusprechen.

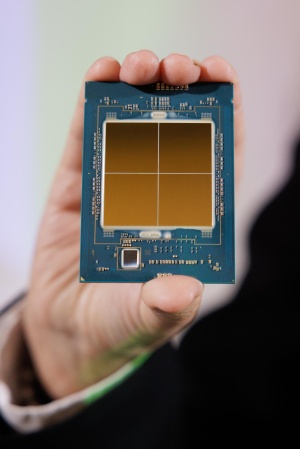

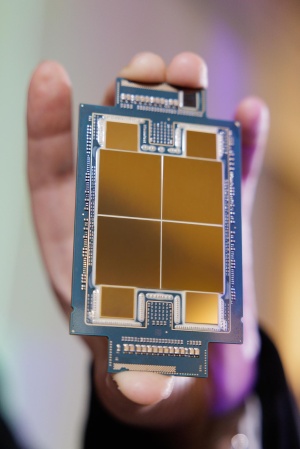

Die CPU-Kerne und die Beschleuniger haben Zugriff auf den Last Level Cache und die Speichercontroller aller Tiles – im Falle des Sapphire-Rapid-Modells mit vier Tiles.

Zudem hat Intel weitere Informationen zum Speicherbandbreite und der Latenzen preisgegeben. Der Wechsel von DDR4-3200 auf DDR5-4800 verspricht eine um 50 % höhere Bandbreite – zumindest auf dem Papier. Lese-Tests und Stream Triad zeigen eine um 45 % höhere Bandbreite, bei durchweg etwas höheren Latenzen. Kommen die Serversysteme mit DDR4 auf Latenzen von 70 bis 100 ns bis zu einer mittleren Auslastung, sind es bei Sapphire Rapids mit DDR5 Anfangs bereits 100 ns.

Diese nimmt man aber in Kauf und hat dazu den Default Page Mode zu Closed Page geändert, um die höhere Leistung zu ermöglichen, auch wenn dies negative Auswirkungen auf die Idle-Latenz hat, die um 12 bis 17 ns höher ausfallen kann. Der Einfluss des DDR5-Speichers selbst liegt bei 7 bis 12 ns. Ähnliche Angaben machte auch AMD bei den letzten EPYC-Prozessoren.

Wirft man einen Blick auf die einzelnen Modelle der Sapphire-Rapids-Prozessoren, dann haben hier bei den Taktraten der Boost- und Basis-Takt die wichtigste Rolle. Aber die Einführung der AMX-Einheiten in den Kernen hat auch Auswirkungen auf deren Takt. Mit AVX2 und AVX-512 sowie SSE gab es bei den Xeon-Prozessoren schon drei Taktstufen. Mit Sapphire Rapids sind es nun vier, denn unter Verwendung von AMX gibt es eine Basisfrequenz (AMX P1), einen All-Core-Turbo (AMX P0n) und einen Half-Core-Turbo (AMX P0half).

Die Turbo-Taktraten sind noch enger als bisher an die jeweils eingesetzten Befehle gebunden. Es gibt keine statische Zuordnung zwischen ISA und den Turbo-Taktraten. Sind nicht alle Kerne mit den aufwändigen AVX-512- und AMX-Berechnungen beschäftigt, können die Sapphire-Rapids-Prozessoren höhere Taktraten erreichen, die sonst nur unter Verwendung von SSE/AVX2 ermöglicht wurden.

Hinsichtlich der Taktfrequenzen hat Intel das Sapphire-Rapids-Design auch schneller im Wechsel der Taktstufen gemacht. Benötigt Ice Lake für den Wechsel von SSE/AVX2 auf AVX-512/AMX etwa 20 µs, sind es bei Sapphire Rapids nun nur noch etwa eine Mikrosekunde. In umgekehrter Richtung, also von einer AVX-512/AMX-Last zu SSE/AVX2 benötigte Ice Lake für den Taktwechsel eine Mikrosekunde, Sapphire Rapids hingegen erreicht dies in 2 bis 20 µs – ist also um Größenordnungen schneller. Dies soll sich natürlich auf die Leistung und die Effizienz positiv auswirken.