Werbung

Bereits vor gut einem Jahr tauchte der Begriff "Adamantine" im Zusammenhang mit Intels kommender Meteor-Lake-Generation erstmals auf. Damals war noch nicht ganz klar, worum es sich genau handelt. In den vergangenen Tagen hat es aber einige Informationskrümel und größere Brocken gegeben, sodass wir nun schon ein deutlich klareres Bild haben.

Der Codename Adamantine (oder kurz ADM) ist inzwischen klar einem L4-Cache zuzuordnen, der mit Meteor Lake sein Comeback feiern soll. Ein Codeschnipsel und die dazugehörige Beschreibung in einem Kernel Driver Patch zur integrierten Grafikeinheit gaben den finalen Hinweis:

"On MTL, GT can no longer allocate on LLC - only the CPU can. This, along with addition of support for ADM/L4 cache calls a MOCS/PAT table update."

Einen L4-Cache haben wir nun aber schon länger nicht mehr gesehen. Aktuell setzen AMD und Intel auf immer größere L2- und L3-Caches bzw. packen schnellen HBM in das CPU-Package. Einigen dürften die Intel Core-Prozessoren der Haswell-Generation mit Iris Pro Graphics noch ein Begriff sein, die einen 128 MB großen eDRAM als L4-Cache hatten. Ansonsten sind L4-Caches eher auf Server-Prozessoren wie dem Itanium 2 oder den aktuellen IBM-Power-CPUs zu finden.

Ein schon zwei Jahre altes Patent, welches von Intel eingereicht wurde, vervollständigt das Bild um den Adamantine/L4-Cache nun (via Videocardz).

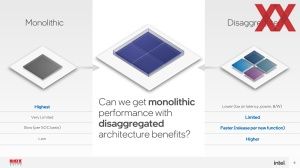

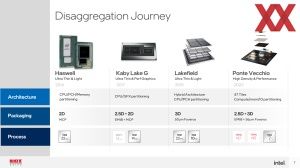

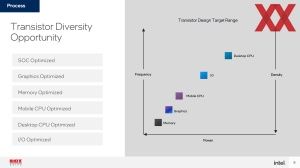

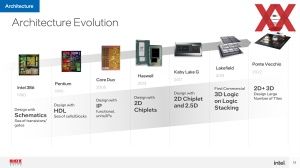

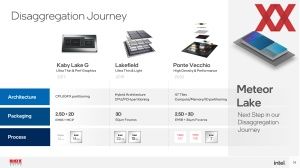

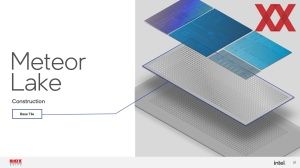

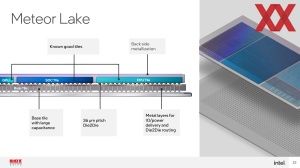

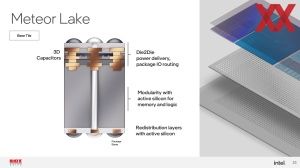

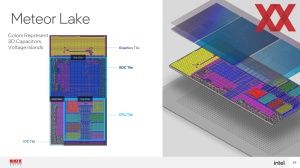

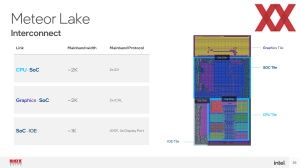

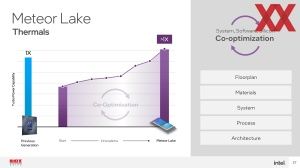

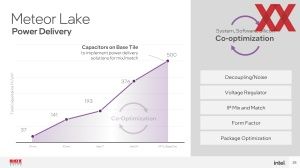

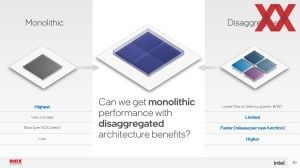

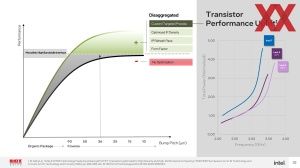

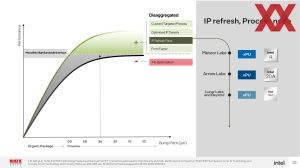

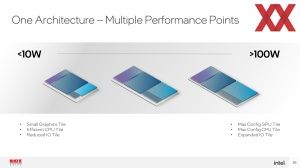

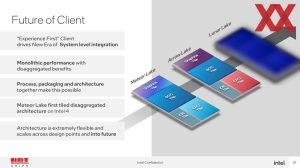

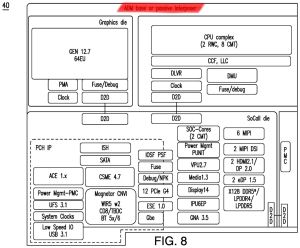

Demnach handelt es sich um einen L4-Cache, der im Base Tile der Meteor-Lake-Prozessoren untergebracht ist. Meteor Lake wird als erster Client-Prozessor mehrere Tiles verwenden. Auf der HotChips 34 gab Intel bereits eine Vorschau auf diese Umsetzung. Für die einzelnen Tiles wird man auf unterschiedliche Fertigungsgrößen setzen. Dies soll einerseits für eine gewisse Flexibilität in der Umsetzung der Prozessoren sorgen, da gewisse Anpassungen an den Tiles bzw. unterschiedliche Zusammenstellungen gemacht werden können und andererseits kann man hinsichtlich der Fertigung den Prozess einsetzen, der die besten Aussichten hat für eben diesen Zweck zu funktionieren. Den aktuellen Gerüchten zufolge teilt Intel dies für Meteor Lake wie folgt auf:

- Compute Tile (mit den CPU-Kernen:): Intel 4

- GPU Tile: TSMC N5

- SoC Tile: TSMC N6

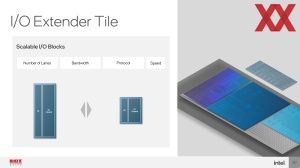

- I/O Tile: TSMCN6

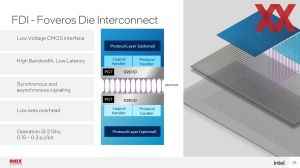

- Base Tile (mit Foveros-Interconnect): Intel 22FFL

Der Base Tile ist im Zusammenhang mit dem L4-Cache nun interessant, da dieser in diesem Base Tile untergebracht sein soll. Für die Datacenter-GPU Ponte Vecchio verwendet Intel ebenfalls einen Base Tile, der 144 MB an L3-Cache enthält. Das Konzept in dieser Ebene des Packages auch schon einen Cache unterzubringen ist also nicht neu.

Welchem Zweck der L4-Cache dienen soll, darüber soll ein Text Auskunft geben, der ebenfalls Bestandteil des Patents ist, der aber recht allgemein gehalten ist und in vielerlei Richtung interpretiert werden kann.

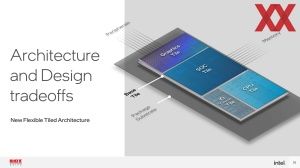

Das oben gezeigte Schaubild verdeutlicht den Aufbau dann noch einmal: Der Base Tile sitzt unter den weiteren Tiles und stellt auch die Verbindungen für das Die-to-Die-Interface bereit. Darauf sitzen die Compute, GPU, I/O und SoC Tiles.

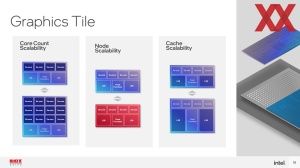

Die Schaubilder im Patent legen nahe, dass ein Compute Tile zwei Redwood-Cove- (RWC) und acht Crestmont-Kerne (CMT) verwenden wird. Zwei weitere Crestmont-Kerne befinden sich offenbar im SoC Tile. Entsprechende Gerüchte zu weiteren Low-Power-Efficiency-Kernen gab in der Vergangenheit bereits.

Wie groß der L4-Cache ist, darüber gibt es noch keinerlei gesicherte Informationen. Gerüchten zufolge soll Intel die Chips aktuell mit 128 bis 512 MB testen. Die Fertigung der Compute Tiles soll bei Intel in Intel 4 bereits angelaufen sein. Dies heißt aber noch nicht, dass man die produktionsreife Massenproduktion des gesamten Package bereits gestartet hat. Mit einer Vorstellung ist womöglich noch Ende 2023 zu rechnen.

Update:

Nicht wirklich mit dem Thema L4-Cache verbunden, aber Teil der aktuellen Entwicklung ist ein Design-Werkzeug, welches Intel im Rahmen seiner Design Tools anbietet. Das "LGA1851-MTL-S Interposer for the Gen5 VR Test Tool" kann im VR Test Tool Base Kit verwendet werden und hilft dabei die Plattform hinsichtlich ihrer Spannungsversorgung zu testen. Darauf gestoßen ist Twitter-Nutzer @momomo_us.

Der Sockel LGA1851 gilt für Meteor Lake aber schon länger als gesetzt. Dieser soll auch für Lunar Lake zum Einsatz kommen.