Werbung

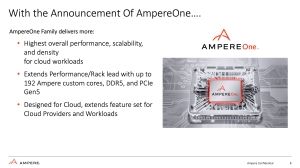

Auf bis zu 128 Kerne folgen nun 136 bis 192, denn Ampere Computing hat mit dem AmpereOne die nächste Prozessor-Generation angekündigt, die für Cloud-Systeme mit einer weiter verbesserten Effizienz auszeichnen sollen. Die Altra- und Altra-Max-Serie basierte auf der gleichen Plattform und erstreckten sich von 30 bis 128 Kerne.

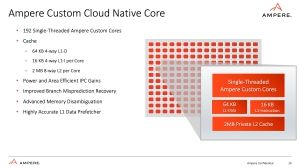

Neben der höheren Anzahl an Kernen besitzt die AmpereOne-Serie auch eine neu Mikro-Architektur. Es kommt nicht mehr länger das Neoverse-Referenzdesign von ARM zum Einsatz, sondern Ampere hat eine ein Custom-Design entworfen, welches allerdings noch immer die Arm ISA verwendet. Ein SMT wird nicht unterstützt. Jeder Kern kann einen Thread verarbeiten.

Der L2-Cache pro Kern wird von 1 auf 2 MB verdoppelt. Anstatt wie bisher acht DDR4-Kanäle kommt nun DDR5 zum Einsatz. Die 128 PCI-Express-Lanes basieren nun auf den 5.0-Standard und verdoppeln damit die zur Verfügung stehende Bandbreite. Mit einer höheren Kernanzahl und schnelleren I/O-Standards steigt allerdings auch die Leistungsaufnahme. Von bisher maximal 180 W geht es nun rauf auf 200 bis 350 W.

Änderungen gibt es allerdings auf der L1-Cache-Ebene: Das Altra-Design verfügte über 64 KB L1-I-Cache und 64 KB L1-D-Cache. Im von Ampere Computing "Syrin" getauften Design sind es zwar weiterhin 64 KB am L1-D-Cache, aber nur noch 16 KB an L1-I-Cache.

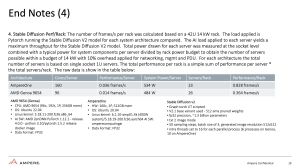

| Altra | Altra Max | AmpereOne | |

| Sockel | FCLGA4926 | FCLGA4926 | FCLGA5964 |

| Fertigung | 7 nm | 7 nm | 5 nm |

| Kerne | 32 bis 80 | 96 bis 128 | 136 bis 192 |

| Mesh-Takt | 1,1 bis 1,8 GHz | 2 GHz | - |

| TDP | bis zu 250 W | bis zu 250 W | bis zu 350 W |

| L2-Cache | 1 MB pro Kern | 1 MB pro Kern | 2 MB pro Kern |

| System Level Cache | 32 MB | 16 MB | - |

| Arbeitsspeicher | 8x DDR4 | 8x DDR4 | 8x DDR5 |

| PCI-Express-Lanes | 128x PCI-Express 4.0 | 128x PCI-Express 4.0 | 128x PCI-Express 5.0 |

| CCIX | 4 x16 CCIX-Lanes | 4 x16 CCIX-Lanes | - |

Aktuell macht Ampere Computing noch keinerlei Angaben zum Takt der Kerne oder des Mesh. Die IPC-Leistung soll aber massiv gesteigert worden sein, sodass es auch ohne eine große Steigerung des Taktes zu einem Leistungsplus kommen soll.

Ampere Computing lässt den AmpereOne in 5 nm in einem Chiplet-Design fertigen. Bisher wurde die 7-nm-Fertigung, ebenfalls von TSMC, verwendet. Das Package besteht aus einem Compute-Chiplet mit den CPU-Kernen, sowie aus I/O-Dies, welche die DDR- und PCI-Express-Controller beinhalten. Auch diese werden in 5 nm gefertigt. ARMs AMBA-CHI-Interconnect-Technik kommt zum Einsatz um die Chiplets miteinander zu verbinden.

Für den Sockel findet ein Wechsel von FCLGA4926 auf FCLGA5964 statt. Mehr I/O bzw. der Wechsel von DDR5 und PCI-Express 5.0 verlangt nach mehr Pins. Auch die höhere Leistungsaufnahme dürfte hier eine Rolle spielen.

Ein Fotos des Prozessors gibt es nur aus dem Video der Präsentation und wir konnten nur eine stark hereingezoomte Version erstellen, die recht unscharf ist. Das Chiplet-Design ist darauf nicht zu erkennen, da sich ein strukturelles Silizium über allen Chiplet befindet. Dieses bietet einerseits Schutz für die empfindlichen Chips und unterstützt auch dabei die Abwärme zu verteilen. Anstatt eines Heatspreaders wie bisher, wird der AmpereOne per Direct-Die-Kühlung versorgt.

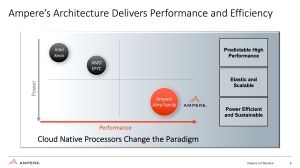

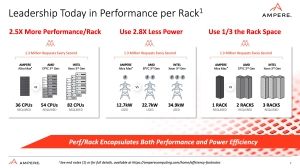

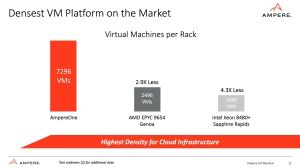

Ampere Computing sieht den AmpereOne genaue wie seine Altra-Vorgänger vor allem im Cloud-Computing bzw. im VM-Angebot deutlich vor der Konkurrenz. Zwar ist es natürlich auch hier möglich jeder VM eine vCPU zuzuordnen, die auch nur ein Thread eines CPU-Kerns sein kann, dann aber müssen sich diese die Ressourcen des Kerns teilen, während beim AmpereOne zum Beispiel 2 MB an L2-Cache jedem Kern exklusive zur Verfügung stehen. Mit 192 Kernen pro Prozessor und mit 2S-Systemen bestückt steigt die Anzahl der VMs pro Rack natürlich deutlich.

Aber auch in der AI-Rechenleistung will Ampere Computing nun einen großen Sprung machen und zumindest mit den Prozessoren der Konkurrenz mithalten bzw. diese deutlich dominieren können. Ampere Computing bewirbt vor allem die Unterstützung von Bfloat16, wenngleich dies auch bei Intel möglich ist und eine Format-Änderung, wie sie bei AMD notwendig wäre (von FP16 in Bfloat16), kein besonders großer Nachteil wäre. Was die Leistung betrifft wird der AmpereOne in unabhängigen Tests noch beweisen müssen, wie gut er wirklich ist. Die deutlich gestiegene Leistungsaufnahme wird in der Beurteilung dessen zudem noch ein Faktor sein.

Die Gegenspieler des AmpereOne werden die EPYC-Prozessoren auf Basis des Bergamo-Designs mit abgespeckten Zen-4c-Kernen sein. Im kommenden Jahr wird Intel mit Sierra Forrest ebenfalls Serverprozessoren anbieten, die ausschließlich Efficiency-Kerne verwenden. Wir erwarten auch noch weitere Details zu den AmpereOne-Prozessoren – Taktraten, die einzelnen Modellinformationen und vor allem zur Verfügbarkeit.