Werbung

Intel bereitet sich auf die nächsten Prozessor-Generationen vor und wird mit diesen auch neue Instruktionen einführen. Eine Motivation dahinter ist natürlich, dass man die Funktionen des Prozessors an die zukünftigen Anforderungen anpassen möchte. Auch wird es darum gehen, die zur Verfügung stehenden Ressourcen besser nutzen zu können. Im Hinblick auf die kommenden CPU-Generationen mit der Unterscheidung in Performance-Core (Granite Rapids) und Efficiency-Core (Sierra Forrest) gilt es aber auch den Funktionsumfang möglichst identisch zu halten und eine gewisse Parität zu gewährleisten.

Gleich vier Dokumente APX (Advanced Performance Extensions), AVX10 (Advanced Vector Extensions) und der Converged Vector ISA hat Intel veröffentlicht.

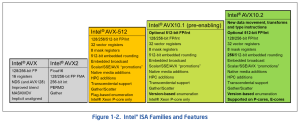

Die bestehenden AVX-512-Befehlssätze werden eingefroren als mittels Legacy-Support weiterhin unterstützt. Dies gilt aber nur für die Prozessoren mit Performance-Kernen. AVX10 räumt hier auf und stellt einen Neustart dar. Als AVX10.2 werden dann sowohl die P- als auch die E-Kerne die Befehlssätze vollständig unterstützen.

Die aktuellen AVX-512-Befehlssätze sind ein wichtiges Werkzeug, um mehr aus den Funktionseinheiten der Prozessorkerne herauszuholen. Allerdings sind diese über die vergangenen Jahre immer weiter aufgebläht worden und Intel hat zudem das Problem, dass diese nicht im vollem Umfang von den Efficiency-Kernen unterstützt werden. Spielt dies auf dem Desktop bzw. im mobilen Bereich noch keine große Rolle, wird das zukünftige Angebot an Xeon-Prozessoren mit P- oder E-Kernen dahingehend für die Softwareunterstützung problematisch werden. Eben diesen Umstand geht Intel mit AVX10 an.

Intel AVX10 Version 1 will be introduced for early software enablement and supports the subset of all the Intel AVX- 512 instruction set available as of future Intel Xeon processors with P-cores, codenamed Granite Rapids, that is forward compatible to Intel AVX10. This version will not include the new 256-bit vector instructions supporting embedded rounding or any of the new instructions and will serve as the transition base version from Intel AVX-512 to Intel AVX10.

Intel AVX10 Version 2 will include the 256-bit instruction forms supporting embedded rounding as well as a suite of new Intel AVX10 instructions covering new AI data types and conversions, data movement optimizations, and standards support. All new instructions will be supported at 128-, 256-, and 512-bit vector lengths with limited variances. All Intel AVX10 versions will implement the new versioning enumeration scheme.

Die Advanced Performance Extensions (APX) verdoppelt die Anzahl der GP-Register (General Purpose) von 16 auf 32. Mit APX kompilierter Code soll 10 % weniger Loads und 20 % weniger Stores veranlassen, was letztendlich dafür sorgt, dass der entsprechende APX-Code effizienter ausgeführt wird. Ein einfacher Re-Compile soll ausreichend sein, damit alter Code per APX effizienter wird.

Softwareentwickler sollen sich nun auf AVX10 und APX vorbereiten können. Mit der Markteinführung der zukünftigen Prozessoren soll die Software dann bereit für diese neue Hardware sein.

Im Frühjahr bestärkte Intel noch einmal seine Pläne rund um die Xeon-Prozessoren. In der ersten Jahreshälfte 2024 sollen mit Sierra Forest die ersten E-Core-Xeons auf den Markt kommen. Kurz darauf wird Granite Rapids als P-Core-Xeon folgen. Beide teilen sich die gleiche Plattform.