Werbung

Oft unter dem Radar, aber ein wichtiger Bestandteil in der Produktpalette bei Intel sind die FPGAs. Unter anderem kommen diese auf Intels eigenen SmartNIC und IPUs zum Einsatz, die Anwendungsbereiche für den Einsatz von FPGAs sind vielfältig. Zuletzt konnten wir uns beim Besuch von Intel in Malaysia davon einen Eindruck verschaffen, denn für die eigene Test- und Verification-Hardware setzt Intel tausende der eigenen FPGAs ein.

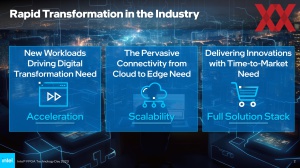

FPGAs werden häufig dort eingesetzt, wo es sich nicht lohnt, ein eigenes Chip-Design zu entwickeln und fertigen zu lassen. Es gibt aber auch Anwendungsbereiche, in denen die Flexibilität der FPGAs, deren Effizienz oder deren Aufbau (geringe Latenzen) eine wichtige Rolle spielen. FPGAs können in ihrer Programmierung auch nachträglich in ihrer Funktion verändert werden, was in dieser Form bei einem "fest verdrahteten" Silizium-Chip nicht mehr möglich ist. Chipentwickler simulieren komplette Mikroarchitekturen auf gleich mehreren FPGAs, um das Design zu prüfen.

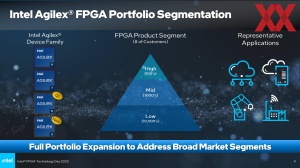

Jedoch sind FPGAs meist recht teuer, vor allem wenn sie eine gewisse Komplexität erreichen. Dem will Intel nun mit einer Erweiterung der Agilex-Serie Rechnung tragen. Die Agilex-5-Serie, bzw. erste Samples wurden bereits für das vierte Quartal angekündigt. Eine Agilex-3-Serie setzt diesen Ansatz fort. Ziel ist es, die Anzahl der möglichen Kunden zu erweitern, in dem die Kosten für die FPGAs reduziert werden.

Sowohl die Agilex-3- als auch die Agilex-5-Serie kommen erst 2024 in großen Stückzahlen. Daneben wird es die ersten Agilex-7-FPGAs geben, die zu den kommenden Serverplattformen mit CXL 2.0 kompatibel sind. Für die Nische in der Nische sieht Intel die Nios-V-Prozessoren vor, die mit RISC-V-Kernen ausgestattet sind, die vorerst per FPGA simuliert werden. Die F2000-IPU-Plattform soll im Bereich der SmartNICs, bzw. Infrastructure Processing Units (IPUs) eingeführt werden.

Auch wenn die FPGAs eine vergleichsweise kleine Rolle im Datacenter-Geschäft von Intel spielen, ihre Bedeutung soll zunehmen, auch weil über die für die Entwicklung notwendigen Werkzeuge, die Fertigung selbst und auch das Packaging alles in Intels eigener Hand liegt und man sich so im Falle von Problemen in der Lieferkette im Vorteil sieht.

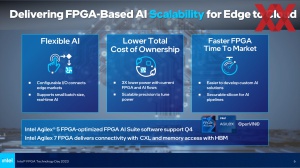

Einen großen Wachstumsbereich sieht Intel – wenig überraschend – im AI-Computing. Das Training findet auf den GPUs und Beschleunigern in Rechenzentren statt, ein schnelles Inferencing auf den eigenen Xeon-Prozessoren, im Edge-Segment allerdings sieht man die FPGAs als ideale Lösung – vor allem wegen der hohen Effizienz.

Ein Baustein in Intels FPGA-Strategie, der bereits angewendet wird, ist eine Chiplet-Strategie. Mittels EMIB werden bereits verschiedene IP-Blöcke miteinander zu einem FPGA verbunden. Ein potentieller Kunde wählt die IP-Blöcke und Bestandteile und Intel fertigt daraus den gewünschten FPGA. Intel bekommt die Chiplets aus den verschiedenen Fertigungsbereichen und fügt sie dann zusammen. Die Durchlaufzeit für einen FPGA soll laut Intel nur noch wenige Wochen betragen, da Intel alles aus eigener Hand anbieten kann.

Auch wenn das FPGA-Geschäft bei Intel im Vergleich zu den anderen Geschäftsbereichen also etwas unter dem Radar läuft, so sieht man hier ein großes Wachstumspotential und will sich potentiellen Kunden als zuverlässiger und flexibler Partner präsentieren – vom Software-Stack zur Entwicklung bis zur Fertigung und dem Packaging.