Werbung

Auf der Keynote der Innovation 2023 verkündete Intels CEO Pat Gelsinger, dass die fünfte Xeon-Scalable-Generation alias Emerald Rapids am 14. Dezember erscheinen wird. Emerald Rapids ist Sockel-kompatibel zur aktuellen Sapphire-Rapids-Generation, hat aber offenbar einige entscheidende Unterschiede aufzuweisen. Bereits seit Monaten spricht Intel davon, dass Emerald Rapids mehr Kerne bei gleichem Verbrauch vorzuweisen hat, aber weiterhin in Intel 7 gefertigt wird. Auf der Innovation gab es einige weitere Details.

So soll der LLC (Last Level Cache) bzw. L3-Cache um den Faktor drei größer ausfallen. Bei Sapphire Rapids verfügen die Modelle mit vier Tiles über 105 MB an L3-Cache. Emerald Rapids sollte daher auf mindestens 300 MB kommen. Allerdings sollen nicht alle Modelle über einen derart großen L3-Cache verfügen.

Zur höheren Anzahl an Kernen kommen wir später noch. Darüber hinaus spricht Intel von der Unterstützung von CXL Type 3, was dann auch bedeutet, dass deutlich mehr CXL-Hardware auf den Markt kommen wird, die dann auch letztendlich verwendet wird. In den ersten CXL-Umsetzung waren zu viele Einschränkungen vorhanden, als das die Technik eine größere Verbreitung hätte finden können.

Darüber hinaus ist von einer höheren Speichergeschwindigkeit die Rede. Sapphire Rapids legt bei DDR5-4800 los. Emerald Rapids sollte mit DDR5-5600 an den Start gehen. Zum Thema Speichergeschwindigkeit wollen wir an dieser Stelle noch zu einem Bericht zu MCR-DIMMs verweisen, denn auch zu diesem Thema hat die Innovation einiges zu bieten.

Ein großer Fokus für Emerald Rapids dürften einmal mehr die integrierten Beschleuniger werden. Diese spielten auch schon bei Sapphire Rapids eine große Rolle.

Emerald Rapids: Aufbau des Packages

Im Rahmen der Keynote und und auch in einer technischen Session ließ sich Intel aber noch ein paar weitere Details entlocken.

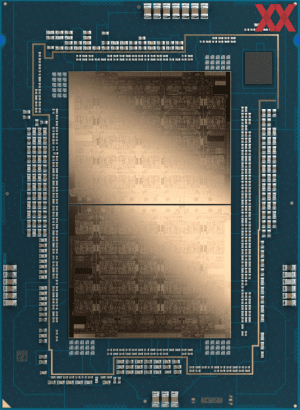

Bereits bekannt ist, dass Emerald Rapids aus zwei Chips bestehen wird, die per EMIB miteinander verbunden sind. Die Strategie dahinter ist die Folgende: Während es für Sapphire Rapids noch zwei Chip-Konfigurationen gab, viermal XCC (Extreme Core Count) für bis zu 60 Kerne und einmal ein MCC-Die (Medium Core Count) für bis zu 32 Kerne, setzt Emerald Rapids auf zwei MCC-Dies mit den Raptor-Cove-Kernen.

Aus der gezeigten Illustration lässt sich womöglich auch die Anzahl der Kerne bestimmen. Wir kommen auf 33 Kerne, von denen jeweils 32 aktiv sein sollten. In der größten Ausbaustufe käme Emerald Rapids somit auf 64 Kerne.

Zum Start von Emerald Rapids wird sicherlich noch weitere Details enthüllen. Vor allem der größere L3-Cache lässt die Frage offen, wie Intel 32 Kerne, in Intel 7 gefertigt, zusammen mit dem großen Cache unterbringt.